# David Ilsen

# Algebraic and Combinatorial Algorithms for Translinear Network Synthesis

Vom Fachbereich Mathematik der Universität Kaiserslautern zur Verleihung des akademischen Grades Doktor der Naturwissenschaften (Doctor rerum naturalium, Dr. rer. nat.) genehmigte Dissertation

1. Gutachter: Prof. Dr. G.-M. Greuel

2. Gutachter: Dr. W. A. Serdijn

Vollzug der Promotion: 19. Mai 2006

D 386

# Contents

| 1. | Intro                                               | oductio  | on                                      | 4       |  |  |  |

|----|-----------------------------------------------------|----------|-----------------------------------------|---------|--|--|--|

| 2. | Prerequisites 2.1. Notions from Graph Theory        |          |                                         |         |  |  |  |

|    |                                                     |          | oric Ideal of a Digraph                 | 7<br>10 |  |  |  |

| 3. | Trar                                                | nslinear | Network Theory                          | 13      |  |  |  |

|    | 3.1.                                                | The T    | ranslinear Principle                    | 13      |  |  |  |

|    |                                                     | 3.1.1.   | The Static Translinear Principle        | 14      |  |  |  |

|    |                                                     | 3.1.2.   | Motivation for a Catalog of Topologies  | 17      |  |  |  |

|    |                                                     | 3.1.3.   | The Dynamic Translinear Principle       | 18      |  |  |  |

|    | 3.2.                                                | Transl   | inear Decomposition of Polynomials      | 20      |  |  |  |

|    | 3.3.                                                | The Te   | opology of Translinear Networks         | 22      |  |  |  |

|    |                                                     | 3.3.1.   | Translinear Digraphs                    | 22      |  |  |  |

|    |                                                     | 3.3.2.   | Connection of Collectors                | 26      |  |  |  |

|    |                                                     | 3.3.3.   | Insertion of Capacitances               | 28      |  |  |  |

|    | 3.4.                                                | The In   | nterface of a Translinear Network       | 28      |  |  |  |

|    |                                                     | 3.4.1.   | Outputs                                 | 28      |  |  |  |

|    |                                                     | 3.4.2.   | Inputs and Ground Node Selection        | 29      |  |  |  |

|    | 3.5.                                                | Topolo   | ogies for 4-terminal MOS transistors    | 30      |  |  |  |

| 4. | Combinatorial Generation of Translinear Networks 32 |          |                                         |         |  |  |  |

|    | 4.1.                                                | Orderl   | y Generation                            | 32      |  |  |  |

|    |                                                     | 4.1.1.   | Cataloging Problems                     | 32      |  |  |  |

|    |                                                     | 4.1.2.   | Canonicity and Augmentation             | 35      |  |  |  |

|    |                                                     | 4.1.3.   | Generation of Canonical Words           | 37      |  |  |  |

|    | 4.2.                                                | Genera   | ation of Digraphs                       | 40      |  |  |  |

|    | 4.3.                                                | Genera   | ation of Translinear Digraphs           | 44      |  |  |  |

|    |                                                     | 4.3.1.   | Adjacency matrices of layer digraphs    | 44      |  |  |  |

|    |                                                     | 4.3.2.   | Canonicity                              | 45      |  |  |  |

|    |                                                     | 4.3.3.   | Augmentation                            | 46      |  |  |  |

|    |                                                     | 4.3.4.   | Specialization for Translinear Digraphs | 47      |  |  |  |

|    | 4.4.                                                | Genera   | ation of Collector Assignments          | 48      |  |  |  |

|    | 4.5.                                                | Catalo   | oging Formal Networks                   | 49      |  |  |  |

# Contents

| 5. | A Catalog of Topologies as a Synthesis Tool                                         |       | 52                                           |

|----|-------------------------------------------------------------------------------------|-------|----------------------------------------------|

|    | 5.1. Translinear Network Equations                                                  |       | 52                                           |

|    | 5.1.1. Translinear Loop Equations                                                   | <br>• | 53                                           |

|    | 5.1.2. Node Equations                                                               |       | 53                                           |

|    | 5.1.3. The Network Ideal                                                            |       | 53                                           |

|    | 5.1.4. Elimination of Collector Currents                                            | <br>• | 54                                           |

|    | 5.2. The Input Matrix                                                               |       | 55                                           |

|    | 5.3. Solution of the Matching Problem                                               |       | 57                                           |

|    | 5.4. Final Network Check                                                            |       | 58                                           |

|    | 5.4.1. Positivity Check of Collector Currents                                       |       | 58                                           |

|    | 5.4.2. Output Function Check                                                        |       | 59                                           |

| 6. | Example Application                                                                 |       | 60                                           |

| 7. | Conclusion                                                                          |       | 64                                           |

|    |                                                                                     |       |                                              |

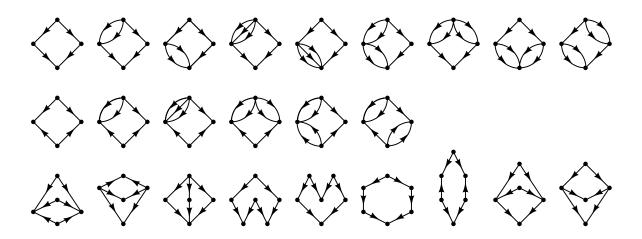

| Α. | . The Static Formal Translinear Networks with up to 6 Transistors                   |       | 66                                           |

|    | . The Static Formal Translinear Networks with up to 6 Transistors . Implementations |       | 66<br>69                                     |

|    | . Implementations                                                                   |       |                                              |

|    | ·                                                                                   |       | 69                                           |

|    | . Implementations B.1. Overview of the Implementations                              |       | <b>69</b>                                    |

|    | . Implementations B.1. Overview of the Implementations                              | <br>  | <b>69</b><br>69<br>71                        |

|    | . Implementations B.1. Overview of the Implementations                              | <br>  | <b>69</b> 71 71                              |

|    | . Implementations  B.1. Overview of the Implementations                             | <br>  | 69<br>71<br>71<br>72                         |

|    | . Implementations  B.1. Overview of the Implementations                             | <br>  | 69<br>71<br>71<br>72<br>73                   |

|    | . Implementations  B.1. Overview of the Implementations                             | <br>  | 69<br>71<br>71<br>72<br>73<br>74             |

|    | . Implementations  B.1. Overview of the Implementations                             | <br>  | 69<br>71<br>71<br>72<br>73<br>74<br>75       |

|    | . Implementations  B.1. Overview of the Implementations                             | <br>  | 69<br>71<br>71<br>72<br>73<br>74<br>75<br>77 |

# 1. Introduction

This thesis contains the mathematical treatment of a special class of analog microelectronic circuits called *translinear circuits*. The goal is to provide foundations of a new coherent synthesis approach for this class of circuits. The mathematical methods of the suggested synthesis approach come from graph theory, combinatorics, and from algebraic geometry, in particular symbolic methods from computer algebra.

Translinear circuits [Gil75, Gil96] form a very special class of analog circuits, because they rely on nonlinear device models, but still allow a very structured approach to network<sup>1</sup> analysis and synthesis. Thus, translinear circuits play the role of a bridge between the "unknown space" of nonlinear circuit theory and the very well exploited domain of linear circuit theory.

The nonlinear equations describing the behavior of translinear circuits possess a strong algebraic structure that is nonetheless flexible enough for a wide range of nonlinear functionality. Furthermore, translinear circuits offer several technical advantages like high functional density, low supply voltage and insensitivity to temperature.

This unique profile is the reason that several authors consider translinear networks as the key to systematic synthesis methods for nonlinear circuits [DRVRV99, RVDRHV95, Ser05].<sup>2</sup>

This thesis proposes the usage of a computer-generated catalog of translinear network topologies as a synthesis tool. The idea to compile such a catalog has grown from the observation that on the one hand, the topology of a translinear network must satisfy strong constraints which severely limit the number of "admissible" topologies, in particular for networks with few transistors, and on the other hand, the topology of a translinear network already fixes its essential behavior, at least for static networks, because the so-called *translinear principle* requires the continuous parameters of all transistors to be the same.

Even though the admissible topologies are heavily restricted, it is of course a highly nontrivial task to compile such a catalog. Combinatorial techniques have been adapted to undertake this task.

The idea to utilize synthetic lists of network topologies is not new in analog circuit design: Catalogs of VCCS topologies are used for CMOS circuit design by E. Klumperink and others [Klu97, KBN01, Sch02, Sch04].

<sup>&</sup>lt;sup>1</sup>In this thesis, a "circuit" means electronics hardware, whereas a "network" means its mathematical model.

<sup>&</sup>lt;sup>2</sup>The "Wiley Encyclopedia of Electrical and Electronics Engineering" expresses the prominent role of translinear circuits by the fact that the entire entry for "nonlinear circuits" consists only of a reference to "translinear circuits".

#### 1. Introduction

In a catalog of translinear network topologies, prototype network equations can be stored along with each topology. When a circuit with a specified behavior is to be designed, one can search the catalog for a network whose equations can be matched with the desired behavior.

In this context, two algebraic problems arise: To set up a meaningful equation for a network in the catalog, an elimination of variables must be performed, and to test whether a prototype equation from the catalog and a specified equation of desired behavior can be "matched", a complex system of polynomial equations must be solved, where the solutions are restricted to a finite set of integers. Sophisticated algorithms from computer algebra are applied in both cases to perform the symbolic computations.

All mentioned algorithmic methods have been implemented and successfully applied to actual design problems at Analog Microelectronics GmbH (in the following: AMG), Mainz.

The thesis is organized as follows:

Chapter 2 collects some graph-theoretic and algebraic background that will be needed in the other chapters.

Chapter 3 first reviews the basic concepts and facts about translinear circuits, then gives an analysis of their topology and develops some abstract notions to model the topology in terms of graph theory.

Chapter 4 is about techniques for producing catalogs of combinatorial objects and the specialization of these techniques to list translinear network topologies exhaustively for a given number of transistors.

The concerns of Chapter 5 are the structure of the equations describing a translinear network's behavior, and the algebraic problems which have to be solved when the network catalog is to be equipped with prototype network equations and when it is searched for a network with a particular behavior.

Chapter 6 reports about the successful application of the developed synthesis methodology in the design of a new humidity sensor system of AMG.

As an impression of the catalog of networks that is produced, an overview over the static formal translinear networks with 6 or less transistors is given in Appendix A.

The algorithms presented in this thesis for building and searching a catalog of translinear network topologies have been implemented using C++, SINGULAR, and MATHEMATICA. Some details and comments of the implementations are included in Appendix B.

# Acknowledgements

My first thanks go to my advisor Prof. Dr. Gert-Martin Greuel. His advice was of excellent scientific and personal quality.

The collaboration with Analog Microelectronics GmbH was essential for my research. I am very much indebted to development engineer Ernst Josef Roebbers for the initiation of the research topic, and for plenty of discussions about my work and its applications. Thanks are also due to managing director Dr. N. Rauch for supplementary explanations and for making the collaboration possible.

I thank Dr. Wouter Serdijn for his helpful comments, in particular for inspiring the topological considerations for MOS translinear circuits.

Further, I thank Prof. Dr. Gerhard Pfister for several discussions, and the AnalogInsydes team at Fraunhofer-ITWM for the frequent meetings at which they shared their circuit analysis experience with me.

I am grateful for the honor to receive a scholarship of the DFG-Graduiertenkolleg "Mathematik und Praxis" in Kaiserslautern, which provided the financial support for my research.

For last-minute proofreading, I thank Britta Späth, Alexander Dreyer, Hannah Markwig, Burkhard Ilsen, and Dr. K. Mann.

Music kept my spirits alive when math was too frustrating. Thanks go to my friends from "Haste Töne".

Without the moral support from Kerstin and from all of my parents, I wouldn't have been able to complete this thesis. Thanks.

I dedicate my work to the remembrance of Magdalene Ilsen, my wonderful "fabulous grandmother", who died on August 28th, 2005. She has a great part in my personal development, not least by her accompaniment of my first steps as a mathematician in Dortmund.

Muja, ich danke Dir für all die Kraft und Wärme und werde sie immer in meinem Herzen behalten!

# 2. Prerequisites

For the algebraic notions used in this thesis, we refer to textbooks, e.g. [CLO97, FS83, Lan94, GP02]. For some of the notions we need from Graph Theory, the literature shows subtle inconsistencies, so we clarify these notions in Section 2.1. Section 2.2 collects some nonstandard constructions and facts about toric ideals, which will be needed in Chapter 5.

# 2.1. Notions from Graph Theory

**Definition 2.1.** A directed graph or digraph is a triple  $G = (V, E, \iota)$  of two sets V and E and a map  $\iota : E \to V \times V$ . The elements of V are called **nodes** or **vertices**, the elements of E are called **branches**.  $\iota$  is called the **incidence map** of E. For a branch E with E with E is called its **tail node** or **start vertex** and also denoted by E tail E and E is called the **head node** or **terminal vertex** of E and also denoted by E head E is called the **head node** or **terminal vertex** of E and also denoted by E head E is called the **head node** or **terminal vertex** of E and also denoted by E head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and also denoted by head E is called the **head node** or **terminal vertex** of E and E is the node of the head E is the head E is the node of the head E is the head E is the node of the head E is the head E

Remark 2.2. Definition 2.1 allows **parallel branches** and **self-loops** in a digraph. (A pair of parallel branches consists of distinct elements  $e, e' \in E$  with  $\iota(e) = \iota(e')$ ; a self-loop is a branch  $e \in E$  with tail(e) = head(e).) Authors in graph theory frequently exclude both in digraphs. If parallel branches or self-loops occur, they rather speak of a directed multigraph. Here, we deliberately chose Definition 2.1 to be as it is.

**Definition 2.3.** A digraph  $G = (V, E, \iota)$  is called **finite** if both V and E are finite sets.

Remark 2.4. In all examples of this thesis, digraphs are finite.

If G is a directed graph, its set of nodes will also be denoted by V(G), and its set of branches will also be denoted by E(G).

**Definition 2.5.** A walk in a digraph G is an alternating finite sequence

$$W = (v_0, e_1, v_1, \dots, e_{l-1}, v_{l-1}, e_l, v_l)$$

of nodes and branches such that for each j = 1, ..., l, either  $\iota(e_j) = (v_{j-1}, v_j)$  or  $\iota(e_j) = (v_j, v_{j-1})$ . In the former case,  $e_j$  is called a **forward branch**, in the latter case it is called a **backward branch** of W. We say that W is a walk **from**  $v_0$  **to**  $v_l$ . The number  $l \in \mathbb{N}_0$  is called the **length** of W. If the nodes  $v_0, ..., v_l$  (and thus also the branches)

are pairwise distinct, W is called a **path**. If  $v_0 = v_l$ , W is called a **cycle**. A cycle  $(v_0, e_1, \ldots, v_{l-1}, e_l, v_0)$  with pairwise distinct nodes  $v_0, \ldots, v_{l-1}$  is called a **loop**.

Sometimes we use the notation  $E(W) := \{e_1, \dots, e_l\}$  for the set of branches appearing in a walk  $W = (v_0, e_1, v_1, \dots, e_l, v_l)$ . The walk  $\overline{W} := (v_l, e_l, v_{l-1}, e_{l-1}, \dots, v_1, e_1, v_0)$  is the **reversed walk** (path/cycle/loop, resp.) of W.

If a walk (path/cycle/loop) W has no backward branches, we call it a **directed walk** (path/cycle/loop).

**Definition 2.6.** Let G be a digraph, let  $W = (v_0, e_1, v_1, \dots, e_l, v_l)$  be a walk in G, and let  $e \in E(G)$  be any branch of G. For  $j = 1, \dots, l$ , define

$$\mu(W, e, j) := \begin{cases} 1 & \text{if } e = e_j \text{ and } \iota(e) = (v_{j-1}, v_j), \\ -1 & \text{if } e = e_j \text{ and } \iota(e) = (v_j, v_{j-1}), \\ 0 & \text{if } e \neq e_j. \end{cases}$$

The incidence index of e in W is

$$\mu(W, e) := \sum_{j=1}^{l} \mu(W, e, j).$$

Remark 2.7. In effect,  $\mu(W, e)$  is the number of times e appears as a forward branch in W minus the number of times e appears as a backward branch in W. If W is a path or a loop,  $\mu(W, e)$  is either 1, -1, or 0. Note that  $\mu(\overline{W}, e) = -\mu(W, e)$  for every walk W and every branch e.

**Definition 2.8.** Let  $W = (v_0, e_1, v_1, \dots, e_l, v_l)$  and  $W' = (v'_0, e'_1, v'_1, \dots, e'_{l'}, v'_{l'})$  be two walks such that  $v_l = v'_0$ . Then we define the walk

$$W \star W' := (v_0, e_1, v_1, \dots, e_l, v_l, e'_1, v'_1, \dots, e'_{l'}, v'_{l'})$$

from  $v_0$  to  $v'_{l'}$ . Furthermore, for every branch e with  $tail(e) = v_l$ , we define the walk

$$W \star e := (v_0, e_1, v_1, \dots, e_l, v_l, e, \text{head}(e))$$

from  $v_0$  to head(e).

**Definition 2.9.** We call a digraph G connected, if for any two nodes  $v, v' \in V(G)$ , there is a walk in G from v to v'.

**Definition 2.10.** Let  $G = (V, E, \iota)$  be a digraph, and let  $\bar{V} \subseteq V$  be a subset of its nodes. We define the digraph  $G|\bar{V} := (\bar{V}, \bar{E}, \bar{\iota})$  by  $\bar{E} := \{e \in E | \iota(e) \in \bar{V} \times \bar{V}\}$  and  $\bar{\iota}(e) := \iota(e)$  for  $e \in \bar{E}$ . If  $G|\bar{V}$  is a connected digraph, and if furthermore there is no other node subset V' such that  $\bar{V} \subsetneq V' \subseteq V$  and G|V' is connected, then  $G|\bar{V}$  is called a **connected component of** G.

**Lemma 2.11.** For every finite digraph G, there is a finite number of subsets  $V_1, \ldots, V_s \subset V(G)$  such that

- 1. The connected components of G are exactly  $G|V_1, \ldots, G|V_s$ .

- 2.  $V_1 \cup \cdots \cup V_s = V(G)$ .

- 3.  $V_i \cap V_k = \emptyset$  for  $j, k = 1, \dots, s$  and  $j \neq k$ .

*Proof.* The existence of one connected component  $G|V_1$  is easily shown. Continue with  $G|(V \setminus V_1)$  to obtain  $V_2$ , and so on.

**Definition 2.12.** G is called **biconnected** if it is connected and remains so after the removal of an arbitrary node, that is, if for every  $v \in V$ , the digraph  $G|(V \setminus \{v\})$  is connected.

**Definition 2.13.** Let G be a directed graph and let  $V(G) = \{v_1, \ldots, v_n\}$ . The **adjacency matrix**  $A^G \in \mathbb{N}_0^{n \times n}$  of G is defined as follows: For  $j, k = 1, \ldots, n$ , the entry  $A_{jk}^G$  is the number of different branches  $e \in E(G)$  with  $\iota(e) = (v_j, v_k)$ .

Remark 2.14. Obviously, the adjacency matrix depends on the order which the nodes  $v_1, \ldots, v_n$  are indexed with. Because in most cases it is clear by notation how the nodes are ordered, it is common practice in textbooks to neglect this dependence. We follow this practice in most parts of this thesis. However, we emphasize here the non-uniqueness of the adjacency matrix, because it will be an important issue in Chapter 4.

**Definition 2.15.** Let G be a directed graph, let  $V(G) = \{v_1, \ldots, v_n\}$  and let  $E(G) = \{e_1, \ldots, e_b\}$ . The **incidence matrix**  $M^G \in \mathbb{Z}^{b \times n}$  of G is defined as follows: For  $j = 1, \ldots, b$  and  $k = 1, \ldots, n$ ,

$$M_{jk}^G := \begin{cases} 0, & \text{if } \operatorname{head}(e_j) \neq v_k \neq \operatorname{tail}(e_j) \text{ or } \operatorname{head}(e_j) = \operatorname{tail}(e_j) = v_k, \\ 1, & \text{if } \operatorname{head}(e_j) = v_k \neq \operatorname{tail}(e_j), \\ -1, & \text{if } \operatorname{head}(e_j) \neq v_k = \operatorname{tail}(e_j). \end{cases}$$

Remark 2.16. The incidence matrix depends on the ordering of the nodes as well as on the ordering of the branches.

**Definition 2.17.** Let G be a directed graph with  $E(G) = \{e_1, \ldots, e_b\}$ , and let S be a loop of G. The **loop incidence vector of** S is

$$u_S := \left(\begin{array}{c} \mu(S, e_1) \\ \vdots \\ \mu(S, e_b) \end{array}\right).$$

Notation 2.18. We denote the transposed matrix of a matrix A by  $A^t$ .

**Lemma 2.19.** For every loop S of a digraph G,  $u_S \in \ker (M^G)^t$ .

*Proof.* Straightforward.

**Proposition 2.20.** For every  $u = (u_1, \ldots, u_b)^t \in \ker (M^G)^t \subset \mathbb{Z}^b$ , there are loops  $S_1, \ldots, S_r$ ,  $r \in \mathbb{N}_0$  such that  $u = u_{S_1} + \cdots + u_{S_r}$  and for every  $l = 1, \ldots, r$ :

- 1. Whenever  $u_j = 0$ , then  $\mu(S_l, e_j) = 0$ .

- 2. Whenever  $u_i > 0$ , then  $\mu(S_l, e_i) \geq 0$ .

- 3. Whenever  $u_i < 0$ , then  $\mu(S_l, e_i) \leq 0$ .

*Proof.* (Sketch.) By induction on  $|u| := \sum_{j=1}^{b} |u_j|$ . Carefully selecting one branch after the other, we can construct a loop  $S_1$  such that 1.-3. hold (for l=1). Then we continue with  $u-u_{S_1}$  instead of u.

Corollary 2.21.  $\ker (M^G)^t$  is generated by the loop incidence vectors.

**Definition 2.22.** A tuple of loops  $S_1, \ldots, S_r$  is called a **system of fundamental loops** if  $u_{S_1}, \ldots, u_{S_r}$  form a basis of ker  $(M^G)$ .

# 2.2. The Toric Ideal of a Digraph

To any directed graph G, we can associate its *toric ideal*, an algebraic object that carries the essential information about the loop structure of G. (In this way, the toric ideal of G is similar, and in fact closely related to the *cycle space* and to the *fundamental groups* of G.) In the context of this thesis, the toric ideal of a digraph is of particular interest, because in the case of a translinear digraph (see Definition 3.5) it actually consists of the translinear loop equations of any network based on that digraph. We will come back to the role of this toric ideal of a translinear network in Subsection 5.1.1.

Of course, there is a general notion of a toric ideal, independent of digraphs and networks. Toric ideals are not only the algebraic building blocks giving rise to the very rich toric geometry (see [Ful97] for an introduction), they also have applications in integer programming and combinatorics and thus attract much attention from the computational viewpoint [Stu97, The99].

**Definition 2.23.** Let k be any field and let  $M = (m_{ij}) \in \mathbb{Z}^{n \times b}$  be an integer matrix. The **toric ideal of** M **over** k, denoted by  $I_A$ , is the kernel of the k-algebra-homomorphism

$$k[x_1, \ldots, x_b] \rightarrow k[t_1, \ldots, t_n, t_1^{-1}, \ldots, t_n^{-1}],$$

$x_j \mapsto t_1^{m_{1j}} \ldots t_n^{m_{nj}}.$

Remark 2.24. Any toric ideal is prime, since it is the kernel of a homomorphism into an integral domain.

Notation 2.25. For  $u=(u_1,\ldots,u_b)\in\mathbb{Z}^b$ , define the monomials  $m_u^+:=\prod_{u_j>0}x_j^{u_j}$ ,  $m_u^-:=\prod_{u_j<0}x_j^{-u_j}$ , and the binomial  $B_u:=m_u^+-m_u^-\in k[x_1,\ldots,x_b]$ .

**Lemma 2.26.**  $I_A$  is generated by  $\{B_u \mid u \in \ker(M) \subset \mathbb{Z}^b\}$ .

Proof. [Stu97, Corollary 4.3]

Notation 2.27. For an ideal  $J \subset k[x_1, \ldots, x_b]$ , we denote its saturation with respect to all variables by  $\operatorname{sat}(J)$ . That is,  $\operatorname{sat}(J) = \{f \mid \exists \text{ monomial } m : mf \in J\}$ .

**Lemma 2.28.** If  $u_1, \ldots, u_s$  form a basis of  $\ker(M)$ , then  $I_A = \operatorname{sat}(\langle B_{u_1}, \ldots, B_{u_s} \rangle)$ .

Proof. [Stu97, Lemma 12.2]  $\Box$

We now focus our attention on the toric ideal of a digraph.

Several authors have examined the toric ideal of a general undirected graph [SVV94, dLST95, OH99]. Ishizeki and Imai have considered toric ideals of acyclic digraphs and Gröbner bases of them [Ish00b, II00b], their publications seem to be the only ones where the toric ideal of a digraph has been mentioned hitherto.

**Definition 2.29.** Let G be a directed graph. The **toric ideal of** G, denoted by  $I_G$ , is the toric ideal of its transposed incidence matrix  $(M^G)^t$  over  $\mathbb{Q}$ .

Remark 2.30. If we identify  $\mathbb{Q}[x_1,\ldots,x_b]$  with the free  $\mathbb{Q}$ -algebra on the set of branches, and  $\mathbb{Q}[t_1,\ldots,t_n,t_1^{-1},\ldots,t_n^{-1}]$  with the free  $\mathbb{Q}$ -algebra on the set of nodes and their inverses, then  $I_G$  is the kernel of the homomorphism defined by  $e \mapsto \text{head}(e)(\text{tail}(e))^{-1}$  for each branch e.

Notation 2.31. For the incidence vector  $u_S$  of a loop S, we abbreviate  $m_S^+ := m_{u_S}^+$ ,  $m_S^- := m_{u_S}^-$ , and  $B_S := B_{u_S}$ .

Lemma 2.32. For a digraph G,

$$I_G = \langle B_S | S \ loop \ of \ G \rangle$$

*Proof.* In view of Lemma 2.26, it suffices to show that  $B_u \in \langle B_S | S \text{ loop of } G \rangle$  for every  $u \in \ker (M^G)^t$ . From Proposition 2.20 we obtain loops  $S_1, \ldots, S_r$  such that  $u = \sum_{i=1}^r u_{S_i}$ , and  $m_{S_i}^+$  and  $m_{S_j}^-$  are coprime for all  $i, j = 1, \ldots, r$ . Thus  $m_u^+ = \prod_{i=1}^r m_{S_i}^+$  and  $m_u^- = \prod_{i=1}^r m_{S_i}^-$ . We can write  $B_u$  as

$$B_u = \sum_{i=1}^r \left(\prod_{j < i} m_{S_j}^-\right) \left(\prod_{j > i} m_{S_j}^+\right) B_{S_i}.$$

### 2. Prerequisites

The last lemma of this chapter provides a possibility to determine a finite generating set for the toric ideal of a digraph:

**Lemma 2.33.** Let  $u_1, \ldots, u_s$  be the loop incidence vectors of a system of fundamental loops of G. Then  $I_G = sat(\langle B_{u_1}, \ldots, B_{u_s} \rangle)$ .

*Proof.* Follows from Lemma 2.28.  $\Box$

# 3. Translinear Network Theory

As mentioned earlier, the goal of this thesis is a coherent and well-structured synthesis methodology for translinear circuits, based on a catalog of topologies.

To give proper foundations for the new synthesis approach, we develop in this chapter (after an introduction to translinear circuits and an earlier synthesis approach in Sections 3.1 and 3.2) a mathematically rigorous perception of translinear circuits. In particular, we give a clean definition of a "translinear network" from a topological point of view.

# 3.1. The Translinear Principle

This section gives a review of the so-called translinear principle, the functional principle of translinear circuits. It has been formulated and given its name by Barrie Gilbert in 1975 [Gil75].

The translinear principle relies on an exponential voltage-to-current relationship of certain devices. The original "translinear device" is the bipolar NPN transistor, other devices with valid exponential models are diodes, PNP transistors and MOS transistors operating in weak inversion [Wie93]. Recently, an emulation of a bipolar transistor has been proposed [DBS04], where a subnetwork structure of three CMOS transistors and one diode shows the necessary exponential behavior.

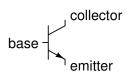

In our circuit diagrams, we will use the symbol of a bipolar NPN transistor, shown in Figure 3.1, to represent an abstract "translinear device", and we will simply use the term "transistor" for such an abstract device. It follows from the above that several different silicon implementations of a "transistor" are possible.

Figure 3.1.: The symbol for a bipolar NPN transistor, our placeholder for a "translinear device".

The ideal exponential model of a transistor is given by the equation

$$I_{CE} = I_S e^{V_{BE}/U_T}, (3.1)$$

saying that its collector current  $I_{CE}$  (the current from collector to emitter) is exponentially dependent on the base voltage  $V_{BE}$  (the voltage between base and emitter). In this model,  $I_S$  and  $U_T$  are device- and operation-dependent parameters called *saturation* current and thermal voltage, respectively. It is assumed that  $I_S > 0$  and  $U_T > 0$ .

We usually make the additional model assumption that the base current (the current from base to emitter) of a transistor is zero.

### 3.1.1. The Static Translinear Principle

The key structures of translinear networks are so-called **translinear loops**. We call a loop W of the network digraph a translinear loop if it satisfies the following three properties:

- W consists exclusively of base-emitter branches of transistor.

- All transistors involved share the same pair  $(I_S, U_T)$  of parameters.

- W consists of as many forward branches as backward branches. Remember that we regard the branches to point "from base to emitter".

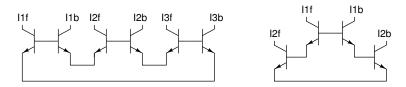

Figure 3.2 shows two examples for a translinear loop.

The interesting property of translinear loops is that due to the exponential transistor model, we can deduce a multiplicative relation of collector currents from KIRCHHOFF's Voltage Law (KVL): Denote the base voltages of the transistors in W-forward orientation by  $V_1^f, \ldots, V_r^f$ , the base voltages of the transistors in W-backward orientation by  $V_1^b, \ldots, V_r^b$ . Then KVL for W reads

$$V_1^f + \dots + V_r^f = V_1^b + \dots + V_r^b$$

.

Figure 3.2.: Examples for translinear loops.

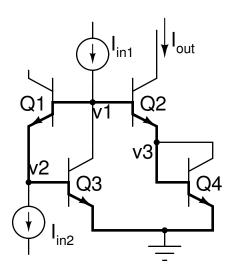

Figure 3.3.: A geometric mean circuit

Taking advantage of the common parameters, we deduce

$$e^{V_1^f/U_T}\cdot\ldots\cdot e^{V_r^f/U_T}=e^{V_1^b/U_T}\cdot\ldots\cdot e^{V_r^b/U_T}$$

and multiplication by  $I_S^r$  yields

$$\left(I_S e^{V_1^f/U_T}\right) \cdot \ldots \cdot \left(I_S e^{V_r^f/U_T}\right) = \left(I_S e^{V_1^b/U_T}\right) \cdot \ldots \cdot \left(I_S e^{V_r^b/U_T}\right).$$

Considering the model equation eqn. (3.1), this means exactly

$$I_1^f \cdot \ldots \cdot I_r^f = I_1^b \cdot \ldots \cdot I_r^b, \tag{3.2}$$

where  $I_1^f, \ldots, I_r^f$  and  $I_1^b, \ldots, I_r^b$  denote the collector currents of the transistors whose base-emitter branches are W-forward or W-backward, respectively.

Remark 3.1. Note that  $I_s$  and  $U_T$  don't occur any more in eqn. (3.2). This means that the relation between the collector currents holds independently of these parameters, provided they are indeed common. One nice effect of this is that translinear networks are essentially temperature-insensitive.

**Example 3.2.** The loop indicated by thick lines in Figure 3.3 is a translinear one, being made up of the base-emitter branches of transistors  $Q_1, \ldots, Q_4$ . (We assume that  $U_T$  and  $I_S$  coincide for the four transistors.) Application of the translinear principle yields<sup>1</sup>

$$I_1 \cdot I_3 = I_2 \cdot I_4. \tag{3.3}$$

Here we simply denote the collector current of a transistor  $Q_j$  by  $I_j$ . We will stick to this convention in the following examples, too.

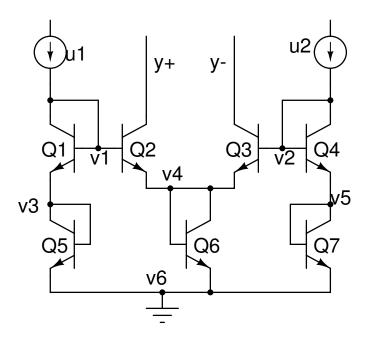

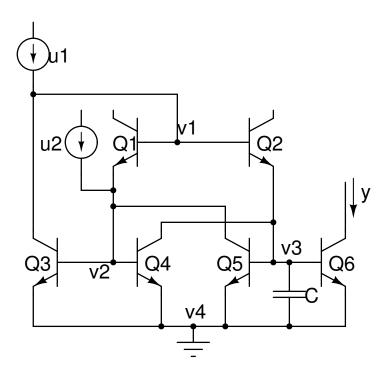

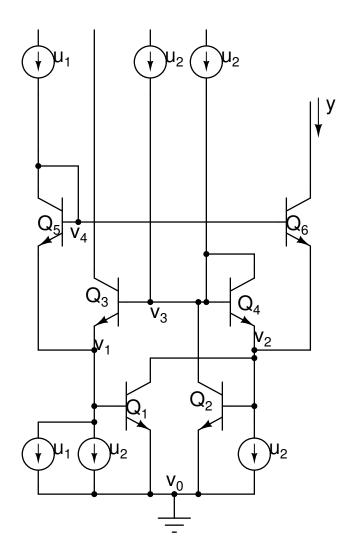

Figure 3.4.: A translinear frequency doubling network. (Since its first publication by GENIN and KONN in 1979 [GK79], this network has become a very prominent example application of the translinear principle.)

Now remember our assumption that base currents are zero. Taking this into account, Kirchhoff's Current Law (KCL) for  $v_1$  means that  $I_3 = I_{\text{in}1}$ . Similarly for  $v_2 : I_1 = I_{\text{in}2}$ , and for  $v_3 : I_4 = I_2 = I_{\text{out}}$ . Thus we can substitute the collector currents in eqn. (3.3) by  $I_{\text{in}1}$ ,  $I_{\text{in}2}$  and  $I_{\text{out}}$ :

$$I_{\text{in}2} \cdot I_{\text{in}1} = I_{\text{out}} \cdot I_{\text{out}},$$

so  $I_{\text{out}} = \sqrt{I_{\text{in}1} \cdot I_{\text{in}2}}$  (since  $I_{\text{out}}$ , being a collector current, must be positive). That means, the network "computes" the geometric mean of the two inputs.

**Example 3.3.** As an example for a network with several translinear loops, consider the network of Figure 3.4.

Transistors  $Q_1$ ,  $Q_2$ ,  $Q_6$ ,  $Q_5$  form a translinear loop. The according equation is

$$I_1 \cdot I_5 = I_2 \cdot I_6. \tag{3.4}$$

Another translinear loop consists of transistors  $Q_3$ ,  $Q_4$ ,  $Q_7$ ,  $Q_6$ . This gives

$$I_3 \cdot I_6 = I_4 \cdot I_7. \tag{3.5}$$

By Kirchhoff's Current Law and our neglection of base currents, we can rewrite eqn. (3.4) and eqn. (3.5) as

$$u_1 \cdot u_1 = y^+ \cdot (y^+ + y^-),$$

$y^- \cdot (y^+ + y^-) = u_2 \cdot u_2.$

A little computation reveals that

$$y^{+} - y^{-} = \frac{u_2^2 - u_1^2}{\sqrt{u_1^2 + u_2^2}}.$$

If we apply sinusoidal inputs with a 90° phase shift, like

$$u_1 = |a\sin t|,$$

$$u_2 = |a\cos t|,$$

with a fixed  $a \in \mathbb{R}$ , then the differential output becomes

$$y^+ - y^- = a\cos 2t,$$

that is, the network shows a frequency doubling behaviour for these inputs.

So every translinear loop leads to an equation of the form of eqn. (3.2). Summarizing the translinear principle in words:

In a loop of base-emitter branches of transistors with the same thermal voltage and the same saturation current, with an equal number of forward and backward branches, the product of collector currents of the transistors whose base-emitter branches are forward in the loop is equal to the product of collector currents of the transistors whose base-emitter branches are backward in the loop.<sup>2</sup>

### 3.1.2. Motivation for a Catalog of Topologies

The following properties of static translinear (STL) networks can be observed from the examples of the preceding subsection:

- STL networks can be described in terms of currents by systems of polynomial equations.

- In such a system, no continuous parameters occur. This is due to the fact that  $U_T$  and  $I_S$  vanish from the equations as soon as the STL principle is applied.

- The topology of translinear networks satisfies strong constraints. One of these constraints is the condition that the number of forward and backward branches in a translinear loop be the same. Another constraint concerns the connection of collectors; it will be considered in Subsection 3.3.2.

<sup>&</sup>lt;sup>2</sup>This is the author's version of many similar formulations of the translinear principle as found in the literature [Gil68, pp. 364–365], [See88, p. 9], [Gil96, p. 107], [Min97, p. 6].

The second property means that the behavior of a STL network is already fixed by the network topology. In particular, there is only a finite number of different STL networks when the number of transistors is bounded!

Together with the third property, which says that the number is not only finite but also "not too large", this observation has inspired the idea of a complete catalog of "small" STL networks. If along with each network appropriate equations are stored, such a catalog can serve as a design tool in an obvious way: When the designer is in search for a circuit with a given desired behavior, she or he can simply run through the catalog to find a network whose equations match that behavior.

Chapter 5 of this thesis is about the details of the usage of such a catalog.

### 3.1.3. The Dynamic Translinear Principle

For so-called dynamic translinear circuits, another circuit element comes into play: The capacitance. The symbol for a capacitance looks like this:

An ideal capacitance has the model equation

$$I_{\rm cap} = C\dot{V}_{\rm cap},\tag{3.6}$$

where of course  $I_{\text{cap}}$  denotes the current through and  $V_{\text{cap}}$  the voltage across the element, and the dot is used to denote time derivative. The device parameter C > 0 is the capacity.

Consider a loop containing one capacitance and one or more base-emitter branches of transistors, as in Figure 3.5. This time, the branch orientations do not matter.

Figure 3.5.: A dynamic translinear loop.

Figure 3.6.: A translinear integrating network. [See90]

KVL for such a **dynamic translinear** (DTL) loop is

$$V_{\text{cap}} = \sum_{j=1}^{l} \pm V_j, \tag{3.7}$$

where the signs depend on the branch orientations. From eqn. (3.1) we deduce that

$$\dot{V}_j = U_T \frac{\dot{I}_j}{I_j}$$

for j = 1, ..., l, so eqn. (3.6) and the differentiation of eqn. (3.7) yield

$$\frac{1}{C}I_{\text{cap}} = U_T \sum_{j=1}^{l} \pm \frac{\dot{I}_j}{I_j}.$$

(3.8)

In short, the dynamic translinear principle says that for every DTL loop, eqn. (3.8) holds.

**Example 3.4.** Figure 3.6 shows a translinear integrating network. The (static) translinear loop equations for this network are

$$I_1 \cdot I_4 = I_2 \cdot I_5, \tag{3.9}$$

$$I_3 = I_4, \tag{3.10}$$

$$I_6 = I_5.$$

(3.11)

There is a dynamic translinear loop consisting of the capacitance and, say,  $Q_6$ . (One could as well consider the loop consisting of the capacitance and  $Q_5$  or the loop consisting of the capacitance,  $Q_2$ ,  $Q_1$  and  $Q_4$ .) The according equation is

$$\frac{1}{C}I_{\rm cap} = U_T \frac{\dot{I}_6}{I_6}. (3.12)$$

The node equations according to KCL are

$$I_3 = u_1$$

for  $v_1$ , (3.13)

$$I_3 = u_1$$

for  $v_1$ , (3.13)

$I_5 = I_1 + u_2$  for  $v_2$ , (3.14)

$I_{\text{cap}} = I_2$  for  $v_3$ . (3.15)

and

$$I_4 + I_{\text{cap}} = I_2$$

for  $v_3$ . (3.15)

$I_1, \ldots, I_5$  and  $I_{\text{cap}}$  can be eliminated from eqns. (3.9) to (3.15), yielding

$$(u_2 - I_6) \cdot u_1 = (u_1 + CU_T \frac{\dot{I}_6}{I_6}) \cdot I_6,$$

which can be simplified to

$$u_2 \cdot u_1 = CU_T \dot{I}_6.$$

If we assume the input  $u_2$  to be a constant scaling factor, we see that the input  $u_1$ is proportional to the time derivative of the output  $y = I_6$ . So indeed, the network effectively performs integration.

Although dynamic translinear networks have important applications, this thesis is mainly about STL networks, and capacitances won't occur very often. In particular, the implementation of a topological catalog as a synthesis tool, which has been produced in the framework of this thesis, is restricted to STL networks.

# Translinear Decomposition of Polynomials

We use the term "translinear decomposition" to denominate the process (or the result) of finding a way of writing a polynomial  $f \in \mathbb{Q}[x_1,\ldots,x_n]$  as an algebraic expression which can be interpreted as one or more translinear loop equations. We think of the variables  $x_1, \ldots, x_n$  as the inputs and outputs of a network to be designed, and of f as an implicit description of the network's desired behavior. Translinear decomposition is an important step of the design trajectory for translinear networks as described by Mulder et. al. [MSvdWvR99].

If one is only interested in networks with only one translinear loop, translinear decomposition amounts to finding a way of writing f in the form

$$f = L_1 \cdot \ldots \cdot L_r - M_1 \cdot \ldots \cdot M_r$$

#### 3. Translinear Network Theory

where  $L_i$  and  $M_i$  are linear combinations of  $x_1, \ldots, x_n$ . An algorithm for translinear decomposition in the 1-loop case is included in the work of Mulder et. al. [MSvdWvR99, pp. 91–107]. The author has developed an alternative algorithm [Ils02] and has compared both algorithms using implementations in MATHEMATICA.

In the general case of several translinear loops, translinear decomposition is much more complicated: Given f, we have to look for "translinear polynomials"

$$f_1 = L_{11} \cdot \ldots \cdot L_{1r_1} - M_{11} \cdot \ldots \cdot M_{1r_1},$$

$$\vdots$$

$$f_s = L_{s1} \cdot \ldots \cdot L_{sr_s} - M_{s1} \cdot \ldots \cdot M_{sr_s}$$

(corresponding to s translinear loops) in the enlarged polynomial ring

$$\mathbb{Q}[x_1,\ldots,x_n,x_{n+1},\ldots,x_{n+s-1}]$$

such that  $f_1 = \cdots = f_s = 0$  implies f = 0 for any given set of real values for  $x_1, \ldots, x_{n+s-1}$ . Here the terms  $L_{ij}$  and  $M_{ij}$  denote linear combinations of the variables  $x_1, \ldots, x_{n+s-1}$ .

The condition " $f_1 = \cdots = f_s = 0$  implies f = 0" can be ensured algebraically by choosing  $f_1, \ldots, f_s$  in such a way that f lies inside the ideal  $\langle f_1, \ldots, f_s \rangle$ , that is, in such a way that there exist  $h_1, \ldots, h_s \in \mathbb{Q}[x_1, \ldots, x_{n+s-1}]$  with

$$f = h_1 f_1 + \dots + h_s f_s. (3.16)$$

Note that since f contains only  $x_1, \ldots, x_n$ , the remaining variables  $x_{n+1}, \ldots, x_{n+s-1}$  must cancel on the right hand side of eqn. (3.16).

No good algorithms are known for translinear decomposition in the general case (also called *parametric decomposition*), and it doesn't seem probable that a satisfactory algorithmic solution can be found, since the problem is in some sense "the wrong way around" compared to classical problems of computer algebra. Also, there are so many degrees of freedom that one can expect a very large number of solutions among which it would be complicated to recognize "good" ones.

Another problem that arises when employing the "translinear decomposition" design trajectory is that it is not clear, once a suitable decomposition is found, how to make the collector currents in fact equal the linear combinations  $L_{jk}$  and  $M_{jk}$ .

Still, it seems worthwhile to research about the algebraic problem of translinear decomposition. However, due to the problems mentioned, the design approach of this thesis avoids translinear decomposition.

# 3.3. The Topology of Translinear Networks

In this section, we give a precise formulation of what a "translinear network" is in terms of graph theory. It will be the basic mathematical model of a translinear circuit's topology and consists essentially of a strict formulation of the constraints which the topology of translinear networks has to obey. Although these constraints have all been known before (their identification is due to E. Seevinck [See88]), their translation into strict mathematics is new.

The precise mathematical formulation is necessary for the specification of the combinatorial task of compiling complete lists of topologies, considered in Chapter 4.

It has been developed in collaboration with E. J. Roebbers and has been published earlier [Ils04, IR04]. The successful application (see Chapter 6) of the techniques of this thesis prove that the topological model fits very well with the industrial needs.

### 3.3.1. Translinear Digraphs

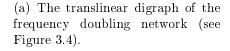

Translinear digraphs are the mathematical objects that are used to represent the core structure of a translinear network, the structure consisting of the translinear loops.

**Definition 3.5.** A translinear digraph is a digraph G satisfying the following properties:

- 1. Every loop of G has as many forward branches as backward branches.

- 2. G is biconnected.

One should think of a translinear digraph G as the digraph formed by the base-emitter branches of a translinear network, that is, the branches of G are in 1-to-1-correspondence with the transistors of the network, and for each branch e, tail(e) corresponds to the base node and head(e) to the emitter node of the respective transistor.

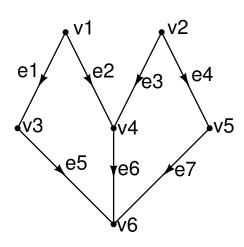

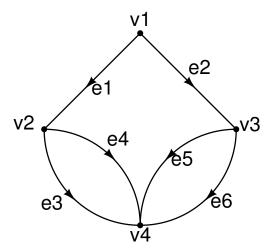

Figure 3.7 shows the translinear digraphs of the example networks from Section 3.1.

(b) The translinear digraph of the integrating network (Figure 3.6).

Figure 3.7.: Two translinear digraphs. The nodes carry the same names as in the corresponding networks; branch  $e_j$  in the digraphs corresponds to transistor  $Q_j$  in Figure 3.4 or Figure 3.6, respectively.

Condition 1 in Definition 3.5 obviously reflects the main requirement on translinear loops as presented in Section 3.1. The reason for including Condition 2 into the definition is that the loops of different biconnected components of the base-emitter digraph are decoupled, so we can consider the corresponding sub-networks separately.

The concept of a translinear digraph as the core of a translinear network was introduced by E. Seevinck [See88], although he concentrated on undirected graphs.<sup>3</sup> (Seevinck's definition differs from the one given here in some more respects.)

It turns out that condition 1 of Definition 3.5 has a nice reformulation, as expressed by the following theorem:

**Theorem 3.6.** Let G be a digraph. The following two statements are equivalent:

- 1. Every loop of G has as many forward arcs as backward arcs.

- 2. There exists a map  $r: V(G) \to \mathbb{Z}$  such that

$$\forall e \in E(G): r(tail(e)) = r(head(e)) + 1.$$

<sup>&</sup>lt;sup>3</sup>This is the reason that the term "translinear graph" is found very often in the literature, whereas "translinear digraphs" have not found much attention hitherto.

*Proof.* First assume there exists a map r as in statement 2. Consider any loop  $W = (v_0, e_1, v_1, \ldots, e_l, v_l), v_l = v_0$  of G. By assumption,

$$r(v_i) = r(v_{i-1}) - \mu(W, e_i)$$

for all j = 1, ..., l. Inductively it follows that

$$r(v_l) = r(v_0) - \sum_{j=1}^{l} \mu(W, e_j)$$

and, because  $v_l = v_0$ ,

$$\sum_{j=1}^{l} \mu(W, e_j) = 0.$$

Since  $\mu(W, e_j) = \pm 1$  for all j = 1, ..., l, the latter is a sum of as many 1's as -1's, which just means that W contains as many forward arcs as backward arcs.

For the other direction of the proof, assume that every loop contains as many forward arcs as backward arcs. In terms of incidence indices, this means

$$\sum_{e \in E(W)} \mu(W, e) = 0 \tag{3.17}$$

for every loop W. It follows that eqn. (3.17) also holds if W is any cycle.

Construct a map r with the stated property in the following way: For each connected component C of G, pick an arbitrary vertex  $v_C \in V(C)$ . Then, for each vertex  $v \in V(C)$ , fix a walk P from  $v_C$  to v and define

$$r(v) := -\sum_{e \in E(P)} \mu(P, e).$$

It is now necessary to show that this definition is independent of the chosen walk P. So, let P' be another walk from  $v_C$  to v. Then  $P \star \overrightarrow{P'}$  is a cycle and

$$\begin{split} 0 &= \sum_{e \in E(P \star \overleftarrow{P'})} \mu(P \star \overleftarrow{P'}, e) \\ &= \sum_{e \in E(P)} \mu(P, e) - \sum_{e \in E(P')} \mu(P', e), \end{split}$$

in particular

$$-\sum_{e \in E(P)} \mu(P, e) = -\sum_{e \in E(P')} \mu(P', e),$$

which shows that r(v) is indeed well-defined.

Applying this construction to every connected component C of G, the map r indeed gets the desired property: Let  $e_0 \in E(C)$  be any branch of some component C. If W

is a walk from  $v_C$  to  $tail(e_0)$ ,  $W' := W \star e_0$  is a walk from  $v_C$  to head $(e_0)$ , and by the definition of r,

$$\begin{split} r(\operatorname{head}(e_0)) &= -\sum_{e \in E(W')} \mu(W', e) \\ &= -\left(\sum_{e \in E(W)} \mu(W', e)\right) - \mu(W', e_0) \\ &= -\left(\sum_{e \in E(W)} \mu(W, e)\right) - 1 \\ &= r(\operatorname{tail}(e_0)) - 1. \end{split}$$

It is clear that if a map r as in the second statement of Theorem 3.6 exists, so does a map  $r_0$  that fulfills the same condition as well as the additional property

$$\min_{v \in V(G)} r_0(v) = 0. \tag{3.18}$$

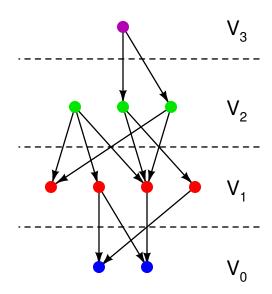

(Simply define  $r_0(v) := r(v) - \min_{v' \in V(G)} r(v')$ .) The nodes can then be partitioned into "levels" or "layers", such that a branch always points from one layer to the next lower layer:

$$V = V_0 \stackrel{.}{\cup} V_1 \stackrel{.}{\cup} \dots \stackrel{.}{\cup} V_R$$

where  $V_j = \{v \in V | r_0(v) = j\}$  and  $R := \max_{v \in V} r_0(v)$ . This is illustrated in Figure 3.8.

**Example 3.7.** In Figure 3.7(a), R = 2,  $V_0 = \{v_6\}$ ,  $V_1 = \{v_3, v_4, v_5\}$  and  $V_2 = \{v_1, v_2\}$ . In Figure 3.7(b), R = 2,  $V_0 = \{v_4\}$ ,  $V_1 = \{v_2, v_3\}$  and  $V_2 = \{v_1\}$ .

**Definition 3.8.** We call a digraph fulfilling one and thus both conditions of Theorem 3.6 a **layered digraph**.

We see that a translinear digraph is nothing but a biconnected layered digraph.

For any connected layered digraph, the additional property of eqn. (3.18) makes  $r_0$  unique.

**Definition 3.9.** Let G be a connected layered digraph. For a node  $v \in V(G)$ , we call the integer  $r_0(v)$  the **rank** of v, and also denote it by  $\operatorname{rank}(v)$ .

In other words, the rank of a node is the index of the layer it belongs to.

Figure 3.8.: layers of a translinear digraph

What is crucial about the layers of the translinear digraph of a network is that the rank of a node corresponds nicely to a certain range of the electric potential the node will have in an actual circuit. This is because the voltage drop along a base-emitter branch is always much larger than the swing of potential at one particular node.

Since the rank is a node invariant, it also helps a lot in the classification of translinear digraphs, as will become apparent in Chapter 4.

### 3.3.2. Connection of Collectors

The previous subsection dealt with the base-emitter connectivity of a translinear network, which can be encoded in a translinear digraph. The main piece of information that is furthermore needed to describe a complete network is where to connect the collectors to.

Let e be a branch of a translinear digraph G. The collector of the transistor corresponding to e can only be connected to a node v of G if  $\operatorname{rank}(v) > \operatorname{rank}(\operatorname{head}(e))$ . The reason is that  $\operatorname{head}(e)$  is the emitter node, and the collector needs a higher potential than the emitter. E. Seevinck considered this condition in the construction of his "T-matrices" [See88].

We denote the collector node of a transistor corresponding to a branch e of the translinear digraph by C(e).

**Example 3.10.** For the integrating network (Figure 3.6), we have  $C(e_3) = v_1$ ,  $C(e_4) = v_3$  and  $C(e_5) = v_2$  (using branch names as in Figure 3.7(b)).

But a collector does not necessarily need to be connected to a node of the translinear digraph. It can also serve as a (current-mode) output of the network, or it can be connected directly to a voltage supply. We will express this by  $C(e) = v_{\text{ext}}$ , imagining  $v_{\text{ext}}$  as an additional node outside of G.

**Example 3.11.** In Figure 3.6/Figure 3.7(b),

$$C(e_1) = C(e_2) = C(e_6) = v_{\text{ext}}$$

.

In summary:

A translinear network topology is specified by

- $\bullet$  a translinear digraph G

- and a map  $C: E(G) \to V(G) \cup \{v_{\text{ext}}\}$ , where C has the property that for each  $e \in E(G)$ , either  $C(e) = v_{\text{ext}}$  or

$$rank(C(e)) > rank(head(e)). \tag{3.19}$$

We identify

```

a branch e with a transistor,

tail(e) with the transistor's base node,

head(e) with the transistor's emitter node,

and C(e) with the transistor's collector node.

```

We call the map C the **collector assignment** of the network. (The notion of a collector assignment will be refined in Section 3.4.)

**Example 3.12.** We can describe the frequency doubling network of Figure 3.4 by the pair (G, C), where G is the translinear digraph depicted in Figure 3.7(a) and C is the collector assignment

$$C(e_1) = v_1,$$

$$C(e_2) = v_{\text{ext}},$$

$$C(e_3) = v_{\text{ext}},$$

$$C(e_4) = v_2,$$

$$C(e_5) = v_3,$$

$$C(e_6) = v_4,$$

$$C(e_7) = v_5.$$

Remark 3.13. Note that in the latter example,  $C(e_j) = \operatorname{tail}(e_j)$  for j = 1, 4, 5, 6, meaning that the collector is connected to the same node as the base of the respective transistor. In such cases of diode-like transistor usage, the condition expressed by eqn. (3.19) is "automatically" satisfied, since by the definition of the rank of a node,

$$rank(tail(e)) = rank(head(e)) + 1.$$

The information given by a translinear digraph G and a collector assignment C is already a fairly complete description of a translinear network. In particular, a netlist for simulation or symbolic analysis of the network can be set up, if just some necessary "interface" information is added, for instance the connection of independent current sources which represent inputs of the network. These interfacing issues will be considered in Section 3.4.

### 3.3.3. Insertion of Capacitances

The considerations of the preceding subsection are valid for STL networks as well as for DTL networks. But while the topology of a STL network is sufficiently modeled by a translinear digraph and a collector assignment, we must make one addition for DTL networks: How are capacitances allowed to be connected in the network?

The answer is quite simple: A capacitance can be inserted between any pair of nodes of the translinear digraph. In Figure 3.6, for example, the capacitance branch is between node  $v_3$  and the ground node  $v_4$ , which are both nodes of the underlying translinear digraph (see Figure 3.7(b)).

Thus, a DTL network topology is given by a triple  $(G, C, E_{cap})$  of a translinear digraph G, a collector assignment C on G, and a subset  $E_{cap}$  of the set of 2-element subsets of G. (See also [IR04].)  $E_{cap}$  then consists of those pairs of nodes where a capacitance is connected inbetween.

### 3.4. The Interface of a Translinear Network

This section addresses the question of what should be considered as the "interface" of a translinear network, i. e. of how inputs are applied to and outputs are supplied by the network.

Since the introduction of the translinear principle by Barrie Gilbert [Gil75] it is clear that inputs and outputs of a translinear network are in current mode.

### 3.4.1. **Outputs**

All collectors which are designated "external" by the collector assignment C (i. e., the collectors of those transistors for which  $C(e) = v_{\rm ext}$ ) can be used as outputs of the network. But not only the current of a single collector, also sums or differences of them can be considered as outputs. To be general, we consider a single symbolic output y of a network which is a sum of positive and negative collector currents:

$$y = \sum_{C(e)=v_{\text{ext}}} \sigma(e) x_e, \tag{3.20}$$

where  $x_e$  denotes the collector current of the transistor corresponding to branch e and  $\sigma(e) \in \{-1, 0, 1\}$ .

**Example 3.14.** For the frequency doubling network (Figure 3.4),  $\sigma(e_2) = 1$  and  $\sigma(e_3) = -1$ . For the integrating network (Figure 3.6),  $\sigma(e_1) = \sigma(e_2) = 0$  and  $\sigma(e_6) = 1$ .

To avoid the usage of  $\sigma$ , we will henceforth work with the following refined concept of a collector assignment: From now on, a collector assignment will be a map

$$C: E(G) \rightarrow V(G) \cup \{v_{\text{out+}}, v_{\text{out-}}, v_{\text{void}}\}$$

such that for every  $e \in E(G)$ :

$$C(e) \in \{v_{\text{out+}}, v_{\text{out-}}, v_{\text{void}}\}\ \text{or}\ \operatorname{rank}(C(e)) > \operatorname{rank}(\operatorname{head}(e)).$$

Thus, the symbolic output of a network will be (compare to eqn. (3.20)):

$$y = \sum_{C(e)=v_{\text{out}+}} x_e - \sum_{C(e)=v_{\text{out}-}} x_e.$$

(3.21)

### 3.4.2. Inputs and Ground Node Selection

In principle, an independent input current  $i_v$  can be applied to any node v of the translinear digraph G. The only restriction is that the sum of all input and output currents (the latter are now all collector currents with  $C(e) \in \{v_{\text{out}}, v_{\text{out}}, v_{\text{void}}\}$ ) must always be zero, which cannot be satisfied if independent currents are prescribed for all nodes of G. (In this case, the modelling assumptions about the transistors are not valid anymore.) Therefore, one has to select one particular node  $v_0$  of G that serves as a "valve" whose "dependent input" current results from values of the "true" inputs and of the outputs. (One should regard this dependence in terms of KCL for the ground node.)

For convenience, we will always choose this "valve" node as the "reference" or "ground" node of the circuit, thus there will be no distinction between "valve node" and "ground node", and we simply assume that we have an independent current source connected to each node of G except one, which we call the ground node and denote by  $v_0$ . We call all other nodes "input nodes".

In the examples we have seen so far, most of the nodes of the translinear digraph have no current source connected to them. This amounts to an independent input which happens to be a constant zero and is not to be confused with the role of the ground node!

**Example 3.15.** For the frequency doubling network (Figure 3.4):  $v_0 = v_6$ ;  $i_{v_1} = u_1$ ,  $i_{v_2} = u_2$ ,  $i_{v_3} = i_{v_4} = i_{v_5} = 0$ .

**Example 3.16.** For the integrating network (Figure 3.6):  $v_0 = v_4$ ;  $i_{v_1} = u_1$ ,  $i_{v_2} = u_2$ ,  $i_{v_3} = 0$ .

A triple  $(G,C,v_0)$  of a translinear digraph G, a collector assignment C (in the refined sense) and a ground node  $v_0$  is a network description which is complete in the sense that the network equations can entirely be set up. The resulting system of polynomial equations will be studied in Section 5.1. That system contains all node equations but the one of  $v_0$ . For this reason, the current into the collector of the transistor corresponding to a branch e with  $C(e) = v_0$  does not occur in the network equations. The same is true if  $C(e) = v_{\text{void}}$ , while in all other cases, the collector current belonging to e does affect the system: either in the node equation of  $C(e) \in V(G) \setminus \{v_0\}$  or, if  $C(e) \in \{v_{\text{out}+}, v_{\text{out}-}\}$ , in the output equation.

Hence, for the system of network equations, it does not matter whether  $C(e) = v_{\text{void}}$  or  $C(e) = v_0$  for a branch e. To avoid redundant entries in our catalog, we do not allow  $C(e) = v_0$  for any e. The simplest possibility to guarantee  $C(e) \neq v_0$  for all e is to choose  $v_0 \in V(G) \setminus \text{img}(C)$ .

We arrive at the following precise formal definition of a translinear network:

**Definition 3.17.** A (static) formal translinear network is a triple  $N = (G, C, v_0)$  of a translinear digraph G, a map  $C : E(G) \to V(G) \cup \{v_{\text{out}+}, v_{\text{out}-}, v_{\text{void}}\}$  and a node  $v_0 \in V(G) \setminus \text{img}(C)$ , such that for every  $e \in E(G)$ :

$$C(e) \in \{v_{\text{out-}}, v_{\text{out-}}, v_{\text{void}}\}\ \text{ or } \operatorname{rank}(C(e)) > \operatorname{rank}(\operatorname{head}(e)).$$

We call C the collector assignment of N and  $v_0$  the ground node of N. The number of transistors of N is the number of branches of G.

### 3.5. Topologies for 4-terminal MOS transistors

Next to bipolar transistors, subthreshold MOS transistors can be employed as "translinear device".

In the preceding sections, we frequently used a terminology that is adopted from the bipolar case. Speaking of MOS transistors, we should replace "base" by "gate", "emitter" by "source" and "collector" by "drain". But in addition to these three terminals, several authors have begun to use the "back gate" or "bulk" terminal of MOS transistors as an independent fourth terminal, instead of short-circuiting it "by law" with the source terminal [Ser05, MvdWSvR95, AB96, SGLBA99].

The topological concepts developed in the preceding sections are based on 3-terminal transistor devices. This section gives some ideas to adapt the concepts for 4-terminal MOS devices. However, a coherent description as for the 3-terminal case is not achieved.

Our proposals are based on the "general translinear principle for subthreshold MOS transistors" by Serrano-Gotarredona, Linares-Barranco and Andreou [SGLBA99]. We restrict to subthreshold MOS transistors employed in forward region.<sup>4</sup> For examples, we refer to the literature mentioned above.

<sup>&</sup>lt;sup>4</sup>We did the same for bipolar transistors by using eqn. (3.1) as model equation.

#### 3. Translinear Network Theory

MOS translinear loops consist either of gate-source branches or of bulk-source branches. Analogously to the translinear digraph, which is the "base-emitter" digraph of bipolar translinear networks, we can consider a gate-source digraph  $G_{\rm gate}$  and a bulk-source digraph  $G_{\rm bulk}$  of a MOS translinear network.  $G_{\rm gate}$  and  $G_{\rm bulk}$  share a common node set

$$V := V(G_{\text{gate}}) = V(G_{\text{bulk}}),$$

and furthermore, there is bijection

$$h: E(G_{\text{gate}}) \to E(G_{\text{bulk}})$$

identifying branches representing the same transistor, such that

$$tail(e) = tail(h(e))$$

for each  $e \in E(G_{\text{gate}})$ . (Since both tails are to be identified with the source of the transistor.)

According to [SGLBA99], it is not necessary to impose any loop condition similar to the one for the bipolar case ("as many forward as backward branches") to  $G_{\text{gate}}$  or  $G_{\text{bulk}}$ . The biconnectedness condition applies to the "superposition" digraph

$$(V, E(G_{\text{gate}}) \dot{\cup} E(G_{\text{bulk}}), \iota).$$

The examples in [SGLBA99] show that neither  $G_{\text{gate}}$  nor  $G_{\text{bulk}}$  can be assumed to be biconnected by itself, in fact, they cannot even be assumed to be connected.

For connecting the drain terminals, one should require that they are provided with a higher potential than the corresponding source terminal. However, lacking layers of  $G_{\text{gate}}$  or  $G_{\text{bulk}}$ , we cannot use a convenient formal condition, like eqn. (3.19) for the bipolar case, to express this requirement. In the example circuits known to the author, all drain terminals are either used as outputs or are short-circuited with the gate terminal of the respective transistor.

The preceding chapter provides a way to regard translinear networks as formal combinatorial objects. This chapter describes techniques to generate complete lists of these formal objects, in order to compile catalogs of translinear networks which are exhaustive in the sense that they contain all possible topologies.

Synthetic lists of translinear graphs and translinear digraphs have been produced before [See88, Wie93]. However, the idea to list complete network descriptions is new.

The first section of this chapter introduces a common method in combinatorics to list graphs or other combinatorial objects. Since the core structures of translinear networks are translinear digraphs, Section 4.3 describes how to specialise the method for this particular class of digraphs, prepared by Section 4.2 on the generation of general digraphs. Sections 4.4 and 4.5 then deal with the exhaustive generation of collector assignments and complete formal networks for a given translinear digraph.

### 4.1. Orderly Generation

This section describes orderly generation, a method for exhaustive generation of combinatorial objects. It was developed mainly by R. Read [Rea78]. It will be applied to the generation of formal translinear networks in the following sections.

Subsection 4.1.1 introduces the general class of problems which orderly generation applies to. Subsection 4.1.2 then covers the basic ideas of orderly generation, and in Subsection 4.1.3 the main type of applications of orderly generation is presented.

# 4.1.1. Cataloging Problems

The term "catalog" is used here to refer to a complete but redundance-free list of combinatorial structures such as elementary ones like sequences, permutations or partitions, but also more complex ones like graphs in several variants (simple graphs, multigraphs, digraphs, trees, colored graphs, etc.), designs [Dem97, And90, AK92, Col96, BJL99] or linear codes [BFK<sup>+</sup>98, in particular chapter 3].<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Of course, the literature provides plenty of more examples of combinatorial structures which a catalog makes sense of. In fact, structure is brought into the vast range of examples by a well-developed the-

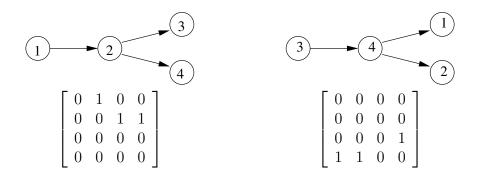

Figure 4.1.: Two labeled digraphs and their adjacency matrices.

Catalogs of these structures are useful in many respects: In pure mathematics, they can serve as a source of examples, especially for testing new conjectures. Also, classification problems in many mathematical disciplines often boil down to discrete cataloging problems. In practical applications, catalogs allow to get hands on error-correcting linear codes, designs of agricultural experiments, isomers of a molecule, or, being the motivation of the present work, possible topologies of electrical networks.

Main references for cataloging techniques, which can also be paraphrased as *generation* of structures, are [Lau93, Lau99, GLM97, Rea78]. Related but not to be confused with generation is enumeration (counting) of structures, treated by [Red27, PR87, KT83, GJ83, dB64]. Both generation and enumeration are dealt with in [Ker99] or [KS99].

Except for the most simple structures, it is a nontrivial task to produce a catalog. The difficulties will become apparent after the following general formulation of a cataloging problem.

Assume that for each  $b \in \mathbb{N}$ , we have a finite set  $L_b$  whose elements are easily digitally represented and also easily listed in the sense that we can produce a list of all elements of  $L_b$  in a time that is proportional to their number  $|L_b|$ . Furthermore, assume  $L_b \cap L_{b'} = \emptyset$  for  $b \neq b' \in \mathbb{N}$  and denote  $L := \bigcup_{b=0}^{\infty} L_b$ . We call the elements of  $L_b$  the **labeled structures of size** b.

In the case of digraphs, for example, we take a fixed set of nodes V and let  $L_b$  be the set of digraphs with node set V and exactly b branches. Adjacency matrices are a convenient digital representation of digraphs, and we can think of  $L_b$  as those matrices whose total sum of entries is b.

Figure 4.1 shows two digraphs and their adjacency matrices. Since the matrices differ, we have two different elements of  $L_b$ .

Unfortunately, the labeled structures are not yet what we are really interested in. Rather, we are interested in **unlabeled structures** which are isomorphism classes of the labeled structures. Since the two digraphs in Figure 4.1 are clearly isomorphic, we do not want

ory of so-called **species** representing the types of combinatorial structures. [Ehr65, Joy81, BLL98], see also [Ker99, pp. 1–20].

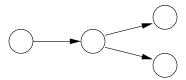

to have both of them in a list of "all digraphs with 4 nodes and 3 branches", rather we want to have only one representative looking like this:

The example makes quite clear where the terminology "labeled" and "unlabeled" comes from.

In general, we have an equivalence relation  $\sim$  on  $L_b$ , where  $A \sim B$  is to be interpreted as "A and B differ only by their labelings" or "A and B are isomorphic".<sup>2</sup> Thus, an **unlabeled structure of size** b is an element of  $L_b/\sim$ .

In the case of digraphs with n nodes and b branches, the equivalence relation in terms of adjacency matrices is the one induced by the action of  $S_n$  consisting of simultaneous row and column permutations: Two  $n \times n$  matrices  $A, B \in L_b$  are "isomorphic" if and only if there is a permutation  $\sigma$  which, when applied simultaneously to rows and columns, transforms A into B:

$$A \sim B \iff \exists \sigma \in S_n : \text{ For all } i, j = 1, \dots, n : B_{ij} = A_{\sigma(i)\sigma(j)}.$$

(In Figure 4.1 above,  $\sigma = (1\ 3)(2\ 4)$  transforms the two matrices into each other.  $\sigma$  also permutes the node labels of the two digraphs in the appropriate way.)

The example of digraphs is presented here because digraphs are of course the structures we are specifically interested in for our purposes; further examples of labeled and unlabeled structures are nicely presented in the first chapters of [Ker99]. Quite an interesting example is the one of linear codes, where equivalence is isometry of codes, i.e. equivalent codes are guaranteed to show the same error-correcting behavior.

In general, the best way to represent an unlabeled structure digitally is to represent it by one of the labeled structures it is made up of. That means that we can define a catalog as a subset  $U \subset L$  which has the property that for every  $A \in L$  there is a unique  $B \in U$  such that  $A \sim B$ . In other words, U should contain exactly one element from each isomorphism class. Such a set U is called a **complete system of representatives** or a **transversal** of  $L/\sim$ .

It is worth to point out that in principle, there is of course no problem to list unlabeled structures completely: One can just list the labeled structures. Every unlabeled structure will be represented in the list at least once. The problem is that because in most cases it will be represented by quite a lot of labeled structures, the list gets very redundant

<sup>&</sup>lt;sup>2</sup>In more precise notation, one would use  $\sim_b$  instead of  $\sim$ . Omitting the reference to b does not, however, cause any ambiguity. In fact, we can define  $\sim$  globally on  $L = \bigcup_{b=1}^{\infty} L_b$  by specifying that  $A \sim B$  should imply that A and B are of the same size.

and much too long, so that even when one just wants a complete list and redundance doesn't disturb by itself, the reduction of complexity obtained by eliminating isomorphs can be a great improvement of efficiency.

The naive approach for generating a transversal of  $L_b/\sim$  is expressed by the following pseudocode:

### Algorithm 1 generateTransversal

```

1: U_b := \emptyset

2: for all x \in L_b do

3: if there is no u \in U_b with x \sim u then

4: U_b := U_b \cup \{x\}

5: end if

6: end for

7: return U_b

```

This algorithm is very slow because the isomorphism test  $u \sim x$ , which is in most cases very expensive, is performed very often. In the following subsection it will be shown how this can be avoided.

### 4.1.2. Canonicity and Augmentation

The basic idea to avoid the isomorphism test of Algorithm 1 is very intuitive:

If we find some definition of "canonicity", a property that exactly one element of each  $\sim$ -class possesses, we can simply test all labeled structures for this property and thus generate the set of "canonical" elements of  $L_b$ , which is then our transversal of  $L_b/\sim$ :

### Algorithm 2 generateCanonicalTransversal

```

1: U_b := \emptyset

2: for all x \in L_b do

3: if x is canonical then

4: U_b := U_b \cup \{x\}

5: end if

6: end for

7: return U_b

```

This is a considerable improvement compared to Algorithm 1, because the so-far built  $U_b$  doesn't need to be searched through in each cycle.

Note that it does not matter for Algorithm 2 if we replace  $U_b$  by the complete U, this amounts to the same as successive generation of each  $U_b$ . In contrast to this, the splitting of U into the  $U_b$ 's is substantial for Algorithm 1, since in line 3 we would have to check all elements  $u \in U$ , instead of only  $u \in U_b$ , for being an isomorph of x.

An appropriate definition of canonicity is easily found: Usually, the set L of labeled structures is endowed with some natural total order, which comes from a numerical or lexicographical interpretation of the "labelings" and their digital representations. For example, one can imagine a 0-1-matrix (representing a simple labeled graph or digraph), read row by row, as a binary encoded integer. Thus, graphs are ordered by the integer ordering.

But once we have fixed a total order < on L, we simply define the canonical representative of a  $\sim$ -class to be the maximal one with respect to <,

$$x \in L$$

canonical  $:\iff y < x$  for all  $y \in L$  with  $y \sim x$  and  $y \neq x$ .

The details of the canonicity check in algorithm 2 of course depend on the definition of a canonical structure, but it can be expected that this test is as expensive as one isomorphism test. For instance, to test two digraphs with n nodes for isomorphism, in general one has to try the n! bijections between their node sets. To test the adjacency matrix A of one n-node digraph for canonicity, one has to compare A with the n! roward column- permuted matrices  $P_{\sigma}^{-1}AP_{\sigma}$ ,  $\sigma \in S_n$ , to find out whether A is maximal. (Here,  $P_{\sigma}$  denotes the permutation matrix of  $\sigma$ , defined by

$$(P_{\sigma})_{ij} = \begin{cases} 1 & \text{if } \sigma(i) = j \\ 0 & \text{otherwise} \end{cases}$$

for

$$i, j = 1, ..., n$$

.)

Thus it is further desirable to reduce the number of canonicity checks. This is possible if a suitable augmentation operation is at hand which produces structures of size b+1 from a structure of size b. In most applications, plenty of different augmentations can be thought of. To make an augmentation really useful, it should satisfy the following requirement.

**Definition 4.1.** Let  $U \subseteq L$  be a transversal of  $L/\sim$ . A *U*-complete augmentation is a map

aug:

$$L \to \mathcal{P}(L)$$

such that for every  $b \in \mathbb{N}$ ,  $\operatorname{aug}(x) \subseteq L_{b+1}$  for  $x \in L_b$  and

$$\bigcup_{x \in U_b} \operatorname{aug}(x) \supseteq U_{b+1},$$

where  $U_b := U \cap L_b$ .

An example of a quite versatile U-complete augmentation is given in the next subsection.

If aug is a U-complete augmentation, the following algorithm obviously computes the transversal  $U_{b+1}$  from  $U_b$ :

#### Algorithm 3 generateByAugmentation

```

1: U_{b+1} := \emptyset

2: for all u \in U_b do

3: for all x \in \text{aug}(u) do

4: if x is canonical then

5: U_{b+1} := U_{b+1} \cup \{x\}

6: end if

7: end for

8: end for

9: return U_{b+1}

```

Algorithm 3 can be successively applied from b = 0 on (assuming  $U_0 = L_0$  or something likewise trivial) to a desired size.

The fundamental difference compared to algorithms 1 and 2 is that in order to take advantage of the augmentation, we now really depend on the decomposition  $U = \bigcup U_b$ . The gain is that it is not necessary to run through all labeled structures of size b to generate the transversal  $U_b$ .

Remark 4.2. If the augmentation has the property that every structure of size b+1 has a unique predecessor of size b, that is, if  $\operatorname{aug}(u) \cap \operatorname{aug}(u') = \emptyset$  for  $u \neq u'$ , then we know for sure that in line 3 of Algorithm 3, x is not yet included in  $U_{b+1}$ . This makes the insertion of x into  $U_{b+1}$  easier to implement and faster. We will make use of this advantage throughout our particular applications.