# Low Jitter Gb/s CMOS Clock and Data Recovery Circuits for Large Synchronous Networks

A dissertation submitted to

the Faculty of Electrical and Computer Engineering

of University of Kaiserslautern

in partial fulfillment of the requirements

for the degree of

**Doctor of Philosophy**

in Electrical Engineering

Sitt Tontisirin

Date of Submission 3<sup>rd</sup> May 2007

Date of Defense: 25<sup>th</sup> April 2008

Dean of Faculty: Prof. Dr.-Ing. S. Liu

Promotion committee

Committee chair: Prof. Dr.-Ing. A. König

1. Committee examiner: Prof. Dr.-Ing. D. Schmitt-Landsiedel

2. Committee examiner: Prof. Dr.-Ing. N. Wehn

3. Committee examiner: Prof. Dr.-Ing. U. Brüning

## Thesis in Electrical Engineering

## Sitt Tontisirin

## Low Jitter Gb/s CMOS Clock and Data Recovery Circuits for Large Synchronous Networks

## Acknowledgement

This thesis could not be accomplished without the help and support of many people. Firstly, I would like to deeply thank my advisor Professor Reinhard Tielert for giving me the opportunity to conduct the research at the Institute of Microelectronics. He was always available and gave me the valuable discussions. Even through, he was not able to be the committee examiner in my examination, I believe he wished me luck and took care of me from above. I do deeply appreciate Professor Doris Schmitt-Landsiedel from TU Munich (Technische Universität München) for kindly being my committee examiner that made me possible to accomplish the examination. I would like to thank Professor Norbert Wehn for taking over the coordination to proceed my examination process and for kindly being my committee examiner. I would like to express thanks to Professor Ulrich Brüning for his valuable time being my committee examiner and his kindness during the collaboration. It is my grateful to the committee chair Professor Andreas König for his time and interest. I would also like to express thanks to Dr. Jürgen Rötter for his kind administration.

I profited from the research projects with many collaborators. I would like to express my appreciation to Heinz Endriss, Henrik Icking, and Andreas Hebenstreit of the Infineon Technology for their support. It is my grateful to Professor Volker Lindenstruth, the Kirchoff Institute for Physic, the University of Heidelberg, for the challenge research project. I would also like to thank Walter Müller of the GSI-Darmstadt for the research project motivating this thesis.

I am greatly indebted to Ursula Pöpperl, Axel Schmitz, Marco Lambert, Marc Wegener, and Jutta Praetorius for sharing the good time in the Institute. I would like to thank David Muthers not only for the pleasurable collaboration but also for sharing an experience of a long business trip. I would also like to thank to my colleagues Emna Ayari, Muhammad Anis, and Thomas Ilnseher for sharing the knowledge and though and for the enjoyable cooperation. I would like to express my thanks to Supriyanto and Faraz for their support in the layout design for the project works. It is my grateful to Markus Müller, Andreas Christmann, and Roland Volk for the kindly support of the CAD and experimental

facilities. In addition, I would like to thank Barbara Mundell for her kind administrative assistance.

I would also like to thank my teachers, advisors, friends and colleagues during my study and careers in Thailand and Germany, whom I could not name all here. I appreciate the sharing moments and their contributions to my individuality and my though.

Finally I would like to thank my patents, sisters and brother for their care and encouragement. I would like to express thanks to my wife Supak. Without her love and support, I would not have passed the difficulties until today.

## **Table of Contents**

| ABSTRACT                                                        | vii |

|-----------------------------------------------------------------|-----|

| KURZFASSUNG                                                     | ix  |

| 1 INTRODUCTION                                                  | 1   |

| 1.1 MOTIVATION                                                  | 1   |

| 1.2 SCOPE AND ORGANIZATION                                      | 6   |

| 2 DESIGN CONSIDERATIONS OF CDR FOR TIME AND CLOCK               |     |

| DISTRIBUTION                                                    | 7   |

| 2.1 Introduction                                                | 7   |

| 2.2 CDR SPECIFICATIONS                                          | 8   |

| 2.2.1 Jitter transfer function                                  | 8   |

| 2.2.2 Jitter peaking                                            | 9   |

| 2.2.3 Jitter Tolerance                                          | 9   |

| 2.2.4 Jitter generation                                         | 10  |

| 2.3 JITTER IN SERIAL COMMUNICATION SYSTEM                       | 10  |

| 2.3.1 Transmitter jitter                                        | 10  |

| 2.3.2 Channel jitter                                            | 14  |

| 2.3.3 Receiver jitter                                           | 18  |

| 2.4 PLL-based CDR and clock synthesizer                         | 18  |

| 2.4.1 PLL linear model                                          | 19  |

| 2.4.2 Loop characteristic design and jitter in PLL              | 24  |

| 2.5 THE ARCHITECTURES OF CDRs FOR LARGE SYNCHRONOUS NETWORKS    | 26  |

| 2.5.1 The CDR with a clock extraction and a phase tracking loop | 27  |

| 2.5.2 The CDR with a clock-jitter-filter                        | 28  |

| 2.6 SIMMADY                                                     | 20  |

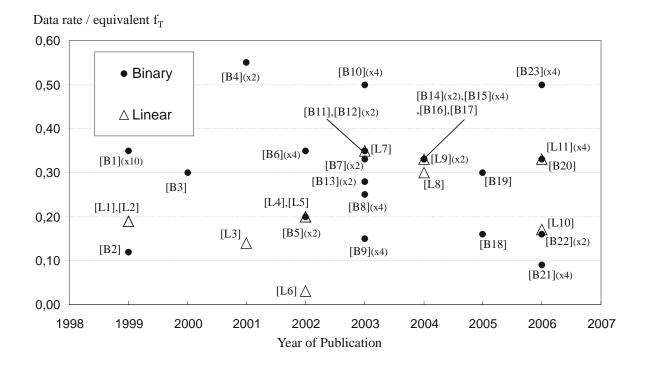

| 3 STRUCTURE OF THE FRONT-ENDED LOOP: PLL-BASED CDR                          | 31 |

|-----------------------------------------------------------------------------|----|

| 3.1 State of the art                                                        | 31 |

| 3.1.1 PLL-based CDR with an external reference clock                        | 31 |

| 3.1.1.1 CDR with frequency initialization                                   | 32 |

| 3.1.1.2 CDR with phase synthesis and phase interpolation                    | 33 |

| 3.1.2 PLL-based CDR without external reference clock                        | 34 |

| 3.1.3 Phase detector for serial data                                        | 35 |

| 3.1.3.1 Linear phase detector                                               | 35 |

| 3.1.3.2 Binary phase detector                                               | 37 |

| 3.1.3.3 Comparison of linear PD and binary PD                               | 41 |

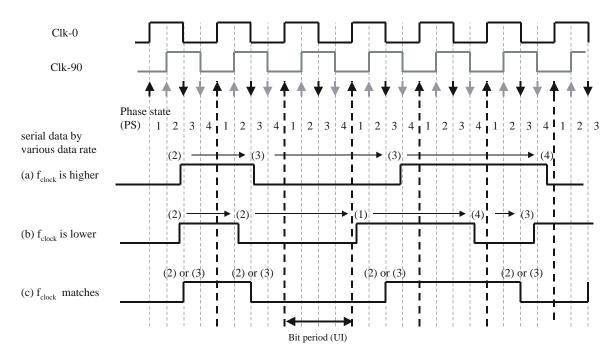

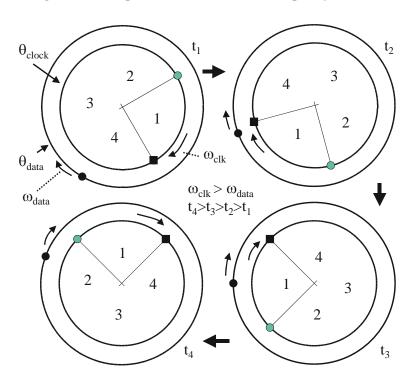

| 3.1.4 Frequency detector for serial data                                    | 42 |

| 3.2 CLOCK RATE REDUCTION ARCHITECTURE OF CDR                                | 46 |

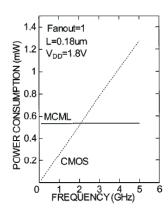

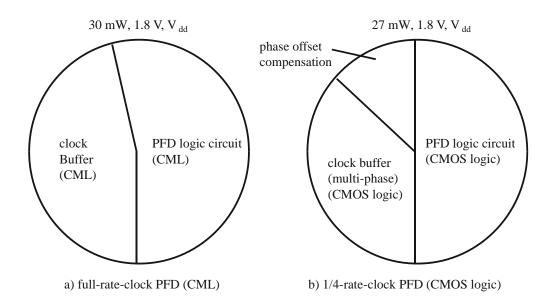

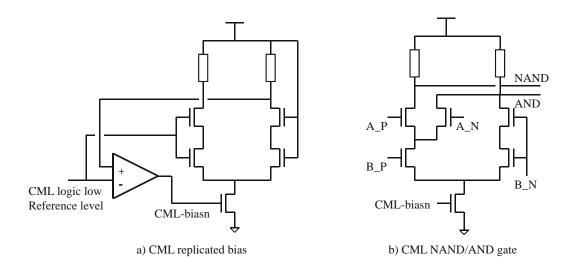

| 3.2.1 Comparison of current-mode logic (CML) and CMOS logic                 | 48 |

| 3.2.2 Comparison of a full rate and an 1/4-rate clock PFDs for CDRs         | 50 |

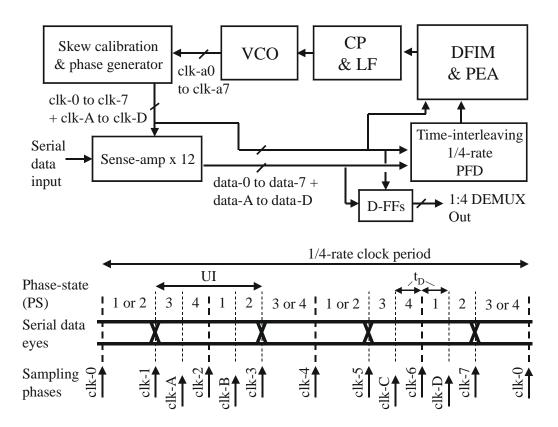

| 3.3 POWER EFFICIENT CDR WITH 1/4-RATE REDUCED-SAMPLING-PHASE TIME-          |    |

| INTERLEAVING PFD (PROPOSED IN THIS WORK)                                    | 52 |

| 3.3.1 Architecture                                                          | 52 |

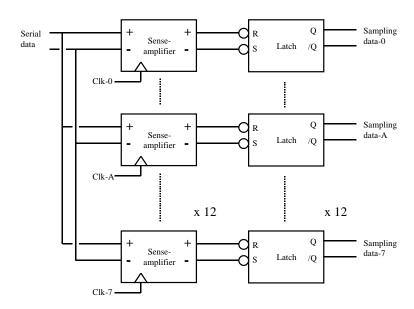

| 3.3.2 Building blocks                                                       | 54 |

| 3.3.2.1 Sense Amplifier                                                     | 54 |

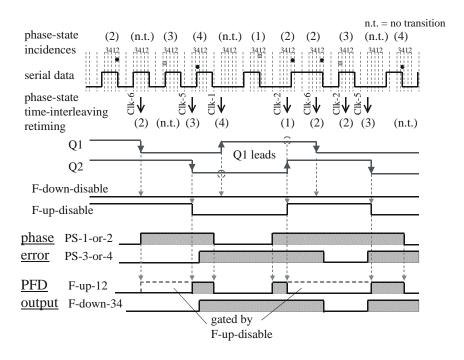

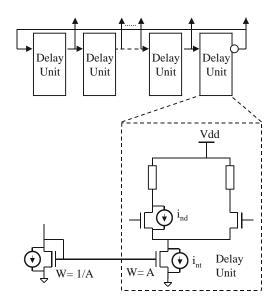

| 3.3.2.2 1/4-rate reduced-sampling-phase time-interleaving PFD               | 55 |

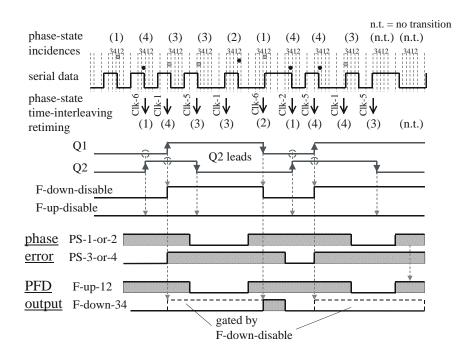

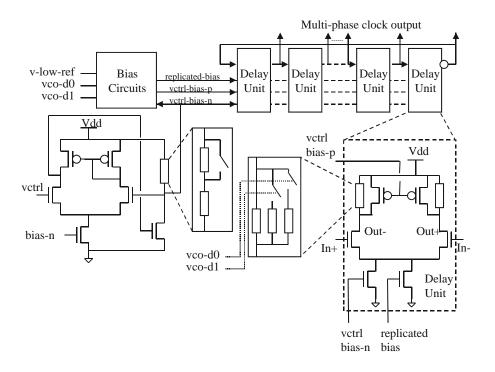

| 3.3.2.3 Voltage controlled oscillator (VCO)                                 | 60 |

| 3.3.2.4 Charge pump                                                         | 66 |

| 3.2.3 Loop bandwidth reduction technique in CDR using the divided frequence | су |

| impulse modulation technique (proposed in this thesis)                      | 68 |

| 3.2.4 Loop bandwidth design for jitter tolerance                            | 71 |

| 3.2.5 Simulation results                                                    | 73 |

| 3.2.6 Experiment results                                                    | 75 |

| 3.4 Summary                                                                 | 78 |

| 4 DESIGN OF PLL-BASED CLOCK-JITTER-FILTER                        | 79  |

|------------------------------------------------------------------|-----|

| 4.1 State of the art                                             | 79  |

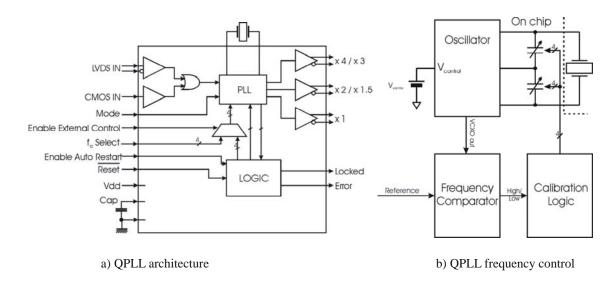

| 4.1.1 Quartz crystal based Phase-Locked Loop (QPLL)              | 79  |

| 4.2 PLL-BASED CLOCK-JITTER-FILTER WITH LC-VCO                    | 80  |

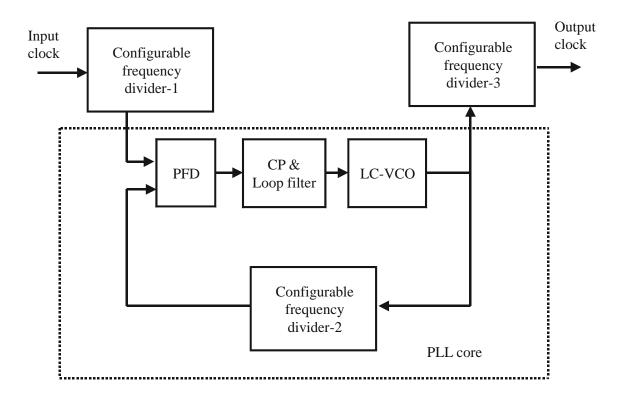

| 4.2.1 Architecture                                               | 81  |

| 4.2.2 Building blocks                                            | 82  |

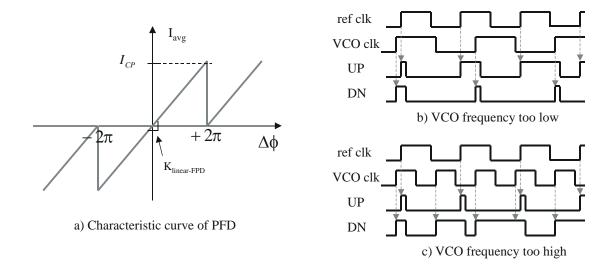

| 4.2.2.1 Phase frequency detector                                 | 82  |

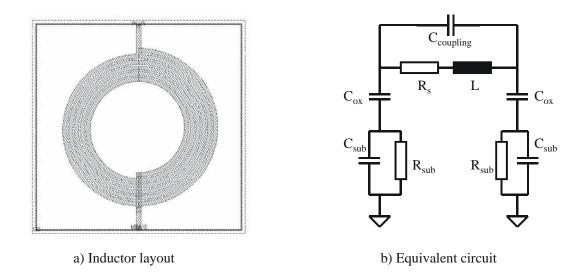

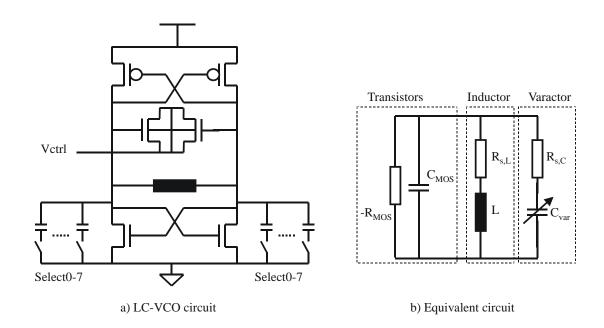

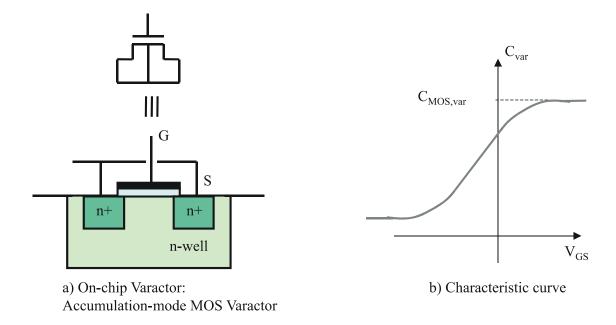

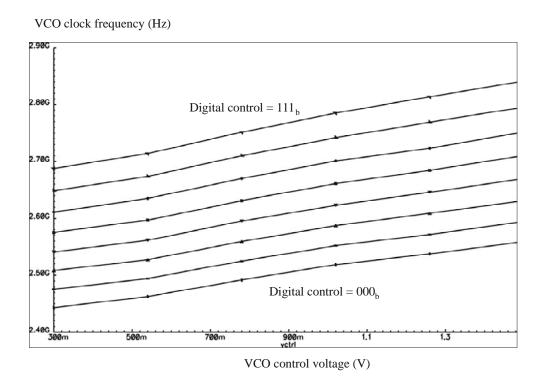

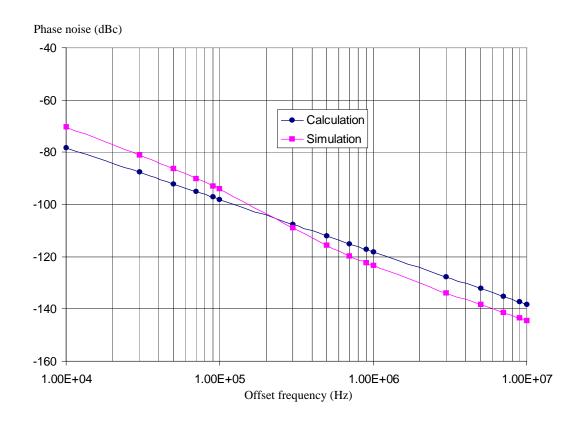

| 4.2.2.2 LC-VCO                                                   | 84  |

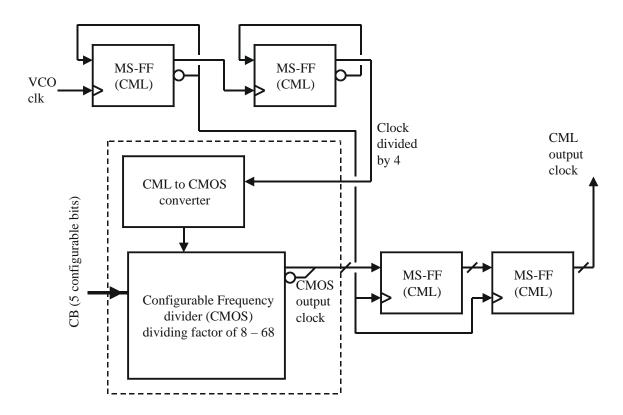

| 4.2.2.3 Frequency divider                                        | 89  |

| 4.2.2.4 Charge pump                                              | 93  |

| 4.2.3 Loop characteristic design                                 | 93  |

| 4.2.4 Simulation results                                         | 94  |

| 4.2.5 Experiment results                                         | 95  |

| 4.3 SUMMARY                                                      | 96  |

| 5 EXPERIMENTAL RESULTS OF THE 1/4-RATE CDR AND THI JITTER-FILTER | 99  |

| 5.2 Measurement results                                          | 100 |

| 5.3 SUMMARY                                                      | 103 |

| 6 CONCLUSIONS                                                    | 105 |

| 6.1 Future work                                                  | 107 |

| 7 APPENDICES                                                     | 109 |

| APPENDIX-A: 8B/10B CODING SYSTEM                                 | 100 |

| APPENDIX-B: DETERMINISTIC JITTER FROM BANDWIDTH LIMITATION       | 102 |

| APPENDIX-C: THE EFFECTIVE GAIN OF A DIGITAL PHASE DETECTOR       |     |

|                                                                  | 111 |

|     | APPENDIX-E: THE SAMPLING PHASES FOR FREQUENCY DETECTION IN CDR         | 125 |

|-----|------------------------------------------------------------------------|-----|

|     | APPENDIX-F: THE OUTPUT FREQUENCY OF THE CLOCK-JITTER-FILTER            | 127 |

|     | Appendix-G : The effect of loop resistor to peak-to-peak jitter of PLL | 129 |

|     | APPENDIX-H: THE PUBLICATION LIST IN FIGURE 3.7                         | 131 |

| 8   | LIST OF FIGURES                                                        | 135 |

| 9 ] | LIST OF ABBREVIATIONS                                                  | 139 |

| 10  | REFERENCES                                                             | 141 |

| C   | IIDDICIII IIM VITAE                                                    | 147 |

## **Abstract**

The high demanded data throughput of data communication between units in the system can be covered by short-haul optical communication and high speed serial data communication. In these data communication schemes, the receiver has to extract the corresponding clock from serial data stream by a clock and data recovery circuit (CDR). Data transceiver nodes have their own local reference clocks for their data transmission and data processing units. The reference clocks are normally slightly different even if they are specified to have the same frequency. Therefore, the data communication transceivers always work in a plesiochronous condition, an operation with slightly different reference frequencies. The difference of the data rates is covered by an elastic buffer. In a data readout system in the experiment in particle physics, such as a particle detector, the data of analog-to-digital converters (ADCs) in all detector nodes are transmitted over the networks. The plesiochronous condition in these networks are non-preferable because it causes the difficulty in the time stamping, which is used to indicate the relative time between events. The separated clock distribution network is normally required to overcome this problem. If the existing data communication networks can support the clock distribution function, the system complexity can be largely reduced. The CDRs on all detector nodes have to operate without a local reference clock and provide the recovered clocks, which have sufficiently good quality, for using as the reference timing for their local data processing units.

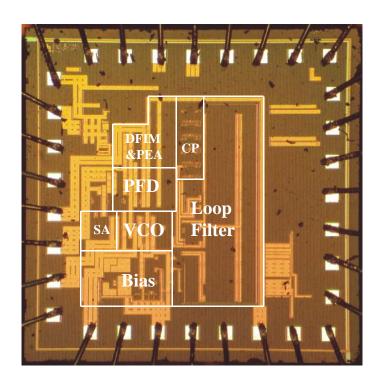

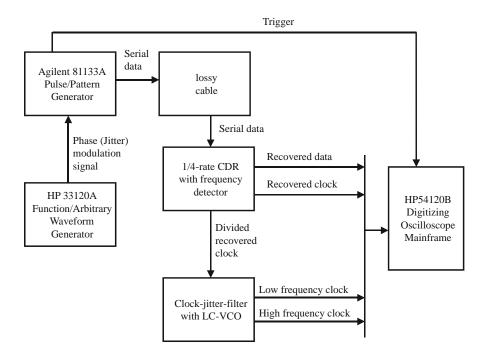

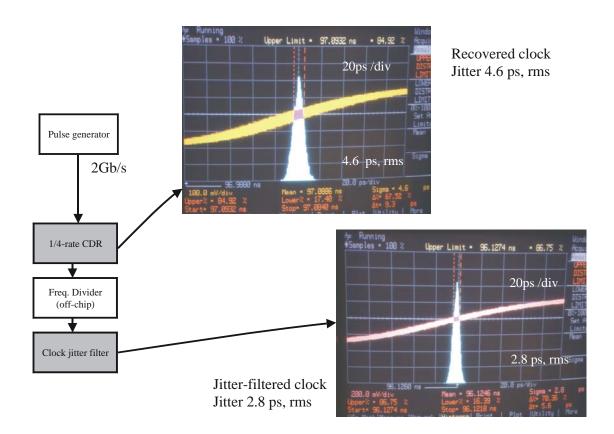

In this thesis, a low jitter clock and data recovery circuit for large synchronous networks is presented. It possesses a 2-loop topology. They are clock and data recovery loop and clock jitter filter loop. In CDR loop, the CDR with rotational frequency detector is applied to increase its frequency capture range, therefore the operation without local reference clock is possible. Its loop bandwidth can be freely adjusted to meet the specified jitter tolerance. The 1/4-rate time-interleaving architecture is used to reduce the operation frequency and optimize the power consumption. The clock-jitter-filter loop is applied to improve the jitter of the recovered clock. It uses a low jitter LC voltage controlled oscillator (VCO). The

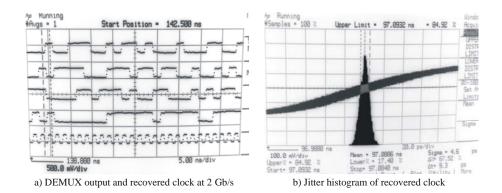

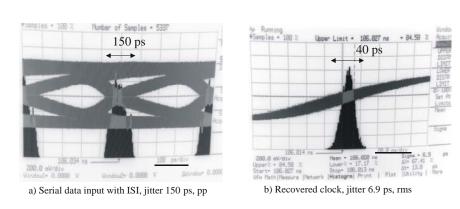

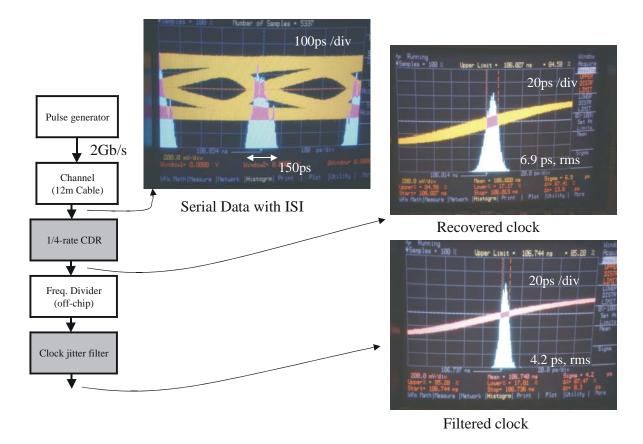

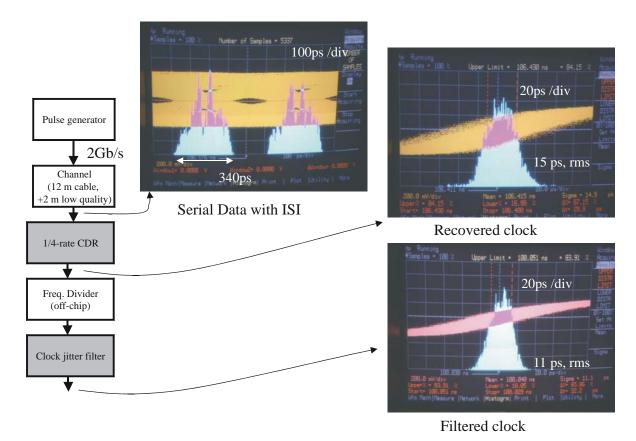

loop bandwidth of the clock-jitter-filter is minimized to suppress the jitter of the recovered clock. The 1/4-rate CDR with frequency detector and clock-jitter-filter with LC-VCO were implemented in 0.18µm CMOS Technology. Both circuits occupy an area of 1.61mm² and consume 170mW from 1.8V supply. The CDR can cover data rate from 1 to 2Gb/s. Its loop bandwidth is configurable from 700kHz to 4MHz. Its jitter tolerance can comply to SONET standard. The clock-jitter-filter has the configurable input/output frequencies from 9.191 to 78.125MHz. Its loop bandwidth is adjustable from 100kHz to 3MHz. The high frequency clock is also available for a serial data transmitter. The CDR with clock-jitter-filter can generate clock with jitter of 4.2ps rms from the incoming serial data with intersymbol-interference jitter of 150ps peak-to-peak.

## Kurzfassung:

## Gigabit pro Sekunde CMOS Takt- und Datenrückgewinnungsschaltungen mit geringem Jitter für grosse Synchronnetze

## **Einleitung**

Die hohen Anforderungen an den Datendurchsatz in Kommunikationssystemen können mit serieller Datenübertragung erfüllt werden. Eine hochratige Übertragung im Bereich von Gb/s ist möglich mit differentieller Signalübertragung. Der Spannungshub der Signale kann ebenfalls reduziert werden, da sie weniger Interferenzen erzeugt und toleranter gegenüber Gleichspannungseinkopplungen ist. Der Datendurchsatz pro Übertragungsstrecke kann so erhöht werden. Ebenso können die Einschränkungen durch die grosse Zahl von Verbindungen bei paralleler Übertragung überwunden werden. Trotz einer Punkt-zu-Punkt-Verbindung kann der Gesamtdurchsatz erhöht werden. Die Technik ist auch möglich bei Datenübertragung zwischen Modulen auf Platinenebene oder anderen Kurzstrecken mit Koaxialkabeln. Optische Kurzstreckenübertragung können weitere Distanzen überbrücken, da optische Fasern weniger Dämpfung ausweisen und weniger empfindlich gegenüber Einkopplungen sind. So können Übertragungsstrecken zwischen Gebäuden überbrückt werden. Die Daten werden ohne Takt übertragen, da ein zeitlicher Versatz zwischen Takt und Daten nicht verhindert werden kann. Im Empfänger wird der Takt durch eine Taktrückgewinnungsschaltung (CDR/Clock and Data Revocery circuit) aus dem Datenstrom zurückgewonnen. Der rückgewonnene Takt muss in Phase mit den Daten sein, um mit einer optimalen Abtastung der Daten eine niedrige Bitfehlerrate zu erreichen.

In einem seriellen Datentransceiver wird ein Hochfrequenztakt benötigt, um die parallel vorliegenden Daten zu serialisieren. Der Hochfrequenztakt wird von einem lokalen

Referenztakt abgeleitet. Die Taktrückgewinnungsschaltung im Empfänger erzeugt einen rückgewonnenen Takt synchron zum empfangenen Datenstrom. Dieser Takt wird zum Demultiplex der Daten und zur Wortsynchronisierung gebraucht. Mismatches der Datenraten sind unvermeidlich, da die Referenztakte der Transceiver nie ganz exakt übereinstimmen. Im Falle von PCI-Express Standard sind beispielsweise +/- 300ppm Unterschied zulässig. Im Empfänger führt der Unterschied zu einem Überlauf oder Leerlauf, je nachdem, ob der Senderreferenztakt zu hoch oder zu niedrig ist. Ein elastischer Puffer wird hier eingesetzt zur Vermeidung dieses Problems. Er erkennt einen Über- oder Leerlauf und entfernt oder addiert spezielle Symbole, um den Sendetakt an den Empfängertakt anzupassen. Alle Knoten in einem Kommunikationsnetzwerk arbeiten folglich mit leicht verschiedener Taktfrequenz. Dies ist solange kein Problem, wie keine präzisen Anforderungen an die Synchronisierung zwischen Knoten gestellt wird.

In Experimenten der Physik, wie in einem System zur Datenauslese in einem Teilchendetektor, werden die Ladungen, die als Ergebnis von Kollisionen aufgezeichnet werden, von Vorverstärkern und AD-Wandlern verarbeitet. Die digitalisierten Daten werden durch ein Kommunikationsnetz übertragen. Die werden verarbeitet und in Pakete gruppiert, bevor sie zur Weiterverarbeitung übertragen werden. Noch im Detektor erhalten sie einen Zeitstempel, um relative Zeitunterschiede der Ereignisse auswerten zu können. Die Verteilung eines Zeitsignals ist deshalb wichtig, um den Zeitstempel erzeugen zu können. Ein konventionelles serielles und optisches Übertragungsnetze mit einem eigenen Referenztakt in jedem Knoten kann hier nicht verwendet werden, sondern es wird ein separates Netz zur Verteilung des Zeitsignals benötigt. Wenn jedoch das existierende Datenübertragungsnetzwerk zur Synchronisierung des Zeitsignals verwendet werden kann, kann die Komplexität des Gesamtsystems stark reduziert werden. Hier ist deshalb das Datenübertragungsnetzwerk leicht verschieden von einem Konventionellen.

Wenn der im Empfänger zurückgewonnene Takt als Referenztakt für die Datenverarbeitung und -übertragung benutzt wird, kommt es nicht zu einem Unterschied der Taktfrequenzen zwischen Sender und Empfänger. Alle Knoten im Netzwerk haben dann den gleichen Referenztakt. Die Latenzen sind durch die Verbindungslängen definiert

und können durch eine Wortsynchronisierung ermittelt werden. Die Hauptaufgabe eines CDR in einem konventionellen Datenübertragungssystem ist die Rückgewinnung der Daten. Wichtigste Kenngrösse ist dann die Bitfehlerrate. Der Jitter des rückgewonnenen Taktes in veröffentlichen Schaltungen wird durch die verschiedenen Referenztakte stets vergrössert. Die meisten CDR brauchen zudem den lokalen Referenztakt, der im Sender ohnehin vorhanden ist. In einem System zur Übertragung des Daten- und Zeitsignals in einem ist es vorteilhaft, wenn der CDR ohne lokalen Referenztakt auskommt. Das System wird so effizienter. Insgesamt sollte der CDR demnach zur Datenrückgewinnung dienen und ebenfalls einen Takt mit niedrigem Jitter bereitstellen, der als Zeitsignal verwendet werden kann.

#### Stand der Technik

CDR-Schaltungen basierend auf PLLs finden häufig Verwendung, da sie leicht zu integrieren sind. In einer solchen PLL-basierten CDR-Schaltung werden die Phasenunterschiede des VCO-Taktes und der ankommenden Daten bei jeder Signalübergang bewertet. Nur der Phasenfehler kann bewertet werden, nicht jedoch ein vorhandener Frequenzunterschied. Eine PLL-basierte CDR mit nur einem Phasendetektor hat einen beschränkten Fangbereich, der von ihrer Schleifenbandbreite definiert wird.

Manche CDR verfügen über eine zusätzliche Phasenfangschleife, um die Frequenz der CDR mit Hilfe einer Frequenzmultiplikation des lokalen Referenztaktes in ihren Fangbereich zu bringen. Eine andere Möglichkeit besteht in einer Zweischleifentopologie, bestehend aus einem Taktsynthesizer und einer Phaseninterpolation. Die erste Schleife ausgehend vom Referenztakt einen Multiphasentakt, der von der zweiten Schleife durch Wahl der optimalen Abtastphase zur Synchronisierung der ankommenden Daten verwendet wird. Leichte Unterschiede in den Frequenzen werden durch ein fortwährendes Umlaufen der Abtastphase ausgeglichen. Beide Ansätze brauchen einen lokalen Referenztakt und führen zu hohem Jitter, wenn die Frequenzen nicht exakt übereinstimmen.

## Leistungseffiziente CDR-Schaltung: Viertelraten-CDR mit reduzierter redundanter Abtastung des Frequenzdetektors

Eine CDR mit eigenem Frequenzdetektor bietet einen erweiterten Fangbereich bei gleichzeitiger Einsparung eines lokalen Referenztaktes. Zudem kann die Schleifenbandbreite individuell angepasst werden. Ein bekanntes Verfahren zur Erkennung von Frequenzunterschieden bei zufälligen Daten ist die Quadrikorrelationstechnik (order Rotationalsfrequenzsdetektion), die zwei Gruppen von Phasenfehlern zwischen den seriellen Daten und den Quadraturtaktphasen verwendet. Der Frequenzunterschied kann durch Auswertung der Korrelation extrahiert werden. Verglichen mit einem Phasendetektor braucht ein Frequenzdetektor mehr Abtasttaktphasen. In CDR-Schaltungen mit einem Vollphasentakt muss der Phase-Frequenzdetektor(PFD) bei der vollen Datenrate arbeiten. Bei einer Datenrate von 2Gb/s bedeutet dies beispielsweise eine Operationsfrequenz von 2GHz. nur Current-mode-logic (CML) Verwendung finden kann. Leistungsverbrauch ist dann sehr hoch auf Grund der konstanten Stromaufnahme der CML-Schaltungen. Auch der Taktpuffer verbraucht viel Leistung.

Eine Architektur mit reduzierter Operationsfrequenz arbeitet mit Mehrphasentakten bei niedrigerer Frequenz, um die nötigen Samplephasen bereit zu stellen. In einer Architektur mit Halbratentakt wird beispielsweise ein 8-Phasentakt gebraucht. Diese 8 werden aufgeteilt in 2 Gruppen zu je 4 Phasen zur Phasen- und Frequenzdetektion. In einem Viertelraten-CDR werden bereits 16 Taktphasen gebraucht. Hiervon dienen 8 für den Phasendetektor und 8 für den Frequenzdetektion. Diese 8 Phasen für den Frequenzdetektion können zu 4 Phasen optimiert werden, da noch genug für die Erkennung einer Frequenzdifferenz gebraucht werden. Ein weiterer Vorteil eines Viertelraten-CDR ist die Möglichkeit, mit CMOS-Logik statt CML Leistung zu sparen. Zudem bildet der Viertelraten-CDR einen intrinsischen 1 zu 4-Demultiplexer, so dass der Deserializer für die Daten weniger Leistung braucht.

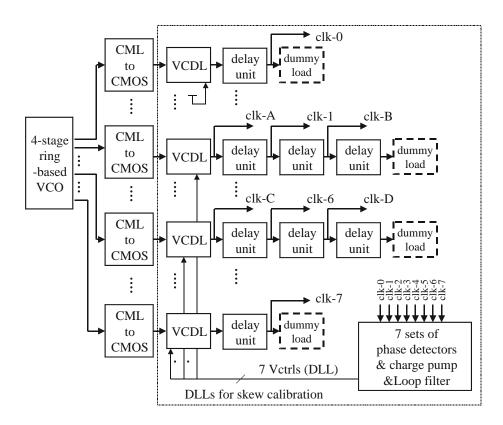

Der Multiphasentakt kann mit Hilfe eines Ringoszillators erzeugt werden. Differentielle Schaltungen werden hier verwendet, weil sie eine bessere Betriebsspannungsunterdrückung aufweisen. In jeder Der unvermeidliche Phasenoffset eines Multiphasentaktes, der die Qualität der CDR einschränken kann, kann durch geeignete Layout-Techniken minimiert werden. Eine Skew-Kalibrierung wird eingesetzt, um den Phasenoffset weiter zu verringern. Sie kostet etwas Leistung und Chipfläche, verbessert jedoch die Güte der CDR.

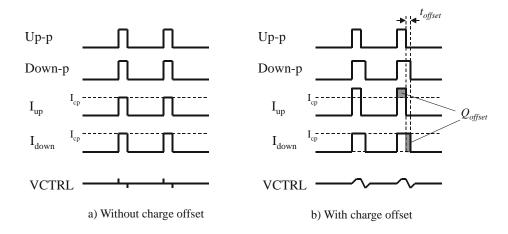

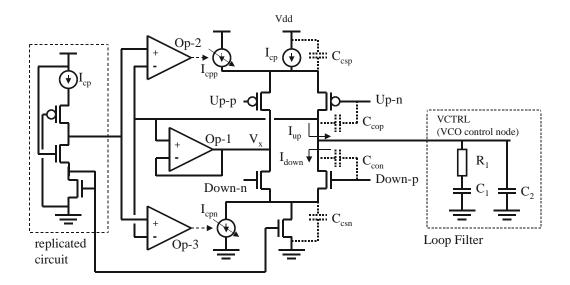

In dieser Arbeit kommt ein binärer Phasendetektor zum Einsatz. Seine Vorteile gegenüber einem linearen Phasendetektor ist die statistische Annäherung, so dass er unempfindlich gegenüber Pulsverzerrungen ist. Zudem werden die seriellen Daten automatisch regeneriert. Die Abtasteinheit zur Phasenfehlerdetektion hat die gleiche Funktion wie die Datenregeneration, so dass es hier kein Mismatch ihrer Abtasteigenschaften geben kann. In der Arbeit wird eine Tri-state-Charge pump mir einer Technik zur Reduktion der Ladungsteilung verwendet. Durch Verfolgung des Arbeitspunktes der Charge pump wird eine Offsetkompensation erreicht. Bei der Einstellung der Schleifenbandbreite wird eine Technik zur Verringerung der Bandbreite verwendet. Ein Teilerfaktor und die Fehlerakkumulation erweitern die Einstellmöglichkeiten um einen weiteren Parameter.

## PLL-basierte Taktjitterfilter mit einem LC-VCO

Der ankommende serielle Datenstrom enthält Jitter vom Übertragungskanal. Die CDR muss in der Lage sein, den Phasenfehler zu verfolgen. Der rückgewonnene Takt hat nicht zwangsläufig einen kleineren Jitter, wenn er auch zur Datenerkennung ausreicht. Als Referenztakt kann er so nicht verwendet werden. Aus diesem Grund wird ein Taktjitterfilter benötigt. Eine Quarz-PLL (QPLL) verwendet einen Quarzoszillator als VCO, bei dem die Frequenz über die kapazitive Last gesteuert wird. So kann der Taktjitter gefiltert werden bis hin zu Frequenzen im Bereich von 100MHz. Für serielle Datenübertragung muss der Hochfrequenztakt von einer anderen PLL erzeugt werden. Der PLL-basierte Taktgenerator hat ebenfalls eine Filterfunktion bezüglich des Taktjitters. Sie können demnach kombiniert werden. Für einen Hochfrequenztakt bieten LC-VCOs sich wegen ihres niedrigen Jitters an, zumal mit Spulen auf dem Chip eine

integrierte Lösung möglich ist. Ein PLL-basierter Taktjitterfilter kann den Hochfrequenztakt für den Transceiver erzeugen und gleichzeitig einen Takt im mittleren Frequenzbereich für Datenverarbeitung oder AD-Wandler im Detektorknoten.

Beim Entwurf eines LC-VCO wird die Steilheit der VCO-Kurve reduziert, um die Jitterempfindlichkeit zu verringern. Der Einstellbereich der Frequenz kann dennoch erweitert werden durch eine Umschaltung mit Hilfe von Konfigurationsbits, die kapazitive Belastungen zuschalten. Die Frequenzeinstellung verläuft mit Hilfe eines On-Chip-Varaktors. Die Steuerspannung des Schleifenfilters wird gepuffert, um eine Rückwirkung vom VCO zu minimieren. Eine Tri-state Charge pump mit den identischen Techniken wie im CDR zur Reduktion von Ladungsteilung und Ladungsoffset findet Verwendung. Beim Phasenfrequenzdetektor handelt es sich um ein Standarddesign mit 2 Latches und einem Rückkoppel-Reset. Die Frequenzteiler werden im Rückkoppelpfad und im Taktausgang verwendet. Um Leistung zu sparen, laufen die Taktteiler bei einem Viertel der VCO-Frequenz, wodurch sie als CMOS-Logik implementiert werden können. Der Ausgangstakt wird abschliessend synchronisiert durch den Hochfrequenztakt, um den Jitter des Taktteilers und der Logik zu eliminieren.

## Messergebnisse

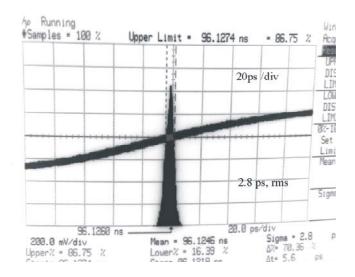

Die Viertelraten-CDR mit reduzierter redundanter Abtastung des Frequenzdetektors und PLL-basierte Taktjitterfilter mit einem LC-VCO wurden in einer 0,18um-CMOS-Technologie auf separaten Testchips implementiert. Der CDR mit 1-zu-4-DEMUX ist 0,79mm² gross und verbraucht 80mW bei 1,8V Betriebsspannung. Er deckt einen Bereich von 1 bis 2Gb/s ab. Bei seriellen Daten mit kleinem Jitter hat er einen RMS-Jitter von 4,6ps. Die Schleifenparameter sind konfigurierbar, die Schleifenbandbreite kann von 700kHz bis 4MHz eingestellt werden. Die SONET-Jittertoleranzanforderungen werden eingehalten. Der Frequenzfangbereich ist grösser als 100MHz. Der PLL-basierte Taktjitterfilter mit LC-VCO nimmt eine Fläche von 0,82mm² ein bei einem Leistungsbedarf von 90mW bei VDD=1,8V. Seine Eingang- und Ausgangstaktfrequenz reichen von 9.191MHz bis 78.125MHz. Die Schleifenparameter sind ebenfalls

konfigurierbar. Die Schleifenbandbreite kann von 100kHz bis 3MHz eingestellt werden. Der Ausgangsjitter hat einen Minimalwert von 2,8ps.

Beide, die Viertelraten-CDR und das Taktjitterfilter wurden ebenfalls zusammen getestet. Bei einem seriellen Datenstrom mit emuliertem pp-Jitter von 150ps liegt der Ausgangsjitter des Taktjitterfilters bei 4,2ps rms.

## Zusammenfassung

In einem grossen synchronen Netzwerk zur Messung von Zeitdaten ist ein separates Taktverteilungsnetz stets nötig. Wenn der Zeittakt durch das Datennetzwerk verteilt werden kann die Komplexität des Netzwerks deutlich reduziert werden. Die Schlüsselkomponente für die Technik ist eine Schaltung Datenrückgewinnung. Die Qualität des rückgewonnenen Taktes muss hoch genug sein, um als Referenztakt dienen zu können. Die CDR mit Frequenzdetektor und Taktjitterfilter kann diese Anforderungen erfüllen. Die CDR hat einen erweiterten Frequenzfangbereich und kann ohne lokalen Referenztakt auskommen. Die Viertelratenarchitektur reduziert die Leistung, da ihr PFD in CMOS-Logik implementiert werden kann. Zudem können die zusätzlichen Abtastphasen für die Frequenzdetektion reduziert werden. Die Viertelraten-CDR ist automatisch auch ein 1-zu-4-DEMUX. Die Leistungsaufnahme des Deserializers wird so reduziert. Das Taktjitterfilter mit LC-VCO erzeugt nicht nur einen Takt mit niedrigem Jitter bei mittleren Frequenzen, wie dies AD-Wandler benötigen, sondern auch einen Hochfrequenztakt für serielle Datenübertragung. Die Viertelraten-CDR mit Frequenzdetektor und Taktjitterfilter in 0,18um-CMOS bietet eine Datenrückgewinnung und einen Referenztakt mit niedrigem Jitter.

## Chapter 1

## Introduction

### 1.1 Motivation

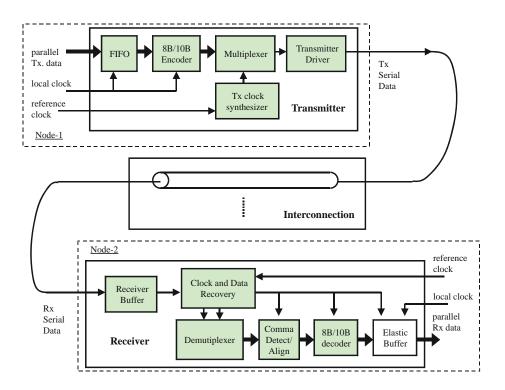

Figure 1.1 Serial data communication system

Optical communication and high speed serial data communication support high demand of data throughput in data networks from global to sub-system level. Optical data communication is applied in long-haul data network for Internet or data highway. It also serves for short-haul interconnections such as interconnections from building to building.

The high speed serial data communication covers large size network to data communication inside small system. It gradually replaces parallel data interface that has a physical limitation by its extremely large number of ports and interconnections for high data throughput.

Figure 1.1 shows the data transmission in serial data communication system. Parallel data are encoded, serialized and transmitted as a serial data stream. Data can be transmitted by higher data rate because of low swing differential signaling. Hence, the physical limitation in parallel data interface can be overcome because a high data throughput can be achieved by a smaller number of ports. For data serialization, a required high frequency clock is generated from a low frequency local reference clock by a clock synthesizer. It is used in a high speed data multiplexer to generate a serial data stream. The serial data are transmitted over transmission lines and cables by a high data rate transmitter driver. In order to avoid clock-data-skew, the serial data are transmitted solely. A corresponding clock is extracted at receiver by a clock and data recovery circuit (CDR). The recovered clock is used in data regeneration, demultiplexing, comma detection/alignment and 8B/10B decoding. Basically, the receiver node has its own local reference clock. It rarely has the exact frequency to the reference clock in the transmitter node. They are normally specified to be within a tolerance. In PCI Express standard, their reference frequencies are specified to be different within +/- 300 ppm. Therefore, an elastic buffer is applied to handle the difference of the reference frequencies. The front-ended blocks in the receiver are synchronous to the incoming serial data. They are depicted as shaded blocks in Figure 1.1. The mismatch of the reference frequencies leads to data overflow/underflow, if the reference frequency in the transmitter node is higher/lower respectively. The elastic buffer observes data overflow/underflow and removes/inserts the special symbol to make the data flow match to the reference frequency in the receiver node. This means that all nodes in the data communication networks operate in a plesiochronous mode, an operation with slightly different reference frequencies. This kind of operation will well function if timing precision in each data node is not critical.

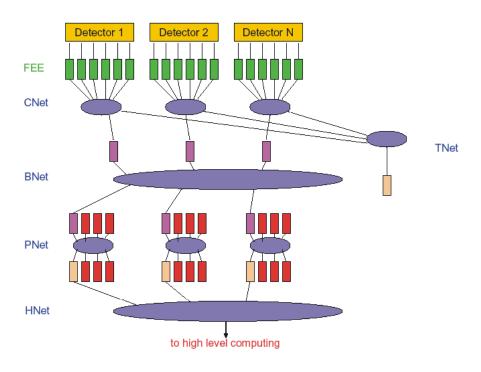

Figure 1.2 The data readout networks in particle physics experiment

Figure 1.2 depicts the data readout networks of the particle detectors in a particle physics experiment. The particles, resulting from collisions, are converted to electrical signals in detectors. The signals are transformed to digital data by charge-amplifiers and analog-to-digital converters in front-ended electronic units (FEE). The data from the front-ended electronic units are collected by Concentrator Network (CNet) and further framed and processed in Build Network (BNet), Processing Network (PNet), and High-level Network (HNet) for the high level computing. The concentrator network operates not only as a data collector but also as a data selector in order to minimize the required data throughput of the networks. Moreover, it also operates as a time distributor for the front-ended electronic units. The time distribution is important for the time stamps of events on detectors. Therefore, the information is not only the readout data but also the relative times of the events [1]. In the conventional serial data communication networks, each node has its own local reference clock. It can be used for data collection but not for time distribution. Therefore, a separate time distribution networks are required. If the existing data networks can provide timing function, the system complexity can be largely reduced. Consequently,

the data communication networks in this synchronous data readout system are slightly different from the standard ones.

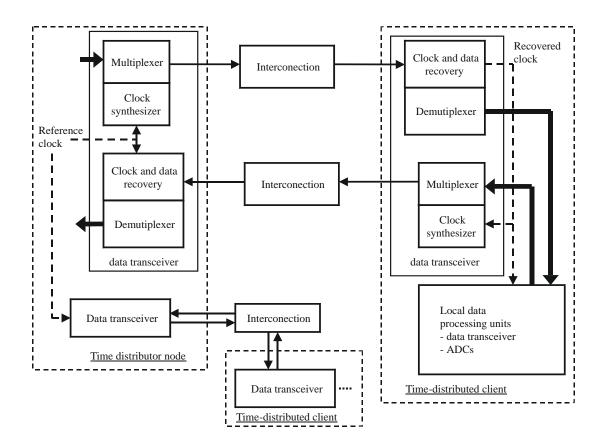

Figure 1.3 The data communication networks for time and clock distribution

The data communication networks for time and clock distribution are shown in Figure 1.3. Only the time distributor node has a local reference clock. The local reference clock in other nodes, time-distributed clients, are replaced by the recovered clocks from CDRs. They are used as the reference clocks for data transmission and data processing units such as analog-to-digital converters in the client nodes. Therefore, there is no plesiochronous condition like in the standard data networks. Hence, the elastic buffer is not required. The key to achieve this concept is a low jitter clock and data recovery circuit because the recovered clock has to be used as a reference frequency. For that reason, a good quality of the recovered clock is required. The CDR for time and clock distribution has to fulfill both requirements of data recovery and of precise reference clock.

The CDR for time and clock distribution has to operate without local reference clock. Therefore, the CDR must have a wide frequency capture range. This can be provided by a rotational frequency detection technique. The additional sampling phases are required but the CDR can have frequency capture range larger than its loop bandwidth. Consequently, it can have a wide frequency capture range and its jitter transfer function can be independently adjusted. In order to improve jitter quality, the clock-jitter-filter is applied to reduce the jitter of the recovered clock. It can also reduce jitter accumulation, if the time-distributed client nodes further distribute the reference frequency.

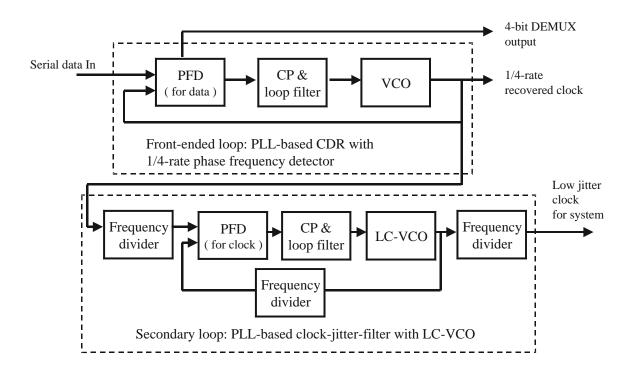

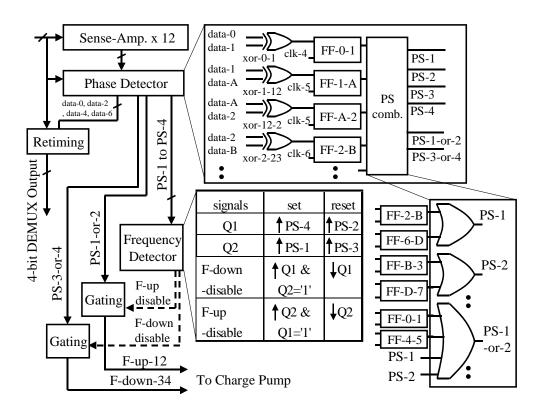

Figure 1.4 The block diagram of CDR for time and clock distribution

The block diagram of CDR for time and clock distribution proposed in this thesis is shown in Figure 1.4. The clock rate reduction technique is applied at the front-ended CDR. The CDR as an intrinsic 1-to-4 demultiplexer can reduce the power consumption of the entire deserializer. The sampling phase for frequency detection can be optimized in order to improve its efficiency. In the Phase-Locked-Loop-based (PLL-based) clock-jitter-filter, the low jitter LC-Voltage-Control-Oscillator (LC-VCO) is used and the loop bandwidth is minimized to suppress the jitter of the recovered clock. The front-ended loop with 1/4-rate

CDR provides data recovery function while the clock-jitter-filter improves the quality of the recovered clock. It can fulfill the requirement of CDR for time and clock distribution.

## 1.2 Scope and organization

An adequate time measurement protocol is required to obtain the relative times of the events in different data readout nodes in a detector. It has to quantify the interconnection delay and the delay of front-ended electronics. However, this thesis is focused on the design of the crucial component for time synchronization. The organization of a complete relative time measurement system is not covered in detail.

This thesis is organized in the following way. The design consideration of the CDR for time and clock distribution is discussed in chapter 2. The specification for CDR is explained. The jitter sources in serial data communication system are defined and analyzed. The characteristic of PLL-based CDR and clock synthesizer are discussed. The 2-loop CDR architecture is purposed and the design goal of CDR for timing reference distribution is specified. In chapter 3, the design of the front-ended loop, PLL-based CDR, is described. The state of the art of CDR in standard serial data communication system is summarized. The various types of CDR are discussed and the rotational frequency detection technique in CDR is explained. The proposed power efficient CDR with reduced-sampling-phase timeinterleaving 1/4-rate phase frequency detector is presented in this chapter. The architecture and the design considerations of its building blocks i.e. phase detector, frequency detector, VCO, charge pump, and the proposed loop bandwidth reduction technique are discussed in detail. The corresponding simulation and experiment results of the 1/4-CDR are shown. In chapter 4, The design of the secondary loop, PLL-based clock-jitter-filter with low jitter LC-VCO is discussed. The design issues of its building blocks: phase/frequency detector, LC-VCO, and frequency divider, are explained. The clock-jitter-filter is optimized to have a low jitter generation. The simulation and experimental results are presented in this chapter. In chapter 5, the experimental results of the two-loop CDR for time and clock distribution implemented in 0.18µm CMOS Technology is shown. The conclusion of this thesis and the future work are presented in chapter 6.

## Chapter 2

## Design considerations of CDR for time and clock distribution

### 2.1 Introduction

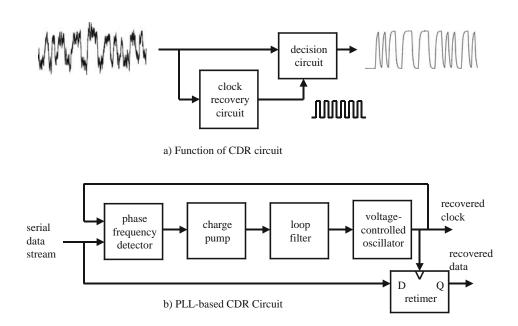

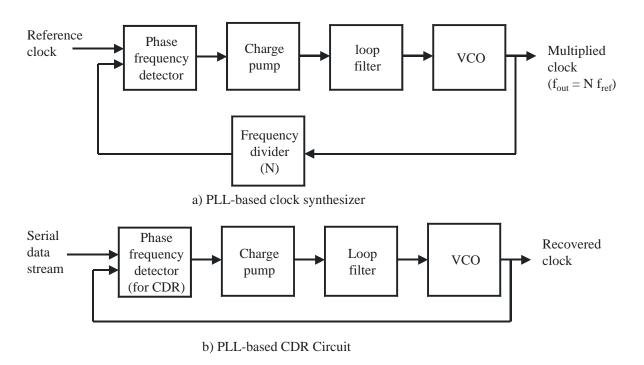

Figure 2.1 The function and basic block diagram of CDR

The specifications of CDR in standard serial data communication will be discussed in this chapter. In order to specify the requirement of CDR for time and clock distribution, the jitter sources in the serial data communication have to be analyzed.

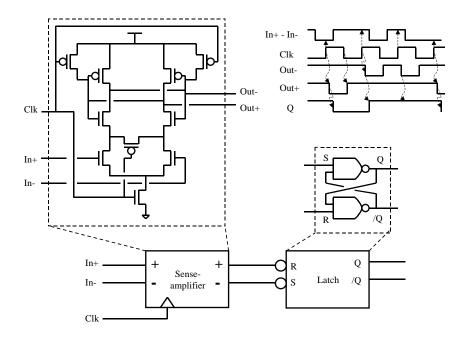

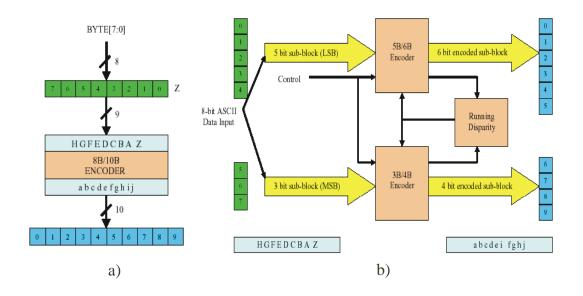

In serial data communication at high bit rates, differential signaling is a common feature. It has smaller signal voltage swing and better common-mode noise rejection than single-ended signaling. Clock and data skew is rather problematic because the unit interval (UI) is small at high data rates. Consequently, only serial data are transmitted and the corresponding clock is recovered at the receiver, as shown Figure 1.1. The 8b/10b coding scheme is always applied in the serial data for two main reasons. The first is to remove the dc-component from serial data stream, allowing the transmission over ac-coupled connections. The second reason is to assure sufficient data transitions for CDR to recover clock from the serial data. The PLL-based CDR is widely used because it is suitable for monolithic integration. The function and basic block diagram of CDR is depicted in Figure 2.1 a) and b) respectively. The CDR generates the required clock for data regeneration, as in Figure 2.1 a). The clock is generated by a VCO which its phase and frequency are regulated by using the averaged phase error from a phase detector (PD) and loop filter (LF). The specifications of CDR will be briefly described in the following.

## 2.2 CDR specifications

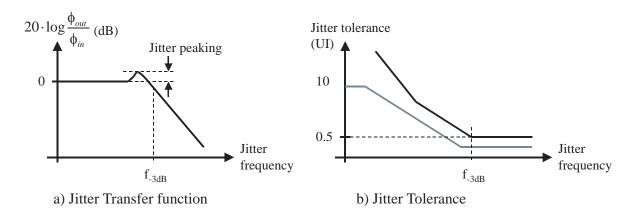

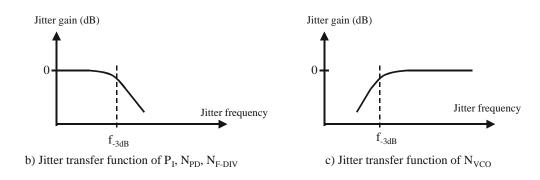

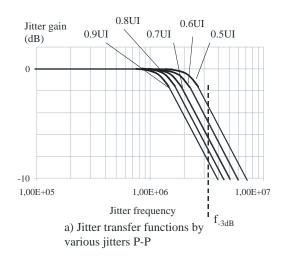

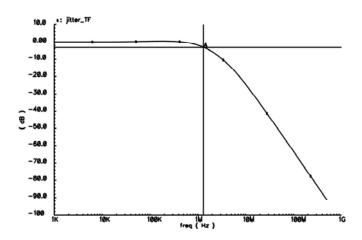

#### 2.2.1 Jitter transfer function

Jitter transfer function relates to the transfer function of the jitter output in the recovered clock to the jitter input in serial data by various frequencies. It defines the loop bandwidth or closed-loop response of CDR. It is considered as low-pass filter, as shown in Figure 2.2 a). The quantitative design can be done by a PLL linear model, that will be discussed in section 2.4.1.

#### 2.2.2 Jitter peaking

Figure 2.2 CDR specifications

In a phase-locked loop, a peak can appear around the corner frequency of the closed loop response depending on the loop damping factor, Figure 2.2 a). The jitter peak causes errors in data regeneration. Therefore, it is normally specified to be less than 0.1 dB.

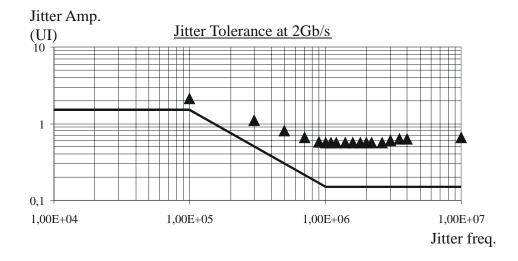

#### 2.2.3 Jitter Tolerance

Jitter tolerance describes the maximum jitter amplitude of incoming serial data, which the CDR can operate without error or with an extremely small error rate, e.g.  $10^{-12}$ , at various jitter frequencies. The jitter tolerance mask in SONET is shown as a grey line in Figure 2.2 b). The black line depicts the jitter tolerance of a qualified CDR. It can usually tolerate higher jitter amplitude than specified by the jitter tolerance mask. Normally, a CDR has to allow for large jitter amplitudes at low frequencies to support a plesiochronous operation, in which the clock frequency of the CDR is slightly different from the incoming serial data stream. In this condition, phase wandering occurs and it is considered as a low frequency jitter. The CDR should be able to track it.

According to its jitter transfer function, the low frequency jitter in serial data appears at the CDR recovered clock. It means the clock phase can follow low frequency jitter inside its loop bandwidth, even if it is larger than a unit interval. Incoming jitter at high frequencies outside CDR loop bandwidth is suppressed. The CDR cannot follow the high frequency

jitter of the incoming serial data, therefore it tolerates only a smaller jitter amplitude. The jitter tolerance of CDR has the same corner frequency as that of the jitter transfer function, f<sub>-3dB</sub>. Therefore, a trade-off in the CDR design is required in order to meet both specifications.

#### 2.2.4 Jitter generation

Jitter generation means the jitter produced by the CDR itself, when input data contains no jitter. The jitter sources in PLL-based CDR are VCO phase noise, interference, and supply/substrate noise. The jitter in CDR can be categorized into two types: random jitter and deterministic jitter. The random jitter comes from device noise such as thermal noise in transistors or resistors. Deterministic jitter is periodic and has finite value. It is caused by the circuit operation such as supply/substrate noise. Any offset voltages or mismatch of devices can degrade the performance and cause deterministic jitter. A careful circuit and layout designs can reduce the jitter generation.

## 2.3 Jitter in serial communication system

The jitter sources in serial communication system have to be analyzed, in order to specify the requirement of the CDR for clock and time distribution. They can be classified into 3 types, i.e. transmitter jitter, channel jitter, and receiver jitter.

### 2.3.1 Transmitter jitter

The high frequency clock for data serialization and the data buffer are the main contributions of the transmitter jitter. The high frequency clock is normally generated by a PLL-based clock synthesizer. Its block diagram is shown in Figure 2.9 a). The dominant jitter sources in PLL are the phase noise of its reference clock and of VCO. They affect the PLL output clock in different ways. The reference clock phase noise has a low-pass transfer function, while the VCO phase noise has high-pass transfer function at the same corner frequency. Therefore, the loop characteristic has to be optimized regarding to the jitter quality of the VCO and of the reference clock. The reported clock synthesizers use an on-

chip low jitter LC-VCO and a low jitter reference clock. They can provide the high quality clock with jitter less than 1ps rms [2][3]. The jitter contributions of the building blocks in PLL will be discussed in section 2.4.2. The design of a PLL-based clock synthesizer as a clock-jitter-filter will be discussed in Chapter 4.

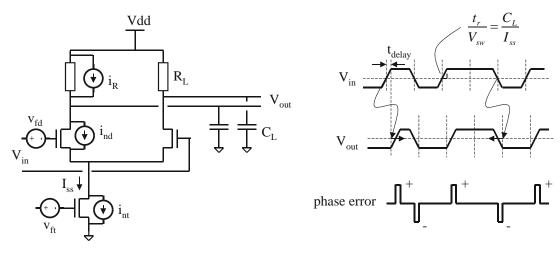

High data rate buffers are usually realized in a differential circuit topology, because common-mode noise rejection is improved comparing with the single-ended data buffers. The supply and substrate noise induced jitter is well rejected. Figure 2.3 a) shows the device noise sources in a differential serial data buffer. The jitter contributed by device's thermal noise in data buffer is analyzed in [4]. It can be calculated by

$$\Delta t_{d-buff,rms} = \sqrt{\frac{kT \cdot C_L}{2}} \cdot \frac{\xi}{I_{ss}}$$

Eq. 2.1

where  $\Delta t_{d\text{-}buff,rms}$  is the root-mean-square of the jitter from the device's thermal noise in data buffer, k is the Boltzmann constant, T is the absolute temperature,  $C_L$  is the output capacitive load,  $I_{ss}$  is the data buffer tail current, and  $\xi = \sqrt{1 + (2/3) \cdot a_v}$  is the noise contribution factor, where  $a_v$  is the data buffer gain. Only jitter from thermal noise is considered in this equation. The jitter contribution by thermal noise in the output driver with this following parameters: the characteristic impedance of 50 ohm, the output voltage swing of 400mV, the capacitive load of 500fF from the bonding pad capacitor and 1.5pF from the effective parasitic capacitor of interconnection, and the voltage gain of one, can be calculated by Eq. 2.1 to be 0.022ps rms. This value is relatively small compared to the jitter contributed by PLL-based clock synthesizers. Therefore, it is normally neglected in the well-designed data buffer.

a) Device noises in data buffer

b) Phase error induced by offset voltage

Figure 2.3 Device noise in the data buffer

The jitter contributed by flicker noise dominates at low frequency. The flicker noise of transistor can be calculated by

$$v_{flicker-nosie}^2 = \frac{K_f}{W \cdot L \cdot C_{ox} \cdot f}$$

Eq. 2.2

where  $v_{flicker-noise}$  is the amplitude of flicker noise,  $K_f$  is the empirical coefficient for flicker noise, W is the width of transistor, L is the length of transistor,  $C_{ox}$  is the specific capacitor of MOS transistor, and f is the noise frequency. The flicker noise has high amplitude at the low frequency, therefore the flicker noise in switch transistors can be visualized as an offset voltage in the data buffer. For instance, the contribution of flicker noise between 1Hz to 0.001Hz from the transistor with W=10 $\mu$ m, L=0.2 $\mu$ m, and  $C_{ox}$  of 8fF/ $\mu$ m<sup>2</sup> can be calculated by Eq.2.2 to be 19 $\mu$ V. It is relatively small compared to the offset voltage contributed by mismatch properties of transistors in the differential circuit. This induces an offset voltage in the milli-volt range.

The effect of the offset voltage in the data buffer is depicted in Figure 2.3 b). The offset voltage from the mismatch and thermal noise of the switch transistors influence the rising and falling edges of the serial data in the opposite way. If offset voltage makes the threshold crossing time of the data rising edge late, it will make the threshold crossing time

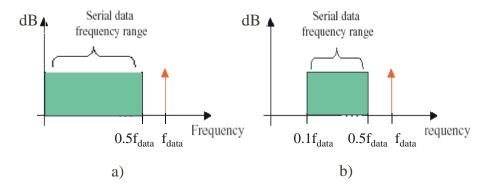

of the data falling edge early, which results in a data duty cycle distortion. The phase errors of the rising and falling edges are in the opposite direction by the same amplitude. Therefore, the offset voltage of the data buffer is converted to high frequency phase errors. Normally, the serial data are encoded by the 8B/10B coding scheme with a longest five identical successive bit sequence, described in Appendix-A. Therefore, the frequency range of jitter induced by the offset voltage of the data buffer can be written as

$$\frac{f_{data-rate}}{10} < f_{jitter-offset} < \frac{f_{data-rate}}{2}$$

Eq. 2.3

where  $f_{data-rate}$  is the data rate frequency,  $f_{jitter-offset}$  is the frequency range of jitter induced by the offset voltage of the data buffer. The jitter amplitude can be calculated from

$$\Delta t_{d-buff,offset} = \frac{2 \cdot C_L \cdot v_{offset}}{I_{ss}}$$

Eq. 2.4

where  $\Delta t_{d-buff,offset}$  is the peak-to-peak jitter caused by the offset voltage,  $v_{offset}$  is the offset voltage of the data buffer,  $C_L$  is the output capacitive load, and  $I_{ss}$  is the tail current of a differential data buffer. In Eq. 2.4,  $C_L$  divided by  $I_{ss}$  is interpreted as the slew rates of the rise or fall times at the output nodes. Jitter induced by the offset voltage will be reduced if the transition time becomes smaller. It can be achieved by increasing the tail current or reducing the capacitive load by minimizing the up-scaling factor in data buffer chain. For instance, the rise/fall times of the serial data buffer chain for driving output pads can be improved by using a up-scaling factor of 2 instead of 2.7 or 3. It make the data buffer has longer delay time. However, the total delay of the serial data buffer chain is normally not critical.

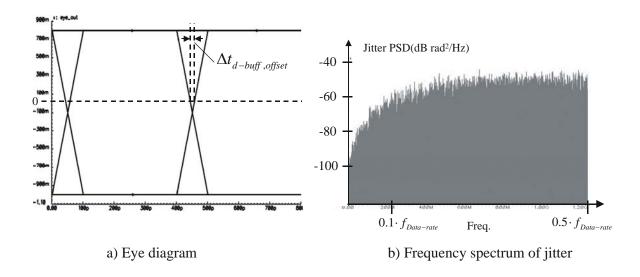

Figure 2.4 shows the simulated power spectrum of the phase error induced by offset voltage of the data buffer. The data transitions occur randomly depending on the transmitted data pattern, therefore the pseudo-random binary bit sequence  $2^{23}$ -1 encoded with 8B/10B coding scheme is used in the simulation. The offset voltage in data buffer in this simulation is 100mV. The phase error power spectra at frequency band as predicted in Eq. 2.3 can be observed.

Figure 2.4 The phase error induced by the offset voltage in data buffer

The flicker noise in the tail current transistor affects the delay time of the data buffer by its current variation. However, the area of the tail current transistor is typically large and the bias node usually possesses relative large capacitive load. Therefore, its contribution can be neglected.

The reported monolithic serializers [2][3] using on-chip LC-VCO and careful design of CML output buffers can provide serial data with jitter less than 10ps P-P.

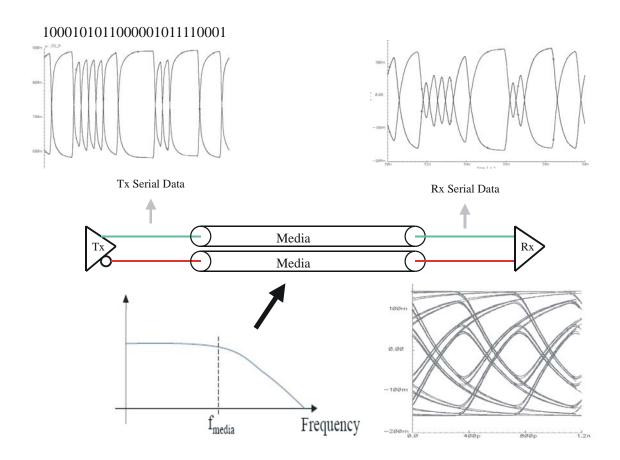

#### 2.3.2 Channel jitter

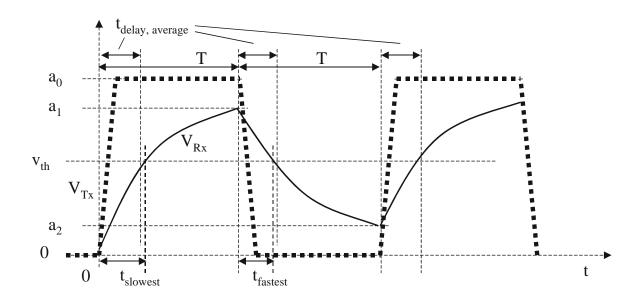

The serial data is transmitted over the channel media like coaxial cable or interconnection on PCB. The interconnections have more loss at high frequency. Therefore, the characteristic can be modelled as a low-pass filter. The inaccurate interconnection termination and the inhomogeneous impedance from connectors, bonding wires, and soldering points also contribute to the parts of the channel jitter. However, the jitter from the bandwidth limitation still dominates, therefore, it is the main focus in this section. The data transmission through the bandwidth limitation channel is shown in Figure 2.5. If the corner frequency of the interconnection,  $f_{media}$ , is lower than the highest dominant frequency component of the serial data, which is half of the data rate for non-return-to-zero

data, it will make the data amplitudes different by various data patterns. The corresponding jitter occur on the data eye-diagram, so-called data dependent jitter (DDJ) or inter-symbol-interference (ISI).

Figure 2.5 Channel Jitter

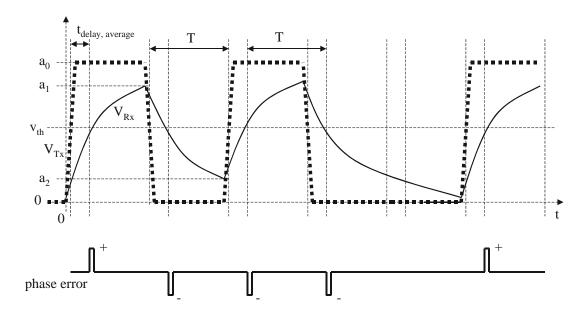

If the interconnection bandwidth is not high enough for the data rate, data bit can not reach the complete logic level as depicted in Figure 2.6. The ideal transmitted signal,  $V_{Tx}$ , is represented as dashed line while the signal at the receiver of the interconnection,  $V_{Rx}$ , is depicted in solid line. The rise time of  $V_{Rx}$  is limited by the interconnection bandwidth. If there is a data transition in the next bit,  $V_{Rx}$  reaches its peak at  $a_1$  and starts falling.  $V_{Rx}$  reaches the logic threshold voltage,  $v_{th}$ , faster. Hence, the threshold crossing times vary.  $V_{Rx}$  starts falling from the signal level  $a_1$  and cannot reach the complete logic level if a data transition occurs in the following bit. Therefore, the next threshold crossing is also fast, which is depicted as negative phase error.  $V_{Rx}$  will not reach the complete logic level again,

if there are data transitions in the following bits, resulting in the fast threshold crossings. If identical successive bits occur,  $V_{Rx}$  has enough time to approach the complete logic level, therefore the threshold crossing of the following transition is slow, which is depicted as a positive phase error.

Figure 2.6 The detail of data-dependent jitter

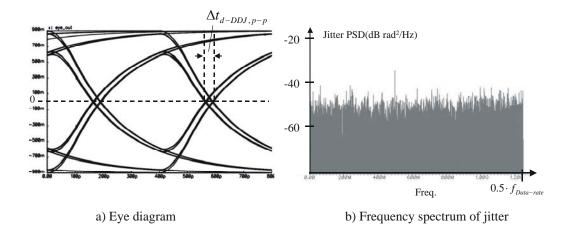

From [5] and the derivation in Appendix-B, the peak-to-peak jitter caused by the channel bandwidth limitation can be calculated by

$$\Delta t_{d-DDJ,p-p} = -\tau \cdot \ln(1 - e^{-\frac{T}{\tau}})$$

Eq. 2.5

where  $\Delta t_{d\text{-}DDJ,p\text{-}p}$  is the peak-to-peak jitter caused by channel bandwidth limitation,  $\tau$  is the channel time constant, and T is the serial data bit period. The example of  $V_{Rx}$  and its phase error signal are depicted in Figure 2.7. The data transition after identical successive bits makes a positive phase error, a late threshold crossing, and the successive data transitions make negative phase errors, early threshold crossing.

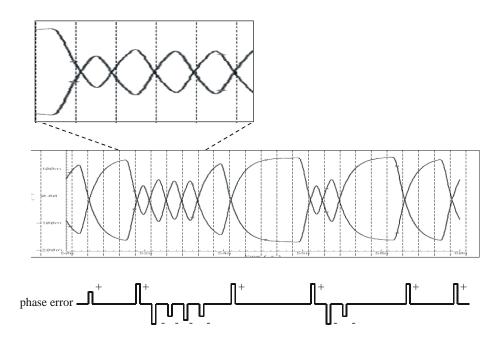

The pseudo-random binary bit sequence  $2^{23}$ -1 encoded with 8B/10B encoding scheme is simulated for 16384 bit periods. The time constant of interconnection channel is 0.5 of bit period. The eye diagram and the power spectrum of the jitter due to the bandwidth

limitation are shown in Figure 2.8. The simulated power spectrum of jitter shows nearly white spectrum. The details of the data-dependent jitter, interference jitter, and their equalization techniques are discussed in [5].

Figure 2.7 An example of data-dependent jitter

Figure 2.8 Data-dependent jitter

#### 2.3.3 Receiver jitter

The receiver jitter can be categorized to the jitter from data buffer and the jitter from CDR. The jitter from CDR dominates the receiver jitter. Figure 2.9 b) shows the block diagram of a PLL-based CDR. Like the PLL-based clock synthesizer, the high frequency output jitter of a PLL-based CDR is dominated by the VCO phase noise, whereas the output jitter at low frequency is related to the jitter of incoming serial data. Basically, the incoming serial data always has the data-dependent jitter from the bandwidth limitation of interconnections. In order to obtain a low jitter recovered clock, a small loop bandwidth has to be used to suppress the incoming jitter. However, the CDR should be able to track the input jitter according to the specified jitter tolerance. Therefore, the loop bandwidth cannot be too small. This trade-off can be released by the 2-loop CDR architecture, which will be analyzed in the following sections.

#### 2.4 PLL-based CDR and clock synthesizer

Figure 2.9 Block diagrams of PLL-based clock synthesizer and PLL-based CDR

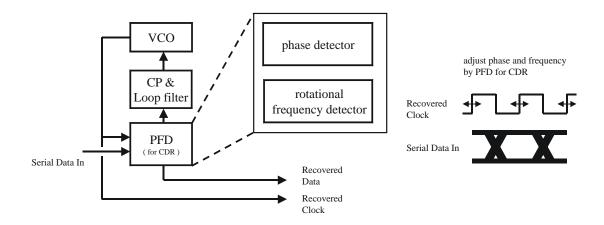

Phase-locked loop circuits are used in the precision timing circuits and systems. Because of feedback topology, they can operate over the variations of temperature, process parameters and supply voltages. The block diagrams of PLL-based clock synthesizer and PLL-based CDR circuit are shown in Figure 2.9 a) and b) respectively.

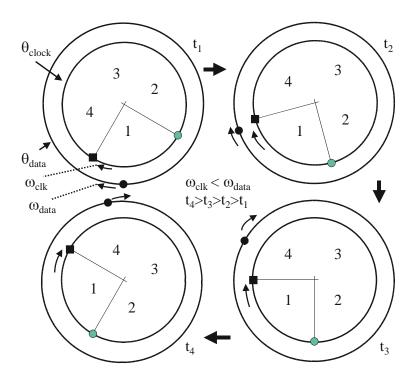

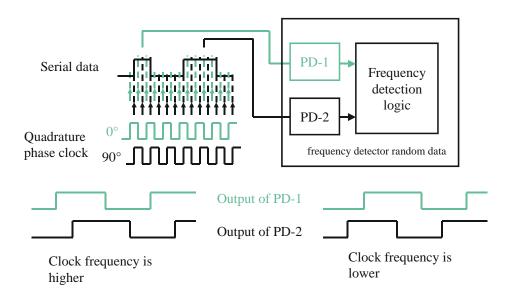

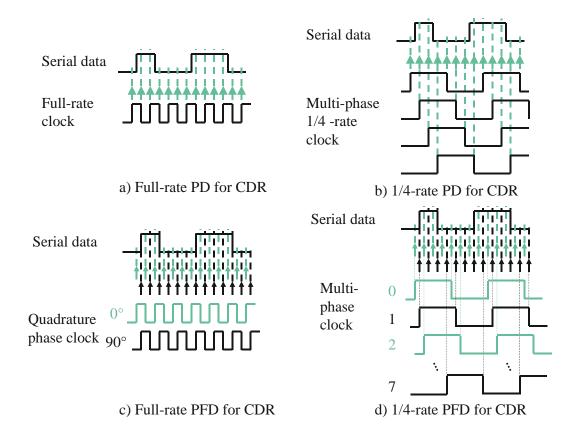

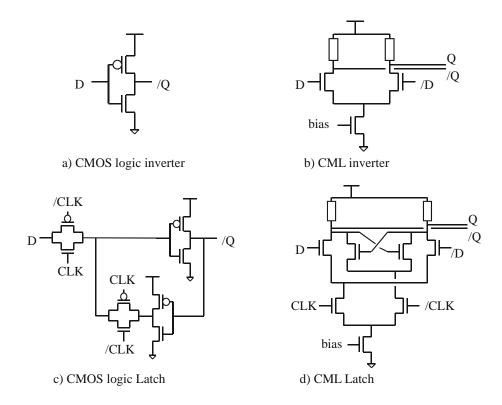

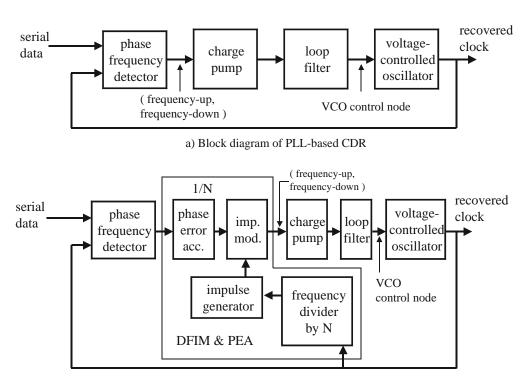

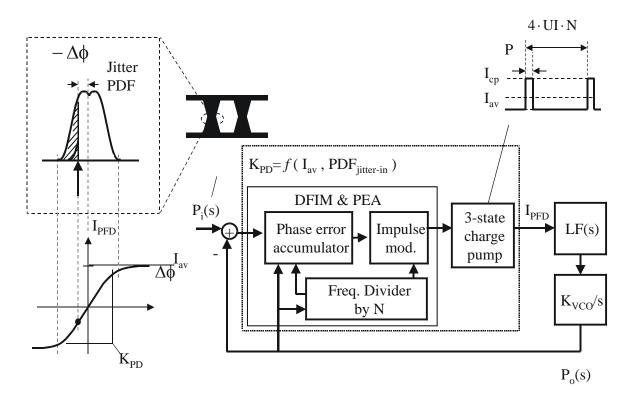

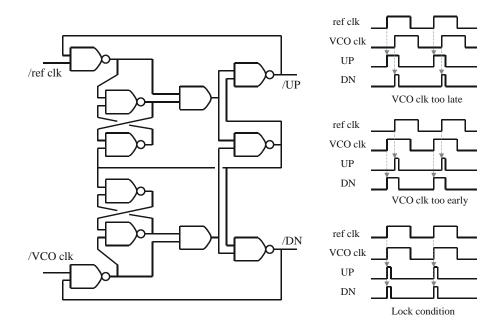

The clock synthesizer, Figure 2.9 a), adjusts the phase and frequency of the divided clock of the VCO to match the reference clock. In lock condition, the frequency of the output clock is N-time higher than the reference clock. It can be used in clock multiplication or as clock-jitter-filter, if a low jitter VCO is available. In the PLL-based CDR circuit, Figure 2.9 b), the VCO clock tracks the phase of the incoming serial data. Phase-frequency detectors of CDR and of clock synthesizer are different. The CDR circuit compares phases and frequencies of random data and of clock. The frequency detection in CDR is more complicate because the transitions of random data do not occur in every unit interval (UI). Unlike the frequency difference detection in clock synthesizer, this can be achieved by clock edge counting or by latches with feedback resetting. The common method for frequency detection in CDR is a rotational frequency detection. Details will be described in Section 3.1.4. Importantly the PFD of a CDR operates at different frequency from the PFD of a clock synthesizer. The PFD of a clock synthesizer operates at reference clock frequency, while the PFD of a CDR operates at the data rate frequency in the case of fullrate clock CDR. Its operation frequency can be reduced by clock rate reduction technique, using a multi-phase clock to supply sufficient sampling phases. The details of clock rate reduction technique is discussed in Section 3.2.

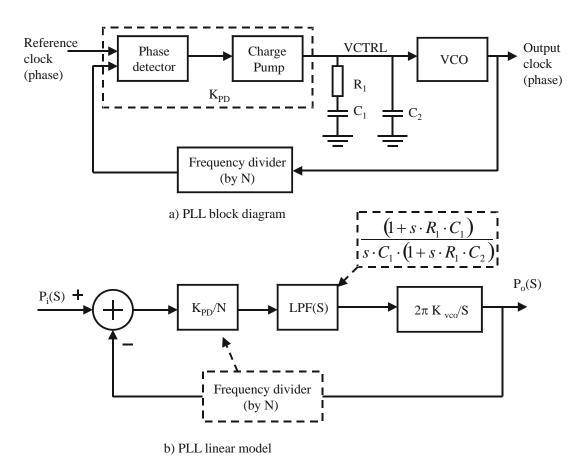

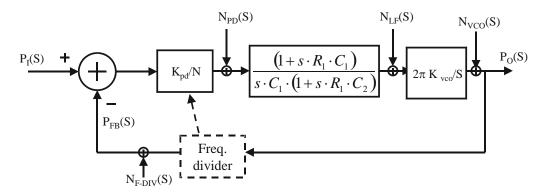

#### 2.4.1 PLL linear model

A phase-locked loop has non-linear behavior in some conditions. However, the loop behavior in phase domain at frequencies one or two decades lower than the PLL operation frequency can be assumed as a linear system. The detailed analysis is shown in [6]. The block diagram of PLL and its linear model are shown in Figure 2.10 a) and b) respectively.

Figure 2.10 PLL linear model

The open loop response of PLL linear model can be written as

$$H_{open}(s) = \frac{P_{op}(s)}{P_{i}(s)} = \frac{2\pi \cdot K_{VCO} \cdot K_{PD} \cdot (1 + s \cdot R_{1} \cdot C_{1})}{s^{2} \cdot C \cdot N \cdot (1 + s \cdot R_{1} \cdot C_{2})}$$

Eq. 2.6

for  $C_1 >> C_2$ , where  $P_i(s)$  is the phase of the input clock/data,  $P_o(s)$  is the phase of the output clock,  $K_{PD}$  is the phase detector gain referring to the ratio of the average current from charge pump to the phase difference between the feedback clock and the input clock/data,  $K_{VCO}$  is the VCO gain, and N is the dividing factor of the frequency divider. VCO behaves as an integrator in phase domain providing one pole at origin. The dividing factor in frequency divider can be interpreted as a gain reduction factor in the phase detector.

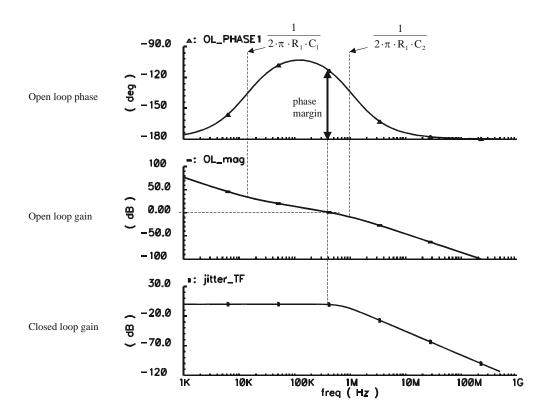

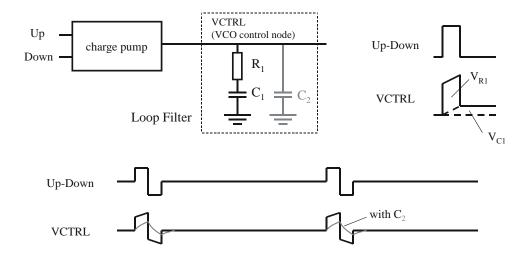

Figure 2.11 The open loop and closed loop responses of PLL linear model

Figure 2.11 shows the bode diagram from Eq. 2.6 and the corresponding closed loop response. Capacitor  $C_1$  averages charge injected from the charge pump and operates as a current integrator crating a pole at low frequency, ideally at origin. Without resister  $R_1$ , the loop has 2 poles at the origin and, hence, is an unstable system. Resistor  $R_1$  is required to create a zero for phase compensation.  $C_2$  is additionally applied to remove the high frequency noise/interference at the VCO control node, but it has to be small enough not to disturb the loop stability.  $C_2$  creates a high frequency pole that can degrade phase margin. If  $C_2$  is selected much smaller than  $C_1$ , the closed loop response can be simplified as  $2^{nd}$ -order loop. The simplified closed loop response can be written as

$$H_{closed}(s) = \frac{P_o(s)}{P_i(s)} = \frac{(1 + 2 \cdot \varsigma \cdot (s/\omega_N))}{1 + 2 \cdot \varsigma \cdot (s/\omega_N) + (s/\omega_N)^2}$$

Eq. 2.7

where,

$$\varsigma = \frac{1}{2} \cdot \sqrt{\frac{K_{PD} \cdot 2\pi \cdot K_{VCO} \cdot R_1^2 \cdot C_1}{N}}$$

Eq. 2.8

and

$$\omega_N = \frac{2 \cdot \zeta}{R_1 \cdot C_1} = \sqrt{\frac{K_{PD} \cdot 2\pi \cdot K_{VCO}}{N \cdot C_1}}$$

Eq. 2.9

$\varsigma$  is the damping factor and  $\omega_N$  is the loop natural frequency<sup>\*</sup>. As derived in [7], the loop bandwidth can be calculated from

$$\omega_{-3dB} = \omega_N \cdot \left( (2 \cdot \zeta^2 + 1) + \sqrt{(2 \cdot \zeta^2 + 1)^2 + 1} \right)^{\frac{1}{2}}$$

Eq. 2.10

where  $\omega_{.3dB}$  is the corner frequency\* of the closed loop response. If a large value of  $C_1$  is applied, in order to make  $\omega_{.3dB}$  greater than 3 to 4 times of  $1/R_1C_1$  and also make  $2\varsigma^2 >> 1$ , the corner frequency of closed loop transfer function can be simplified as

$$\omega_{-3dB} \approx 2 \cdot \omega_N \cdot \zeta = \frac{K_{PD} \cdot 2\pi \cdot K_{VCO} \cdot R_1}{N}$$

Eq. 2.11

Eq. 2.7 to Eq. 2.11 describe the closed loop response of a PLL. The damping factor defines how the loop reacts to the input. If the damping factor is smaller than 0.7 or underdamped, the closed loop response shows an overshoot around its corner frequency, but the loop acquisition time is small. On the opposite, if the damping factor is larger than 0.7 or overdamped, there is no overshoot around its corner frequency, but the loop needs more time to acquire the lock condition.

×

<sup>\*</sup> frequency in this term is angular frequency

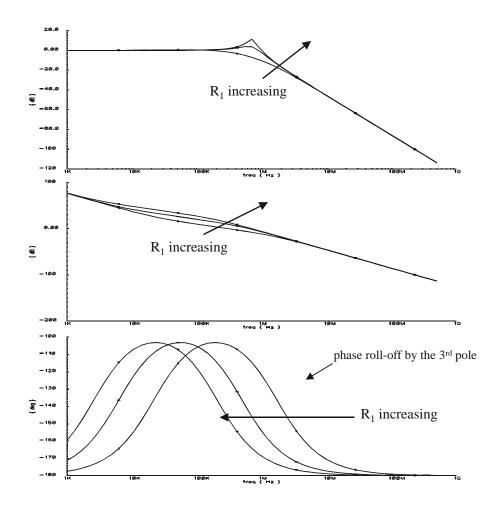

Figure 2.12 The open and closed loop responses of the 3<sup>rd</sup>-order loop by various loop resistors

From Eq.2.8, the damping factor of the  $2^{nd}$ -order loop can be calculated. However, with the capacitor  $C_2$ , the loop is actually  $3^{rd}$ -order, so that the loop damping factor cannot be precisely predicted. The phase roll-off resulting from the  $3^{rd}$  pole is presented in the bode diagram in Figure 2.12. By increasing loop resistor  $R_1$ , the zero and the  $3^{rd}$  pole move towards low frequency. Consequently, the crossover frequency increases and the phase margin is degraded. However, the equations of the  $2^{nd}$  order loop in Eq. 2.7 to Eq. 2.11, can provide a simple hand calculation for the loop design. The more precise loop characteristic can be obtained by the linear model simulation.

#### 2.4.2 Loop characteristic design and jitter in PLL

a) Linear model of jitter in PLL

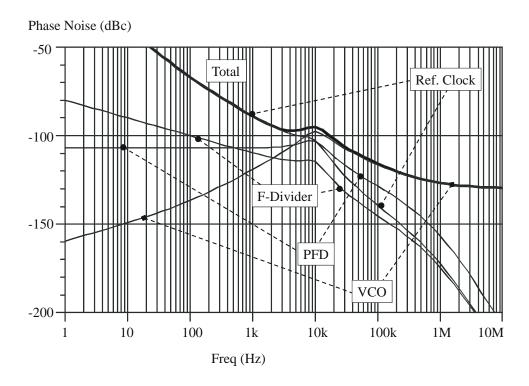

Figure 2.13 Jitter in PLL

The main contributions of jitter in PLL are incoming jitter and VCO phase noise. Figure 2.13 a) shows the linear model of PLL with its jitter sources. The transfer function of the incoming jitter,  $P_i(S)$ , to the output clock jitter,  $P_o(S)$ , has low-pass characteristic. It is described by the closed loop response as shown in Figure 2.13 b). The transfer function of VCO phase noise,  $N_{VCO}(S)$ , to the output clock jitter is depicted in Figure 2.13 c). It has high-pass characteristic by the same corner frequency. Incoming jitter within the loop bandwidth will be tracked by the output clock. The incoming jitter out of the loop bandwidth will be suppressed. The VCO phase noise dominates the clock output jitter at high frequencies. The low frequency part of the VCO phase noise is cancelled itself out by the negative feedback. Other building blocks have jitter induced by device noise, supply/substrate noise, interference, mismatch and offsets in the circuits. Jitter from phase detector, charge pump, and frequency divider,  $N_{PD}(S)$  and  $N_{F-DIV}(S)$ , have a low-pass

transfer function to the output clock. The jitter from loop filter has a band-pass transfer function.

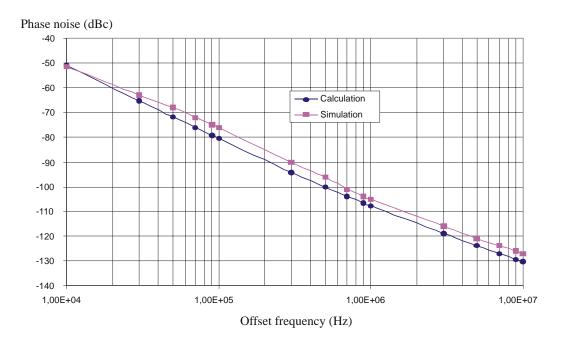

Figure 2.14 Phase noise (jitter) contribution in PLL

Figure 2.14 shows the plot of phase noise contributions from various sources to the PLL output clock obtained by the simulation of PLL linear model. Phase noise describes jitter in frequency domain as the ratio of power spectra around the carrier frequency to the carrier power. The total phase noise of PLL output clock is depicted by the thick line. Inside loop bandwidth, up to around 10kHz in this example, the output phase noise is dominated by the phase noise of the reference clock. The VCO phase noise dominates the output phase noise at higher offset frequencies. The phase frequency detector and the frequency divider contribute to the output phase noise inside the PLL loop bandwidth.

From the linear model, the contributions of jitter sources in PLL are well understood are useful for loop characteristic design. For example, in the design of a PLL-based clock synthesizer that has a low jitter reference clock from quartz oscillator and a ring oscillator as VCO, the loop bandwidth should be wide in order to suppress the poor jitter quality of

the ring-based VCO clock. In a high performance system, a low jitter LC-VCO is applied. Its loop bandwidth is selected to have the same jitter contributions from the reference clock and VCO. Another example is a PLL-based clock-jitter-filter. It uses a low jitter VCO and a small loop bandwidth to suppress the input jitter.

The loop characteristic of a PLL-based CDR has to be designed to meet the requirements of the jitter tolerance and the jitter peaking. The CDR is normally designed to be overdamped, in order to avoid jitter peaking that degrades jitter tolerance.

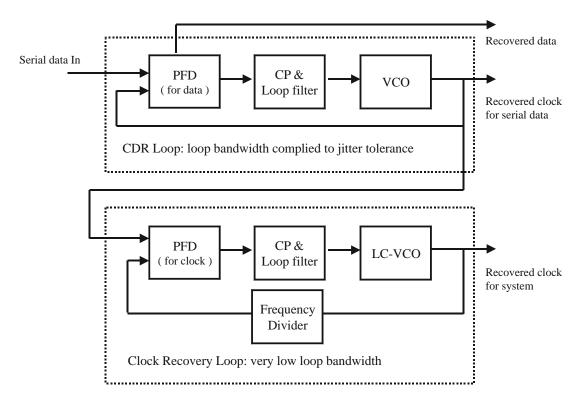

## 2.5 The architectures of CDRs for large synchronous networks

By the understanding of PLL jitter sources and their effects, the architecture of the CDR can be designed. Serial data always has unavoidable jitter contributed by the transmitter jitter and the channel jitter. Therefore, the CDR should be able to track the phase of incoming data to provide sufficient bit-error-rate (BER). The BER will be degraded, if the loop bandwidth of the CDR is too small. The jitter tolerance specification has to be met. In large synchronous networks. The recovered clock from the CDR has to be used as a local reference clock, the conventional CDR architecture will not be suitable. Hence, the 2-loop architecture has to be applied, in order to avoid the trade-off between jitter tolerance and jitter filtering. Different approaches will be discussed and compared in the following section.

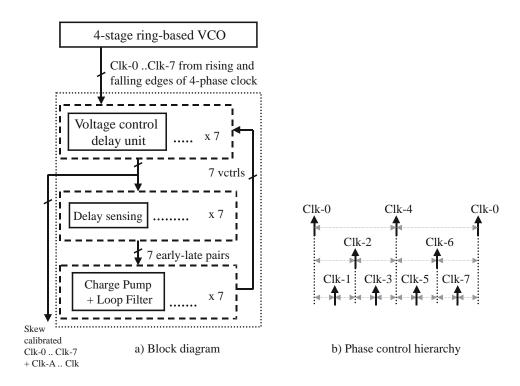

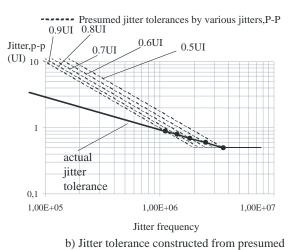

#### Recovered clock for system Serial data In FD CP & LC-VCO Loop filter (for data) Clock Recovery Loop: low loop bandwidth Recovered clock for serial data CP & PD VCDL (for data) Loop filter Clock and Data Recovery Loop: Recovered data loop bandwidth complied to jitter tolerance

#### 2.5.1 The CDR with a clock extraction and a phase tracking loop

Figure 2.15 The CDR with clock extraction and phase tracking loops

The first approach is using a clock extraction loop and a phase tracking loop. The block diagram is shown in Figure 2.15. In the clock extraction loop, a low jitter VCO is required and the loop bandwidth has to be small to suppressed the incoming jitter. Therefore, LC-VCO is used. The extracted clock is further applied for the data tracking loop. It adjusts the clock phase by a voltage control delay line (VCDL) in order to track the phase of the incoming serial data. The loop bandwidth of the data tracking loop has to comply with the jitter tolerance standard. This approach has disadvantage that the frequency detector and the phase detector in both loops have to operate at the data rate frequency. Therefore, the current-mode-logic has to be applied. It makes the whole system has large power consumption. Moreover, it is difficult to has small loop bandwidth, when phase detector operate at high frequency. The clock rate reduction architecture is difficult to apply because the LC-VCO is not inherently multi-phase but it has to be used for low jitter clock generation.

#### 2.5.2 The CDR with a clock-jitter-filter

Figure 2.16 The CDR with a clock-jitter-filter

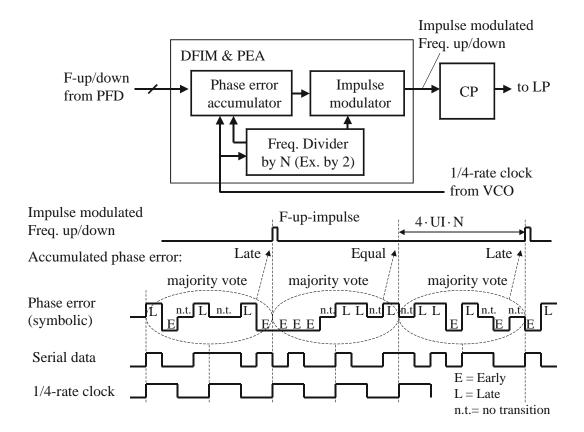

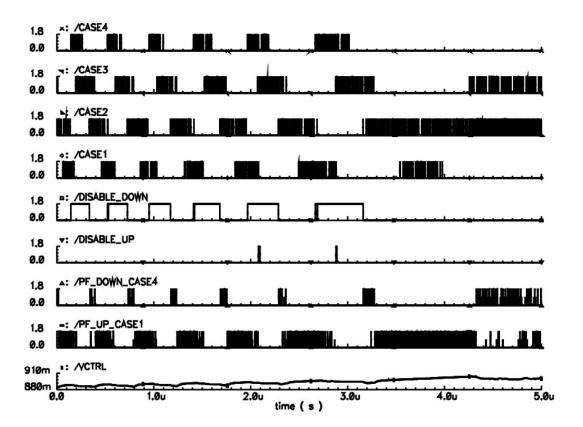

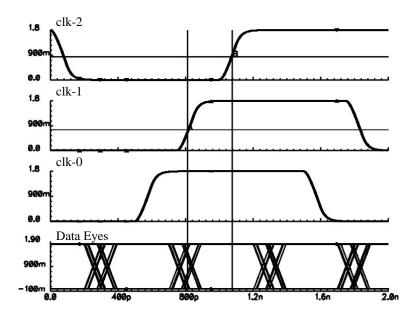

The second approach is using a clock and data recovery loop and a clock-jitter-filter. Its block diagram is shown in Figure 2.16. In the CDR, the frequency detector is applied to be able to operate without the local reference clock. The loop bandwidth of CDR is designed to comply with the jitter tolerance specification. The second loop operates as a clock-jitter-filter. The loop bandwidth has to be small to reduce the jitter of the recovered clock. The low jitter VCO is needed therefore a LC-VCO is applied in the clock-jitter-filter. In this approach, there are many advantages over the previous one. The clock rate reduction architecture can be applied by using a ring oscillator in the front-ended CDR loop. With carefully design, the ring oscillator can provide sufficient low jitter for data recovery function. With reduced clock rate CDR, the recovered clock is at the lower frequency. It is suitable for the small loop bandwidth design in the clock-jitter-filter. Moreover, the reduced clock rate CDR using multi-phase clock is an intrinsic DEMUX, hence, the power consumption of the whole deserializer is reduced. The clock-jitter-filter operates not only

as clock-jitter-filter but also as the high frequency clock synthesizer for the data serializer. Consequently, power consumption of the entire transceiver is minimized. This architecture is selected to apply on the CDR for large synchronous networks. The detail designs of both loops, the CDR loop and the clock-jitter-filter loop, are discussed in the following chapters.

By using the CDR in Figure 2.16, the incoming jitter inside the loop bandwidth of the clock-jitter-filter still remains in the output clock. It is mainly contributed by the channel jitter because of its white spectrum. The jitter resulting from the offset voltage in the data buffer, which is induced by the flicker noise and the device mismatch, is converted to the high frequency jitter by the 8B/10B coding scheme, as discussed in Section 2.3.1. Therefore, it is filtered by the clock-jitter-filter. The remaining jitter at the output clock can be minimized by decreasing the ISI jitter. It can be achieved by the equalization technique in the serial data transmitter driver.

The jitter of the distributed clock is specified in [1] to be smaller than 25ps rms. Therefore, it is a primary goal of this thesis.

#### 2.6 Summary

From the analysis of the jitter sources in serial data communication system, the jitter sources in transmitter can be minimized by using a clean reference clock and a low jitter LC-VCO in the clock synthesizer in time distributor node. Therefore, the main contribution of the serial data jitter is the channel jitter by its bandwidth limitation. It causes white spectrum jitter because of the random nature of the serial data stream. The clock data recovery circuit at the receiver has low-pass jitter transfer function according to its loop bandwidth. It can filter some parts of the incoming jitter from the serial data. However, its loop bandwidth can not be too small. It needs to have a tracking ability for sufficient bit-error-rate. In order to obtain clock distribution through data network, the CDR with 2-loop topology has to be applied because it has no trade-off between jitter tolerance and jitter filtering. The front-ended loop generates the clock tracking serial data phase for the adequate bit-error-rate and the secondary loop suppresses the jitter by its small loop

bandwidth and low jitter LC-VCO. It can provide low jitter clock for local reference timing.

## Chapter 3

# Structure of the front-ended loop: PLL-based CDR

#### 3.1 State of the art

Clock and data recovery circuit is a crucial component in serial data receiver. The phase-locked loop based, PLL-based, CDR is widely used. The CDR uses phase error information from phase detector to adjust phase and frequency of its VCO clock to synchronize to the incoming serial data. The jitter characteristic of PLL-based CDR is defined by its loop parameters. For instance, its loop bandwidth defines its jitter transfer function and its frequency capture range. The architectures of PLL-based CDR can be roughly categorized to 2 types, i.e. the CDR with and without external reference clock.

#### 3.1.1 PLL-based CDR with an external reference clock

This type of CDR requires the external reference clock for its operation. It is widely used in the standard serial data transceiver system, as shown in Figure 1.1, because the external reference clock is always available for the data transmitter. The architectures can be roughly separated into two groups. They are CDR with frequency initialization and CDR with phase synthesis and phase interpolation.

#### VCO 44 Control Lock Freq. Divider Loop logic detector by factor **D** Filter **PFD** Ref. CLK (clk. to clk.) ( bitrate freq./ $\mathbf{D}$ ) Selector CP Serial Data In PD Recovered Data Recovered Clock Ref. CLK ( bitrate freq./ $\mathbf{D}$ ) Frequency acquisition loop (active in initialisation) Recovered Clock Data tracking loop

#### 3.1.1.1 CDR with frequency initialization

Serial Data In

Figure 3.1 CDR with frequency initialization loop

With the simple phase detector for serial data, the frequency capture range of a PLL-based CDR is limited by its loop bandwidth. Therefore, a frequency acquisition loop has to be applied. The CDRs with frequency initialization are reported in [2][3]. Figure 3.1 shows its block diagram and the important signals. The frequency acquisition loop, shown as grey lines, drives the CDR to lock with an external reference clock. The frequency of the external reference clock and the dividing factor D are carefully selected in order to make the frequency of the VCO close to the incoming data rate. The phase frequency detector in the frequency acquisition loop is similar to the one in the clock synthesizer, which is designed for clock-to-clock comparison. It will be further discuss in detail in section 4.2.2.1. After the frequency acquisition is achieved, the CDR switches to a data tracking loop as shown in black lines. The clock phase will be adjusted to sample the incoming data at the optimum point.

It occurs in practical that the reference clocks of different transceivers can not be exactly equal. Therefore, in the serial communication standard, e.g. PCI Express, the unit interval of transmitter and receiver can be different by +/-300 ppm. As a result, the operation frequency of the CDR at the beginning of the data tracking mode is different from the incoming data rate. The loop bandwidth of the data tracking loop has to be designed to cover this frequency difference.

#### 3.1.1.2 CDR with phase synthesis and phase interpolation

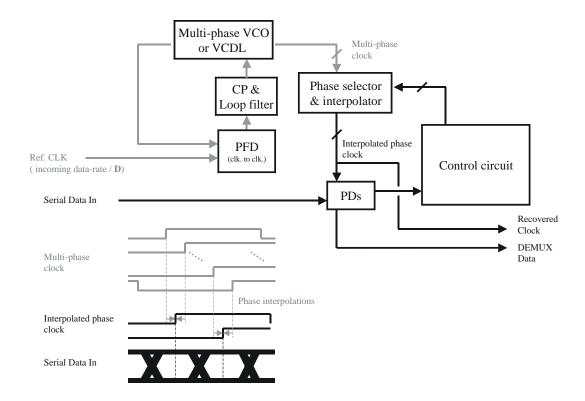

Figure 3.2 CDR with phase interpolation

A CDR with phase synthesis and phase interpolation is depicted in Figure 3.2. A phase synthesis loop, shown in grey lines, generates a multiphase clock locked to a reference clock by using a ring-based VCO or a Voltage Control Delay Line (VCDL). The phase selectors and phase interpolators select the suitable pairs of clock phases from the multiphase clock and interpolate them in order to obtain the optimum data sampling phases. CDRs with this architecture are reported in [8],[9], and [10]. If there is frequency difference between the reference clock and the incoming serial data, phase errors cyclically

change. The control circuit of the phase selectors and the phase interpolators is designed to support this phase error rotation and the CDR has to track the phase error over one unit interval, 360°. Parts of phase error signals are used to drive the VCO clock to track the frequency difference. It makes the sampling phase shift from the optimum sampling point, hence, degrades the CDR operation. The compensation of the phase offset in a plesiochronous operation is reported in [11]. The additional frequency detector based on the edge-counting is applied to estimate the frequency difference and generate signals to compensate the phase offset.

#### 3.1.2 PLL-based CDR without external reference clock

Figure 3.3 CDR without external reference clock

CDR without external reference clock is presented in Figure 3.3. Its architecture is quite simple. However, its PFD is more complicated than the phase detector (PD) in CDR with an external reference clock. The phase and frequency error can be obtained by PFD. The frequency difference between the serial data and the VCO clock can be indicated by the rotational frequency detection. It will be discussed in detail in section 3.1.4. The CDR has wider frequency capture range than its loop bandwidth, therefore the frequency acquisition loop and external reference clock are not required. Normally, this type of CDR is applied in the signal repeater in the optical communication system or in applications that local reference clocks are not available. The design and implementation of the full-rate-clock architecture is reported in [12]. The half-rate-clock designs are shown in [13] and [14]. The

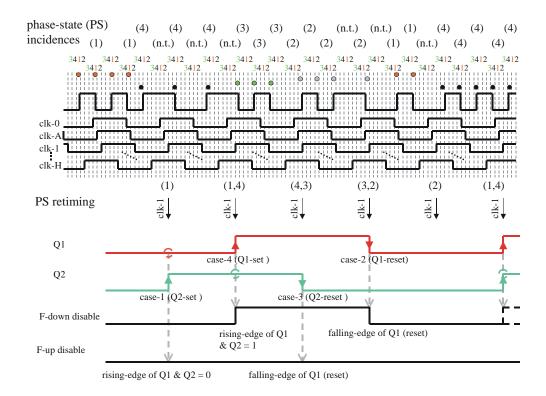

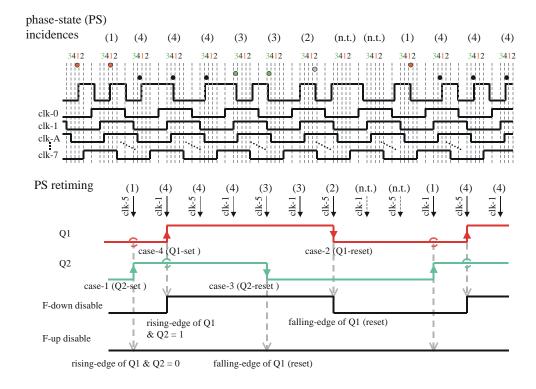

1/4-rate-clock approach is proposed in this thesis. It has been also reported as a publication in [15].

#### 3.1.3 Phase detector for serial data

The phase detectors for serial data can be categorized into two types, i.e. the linear phase detector and the binary phase detector.

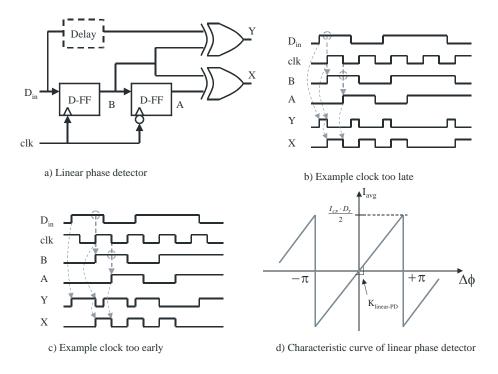

#### 3.1.3.1 Linear phase detector

Figure 3.4 Linear phase detector

The circuit of a linear phase detector, its operations and characteristic curve are shown in Figure 3.4. The linear phase detector had been first time published in [16] by Hogge. The operation of the linear phase detector can be described in the following. The linear phase detector generates the reference impulses that have a duration of half unit interval at every serial data transition, shown as signal 'X' in Figure 3.4 b) and c). It can be produced by two D-flipflops (D-FFs), which are clocked by raising and falling clock edges, and XOR-gate. The phase-measuring impulses are generated by the recovered data, signal 'B', and the

incoming serial data. The phase-measuring impulses are shown as signal 'Y'. If clock are too late/early, the phase measuring impulses will be shorter/longer than a duration of half unit interval, as depicted in Figure 3.4 b) and Figure 3.4 c) respectively. In the lock condition, the phase-measuring impulses have a half unit interval duration. The difference of the impulse durations represents the phase error, therefore its phase error output depends linearly to the phase error between serial data and VCO clock. Moreover, the recovered serial data is automatically regenerated in the phase detection circuit as signal 'B'. The disadvantage of the linear phase detector is the utilization of impulse durations. That their distortions from unbalancing gate delay or rise/fall times cause phase offset or the sampling point shifting from the middle of the data eye. Furthermore, the phase error is detected in every serial data transitions, but not every unit interval. Consequently, the gain of this phase detector type depends on the data transition density.

Figure 3.4 d) shows the characteristic curve of the linear phase detector. The average current output of a linear phase detector combining with a charge pump can be written as

$$I_{avg-linear-PD}(\Delta\phi) = \frac{\Delta\phi \cdot I_{CP} \cdot D_T}{2\pi} \left[ \mathbf{A} \right] \quad \text{for } -\pi \le \Delta\phi \le +\pi$$

Eq. 3.1

where  $I_{avg-linear-PD}$  is the average output current of the linear phase detector combining with a charge pump,  $\Delta \phi$  is the phase error,  $I_{CP}$  is the charge pump current and  $D_T$  is the data transition density, the number of data transitions per unit interval. Therefore, the gain of a linear phase detector can be written as

$$K_{linear-PD} = \frac{I_{CP} \cdot D_T}{2 \cdot \pi} \left[ \frac{A}{rad} \right]$$

Eq. 3.2

where  $K_{linear-PD}$  is the gain of a linear phase detector.

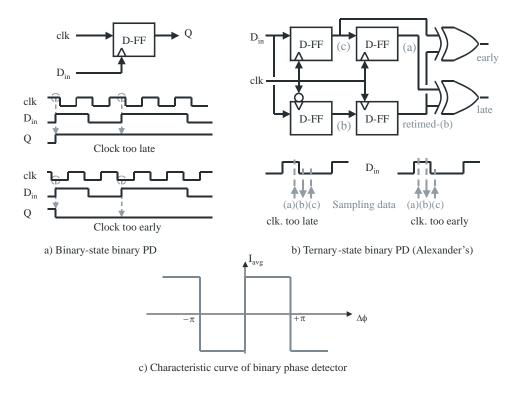

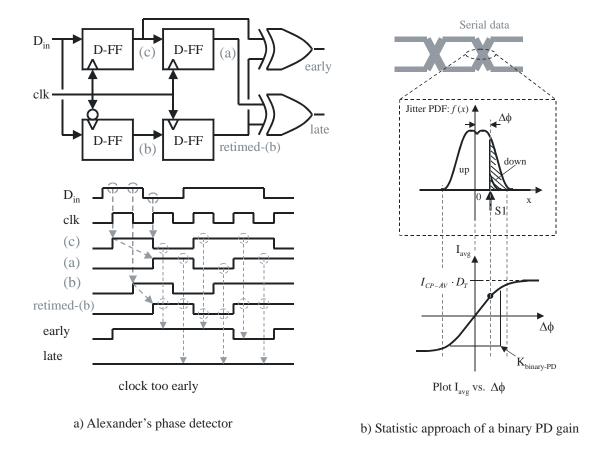

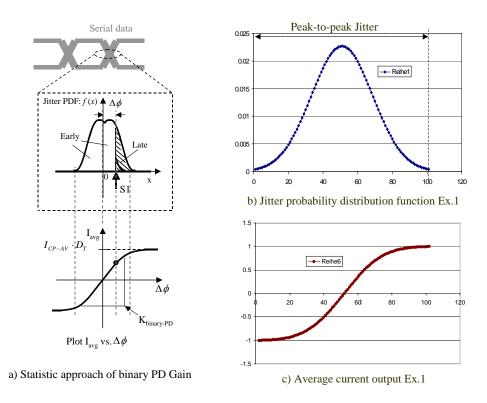

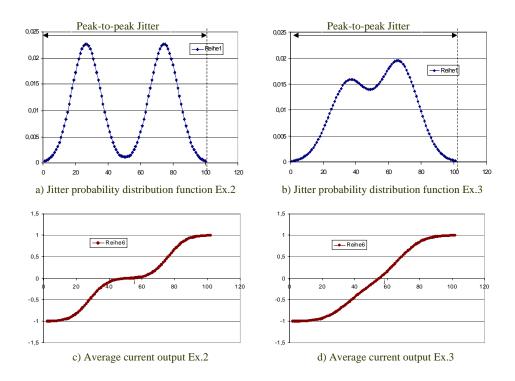

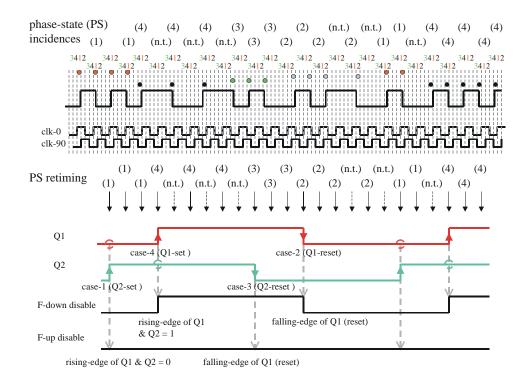

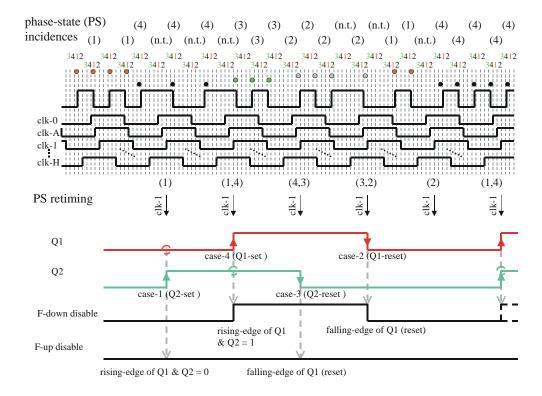

#### 3.1.3.2 Binary phase detector

Figure 3.5 Binary-state and ternary-state binary phase detectors

Unlike the linear phase detector, a binary phase detector indicates only if the clock phases are too early or too late but it cannot provide the quantitative phase error. It utilizes the unavoidable jitter in the incoming serial data and the VCO clock to generate the same amounts of the early and the late signals in the lock condition. The binary phase detector can be separated into the binary-state type and the ternary-state type (Alexander's phase detector).

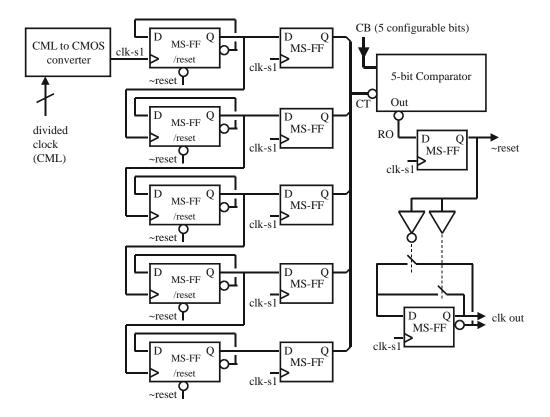

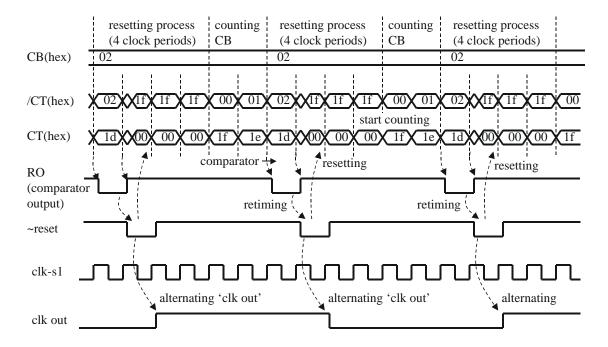

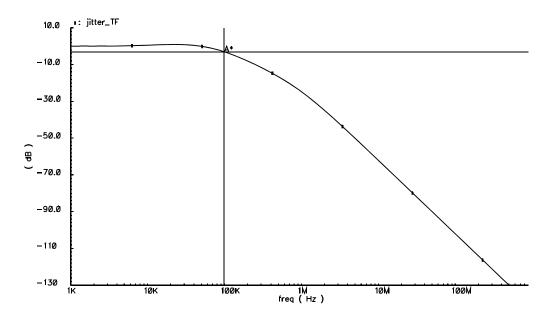

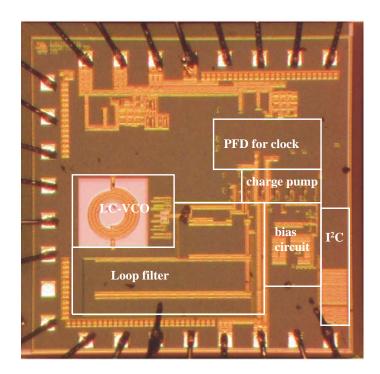

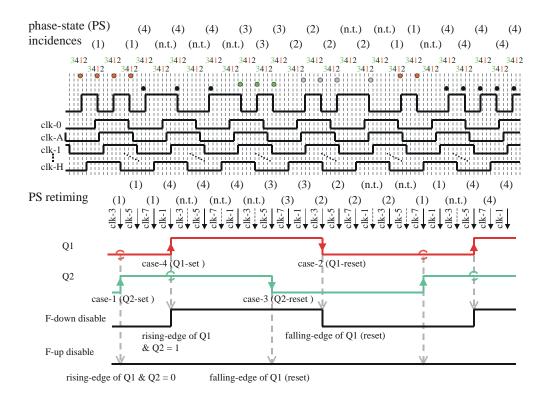

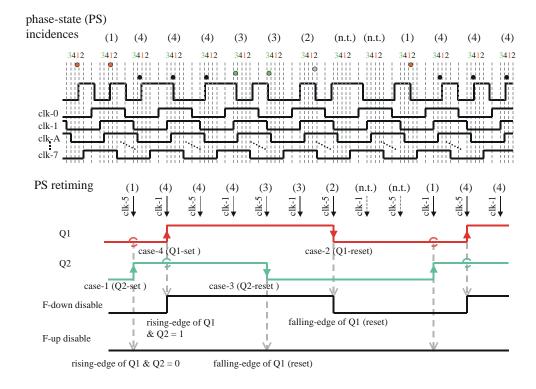

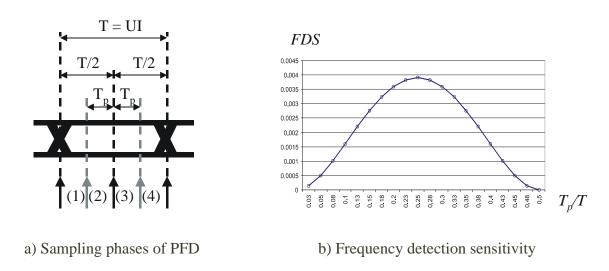

#### 3.1.3.2.1 Binary-state binary phase detector