# TOWARDS DYNAMICALLY RECONFIGURABLE MIXED-SIGNAL ELECTRONICS FOR EMBEDDED AND INTELLIGENT SENSOR SYSTEMS

Beiträge zur Entwicklung dynamisch rekonfigurierbarer, gemischt analogdigitaler Elektronik für eingebettete und intelligente Sensorsysteme

#### vom

Fachbereich Elektrotechnik und Informationstechnik der Technischen Universität Kaiserslautern zur Erlangung des akademischen Grades eines

#### Doktor der Ingenieurwissenschaften (Dr.-Ing.)

Dissertation

von

Senthil Kumar Lakshmanan geb. in Tiruchy (Indien)

D 386

Eingereicht am: 25. June 2008

Tag der mündlichen Prüfung: 04. November 2008

Dekan des Fachbereichs: Prof. Dr.-Ing. Steven Liu

Promotionskommission

Vorsitzender: Prof. Dr.-Ing. Remigius Zengerle

Berichterstattende: Prof. Dr.-Ing. Andreas König

Prof. Dr.-Ing. Ulrich Rückert

# Erklärung

Hiermit versichere ich, dass ich die vorliegende Arbeit selbst angefertigt und verfasst habe und alle benutzen Hilfsmittel in der Arbeit angegeben habe. Die vorliegende Dissertation oder Teile hiervon würden noch nicht als Prüfungsarbeit für eine staatliche oder andere wissenschaftliche Prüfung eingereicht.

Kaiserslautern, den 25/06/08

M.Sc. Senthil Kumar Lakshmanan

#### **Abstract**

Rapid growth in sensors and sensor technology introduces variety of products to the market. The increasing number of available sensor concepts and implementations demands more versatile sensor electronics and signal conditioning. Nowadays signal conditioning for the available spectrum of sensors is becoming more and more challenging. Moreover, developing a sensor signal conditioning ASIC is a function of cost, area, and robustness to maintain signal integrity. Field programmable analog approaches and the recent evolvable hardware approaches offer partial solution for advanced compensation as well as for rapid prototyping.

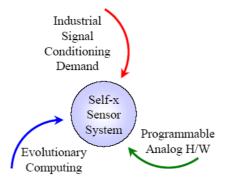

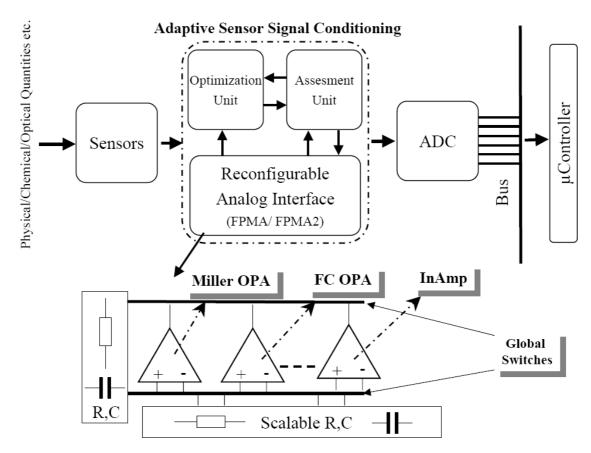

The recent research field of evolutionary concepts focuses predominantly on digital and is at its advancement stage in analog domain. Thus, the main research goal is to combine the ever increasing industrial demand for sensor signal conditioning with evolutionary concepts and dynamically reconfigurable matched analog arrays implemented in main stream Complementary Metal Oxide Semiconductors (CMOS) technologies to yield an intelligent and smart sensor system with acceptable fault tolerance and the so called self-x features, such as self-monitoring, self-repairing and self-trimming. The conceptual illustration of the aspired research work is depicted in Figure Ab-1.

Figure Ab-1: Symbolic representation of the research work

For this aim, the work suggests and progresses towards a novel, time continuous and dynamically reconfigurable signal conditioning hardware platform suitable to support variety of sensors.

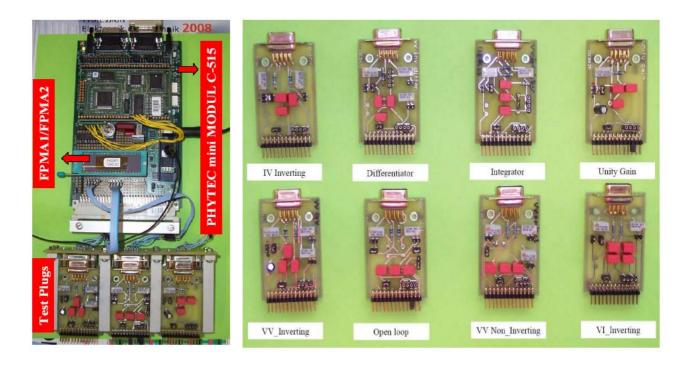

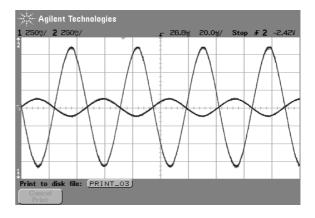

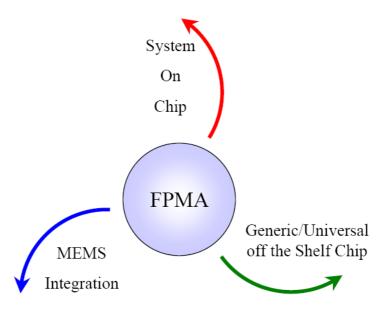

The state-of-the-art has been investigated with regard to existing programmable/reconfigurable analog devices and the common industrial application scenario and circuits, in particular including resource and sizing analysis for proper motivation of design decisions. The pursued intermediate granular level approach called as Field Programmable Medium-granular mixed signal Array (FPMA) offers flexibility, trimming and rapid prototyping capabilities. The proposed approach targets at the investigation of industrial applicability of evolvable hardware concepts and to merge it with reconfigurable or programmable analog concepts, and industrial electronics standards and needs for next generation robust and flexible sensor systems. The devised programmable sensor signal conditioning test *chips*, *namely FPMA1/FPMA2*, designed in 0.35 µm (C35B4) Austriamicrosystems, can be used as a single instance, off the shelf chip at the PCB level for

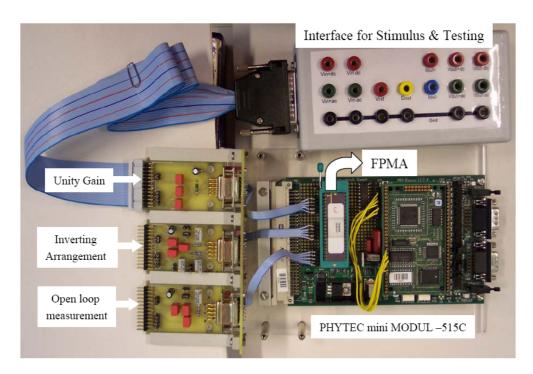

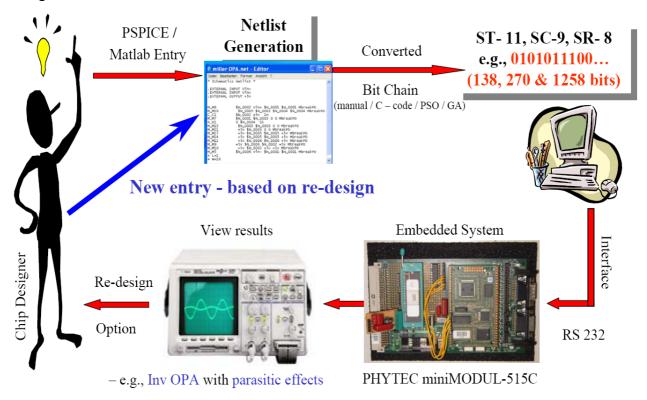

conditioning or *in the loop* with dedicated software to inherit the aspired self-x features. The use of such self-x sensor system carries the promise of improved flexibility, better accuracy and reduced vulnerability to manufacturing deviations and drift. An embedded system, namely PHYTEC miniMODUL-515C was used to program and characterize the mixed-signal test chips in various feedback arrangements to answer some of the questions raised by the research goals.

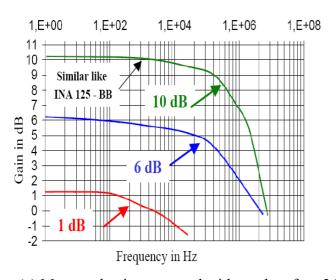

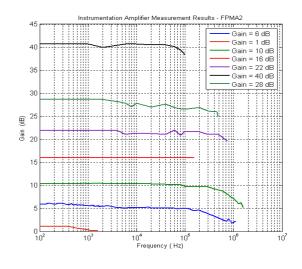

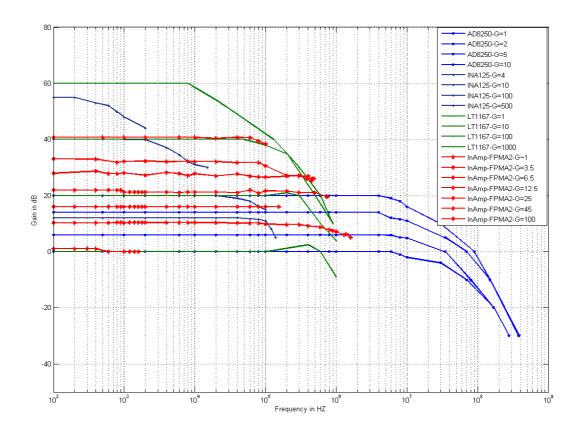

Wide range of established analog circuits, ranging from single output to fully differential amplifiers, was investigated at different hierarchical levels to realize circuits like instrumentation amplifier and filters. A more extensive design issues based on low-power like for e.g., sub-threshold design were investigated and a novel soft sleep mode idea was proposed. The bandwidth limitations observed in the state of the art fine granular approaches were enhanced by the proposed intermediate granular approach. The so designed sensor signal conditioning instrumentation amplifier was then compared to the commercially available products in the market like LT 1167, INA 125 and AD 8250.

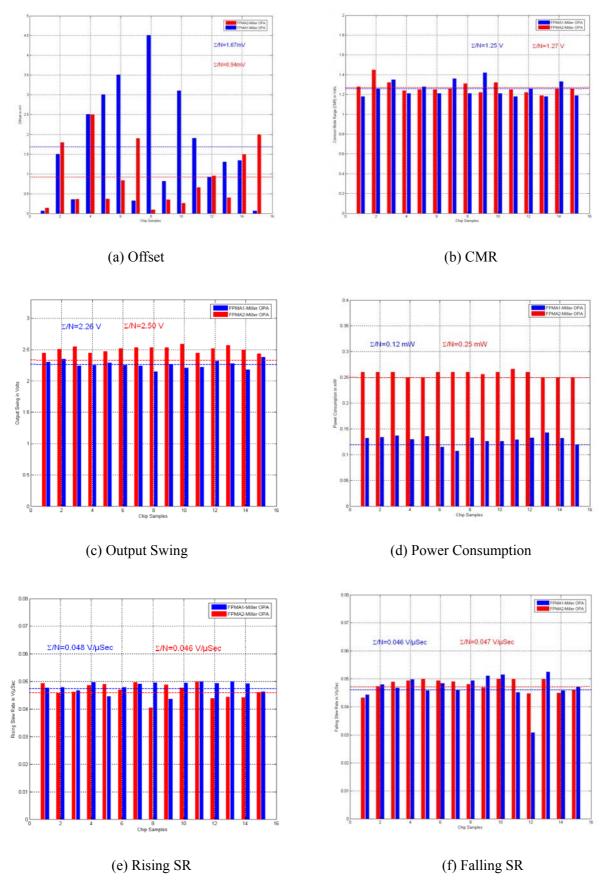

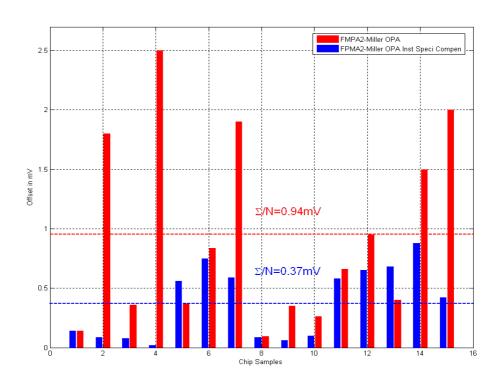

In an adaptive prototype, evolutionary approaches, in particular based on particle swarm optimization with multi-objectives, were just deployed to all the test samples of FPMA1/FMPA2 (15 each) to exhibit self-x properties and to recover from manufacturing variations and drift. The variations observed in the performance of the test samples were compensated through reconfiguration for the desired specification.

# Acknowledgments

First and foremost, I wish to express my gratitude and sincere thanks to my advisor **Prof. Dr.-Ing. Andreas König** for the suggestions on the research topic. I am deeply indebted to him for his advice, suggestions, and numerous discussions on my research and help throughout my stay. I would like to thank my second reporter Prof. Dr-Ing. Ulrich Rückert for his interest in my work.

I would also like to acknowledge PHYTEC Messtechnik GmbH, Mainz for funding the chips manufacturing which are used in the scope of this thesis work.

I also take this opportunity to thank the system administrators Mr. Markus Müller and Mr. Andreas Christmann. I thank Dr. Peter Tawdross for employing optimization techniques on to the chips designed in this thesis work. I am thankful to Mr. Thomas Gräf for designing PCB test plugs. I am thankful to Mr. Robert Freier and Mr. Jürgen Hornberger for helping me in german language translations of the abstract.

Above all I would like to thank my parents Vijayalakshmi, L and Lakshmanan, R for their support, encouragement and patience. Last but not least, I would also like to thank my relatives and friends for their constant motivation.

To my mother

- Vijayalakshmi. L

# Contents

| 1. | Intr  | oductionoduction                                                                                                              | 10 |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------|----|

|    | 1.1   | Signal Conditioning in Integrated Smart Sensor System                                                                         | 10 |

|    |       | 1.1.1 Trimming / Calibration Techniques                                                                                       |    |

|    | 1.2   | Motivation of this thesis                                                                                                     |    |

|    | 1.3   | Aims of this thesis                                                                                                           | 14 |

|    | 1.4   | Organization of the Thesis                                                                                                    | 15 |

| 2. | State | e – of – the– Art of Programmable / Reconfigurable CMOS Analog Electronics                                                    |    |

|    | 2.1   | Introduction                                                                                                                  | 16 |

|    | 2.2   | Overview of Commercial Programmable Analog / Mixed-Signal IC's                                                                | 19 |

|    |       | 2.2.1 IMP- Electrically Programmable Analog Devices (EPAC)                                                                    |    |

|    |       | 2.2.2 Motorola MPAA020                                                                                                        |    |

|    |       | 2.2.3 Zetex Totally Reconfigurable Analog Circuit                                                                             |    |

|    |       | 2.2.4 Anadigm AN231E04 Dynamical Reconfigurable dpASP                                                                         | 21 |

|    |       | 2.2.5 Texas Instruments – PGA- Digital Trim for Non-Linearity's                                                               |    |

|    |       | 2.2.6 Analog Devices – Digi Trim AD855x series                                                                                |    |

|    |       | 2.2.7 Lattice ispPAC                                                                                                          |    |

|    |       | 2.2.8 Cypress PSoC                                                                                                            |    |

|    |       | 2.2.9 Analog Linear Devices – EPAD                                                                                            |    |

|    |       | 2.2.10 Melexis – Programmable sensor interface MLX90308                                                                       |    |

|    |       | 2.2.11 MaZeT – Programmable Gain Transimpedance amplifier MTI04Bx-BF                                                          |    |

|    | 2.2   | 2.2.12 Embedded and Programmable Sensor Calibration.                                                                          |    |

|    | 2.3   | Overview of Academic Reprogrammable Analog Hardware                                                                           |    |

|    |       | 2.3.1 FPAA - University of Toronto (Gulak)                                                                                    |    |

|    |       | 2.3.2 Palmo- University of Edinburgh                                                                                          |    |

|    |       | <ul><li>2.3.3 Evolvable Motherboard – University of Sussex</li><li>2.3.4 PAMA Catholic University of Rio de Janeiro</li></ul> |    |

|    |       | 2.3.4 FAMA Catholic University of Rio de Janeiro                                                                              |    |

|    |       | 2.3.6 FPAA – IMTEK                                                                                                            |    |

|    |       | 2.3.7 FPTA / SRAA– JPL                                                                                                        |    |

|    |       | 2.3.8 FPTA – University of Heidelberg                                                                                         |    |

|    |       | 2.3.9 EPAA – TU Ilmenau                                                                                                       |    |

|    |       | 2.3.10 FG FPAA – Georgia Tech                                                                                                 |    |

|    |       | 2.3.11 FPAA Based OTA-C Filter - Technical University of Gdansk                                                               |    |

|    |       | 2.3.12 FPMA - John Hopkins University                                                                                         | 41 |

|    | 2.4   | Evolvable Hardware                                                                                                            | 42 |

|    | 2.5   | Discussion                                                                                                                    | 47 |

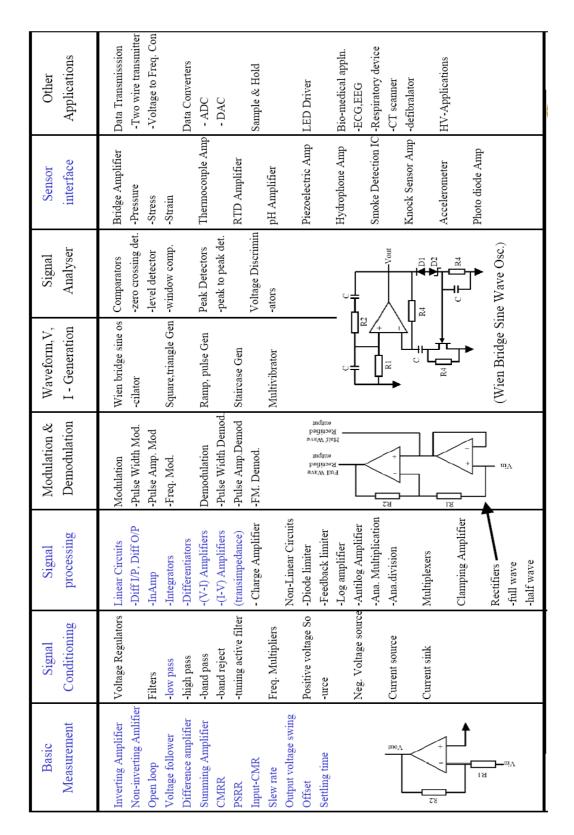

| 3. | Sens  | sor Application Circuits Survey for Resource Distillation                                                                     | 49 |

|    | 3.1   | Introduction to Application Circuits                                                                                          | 50 |

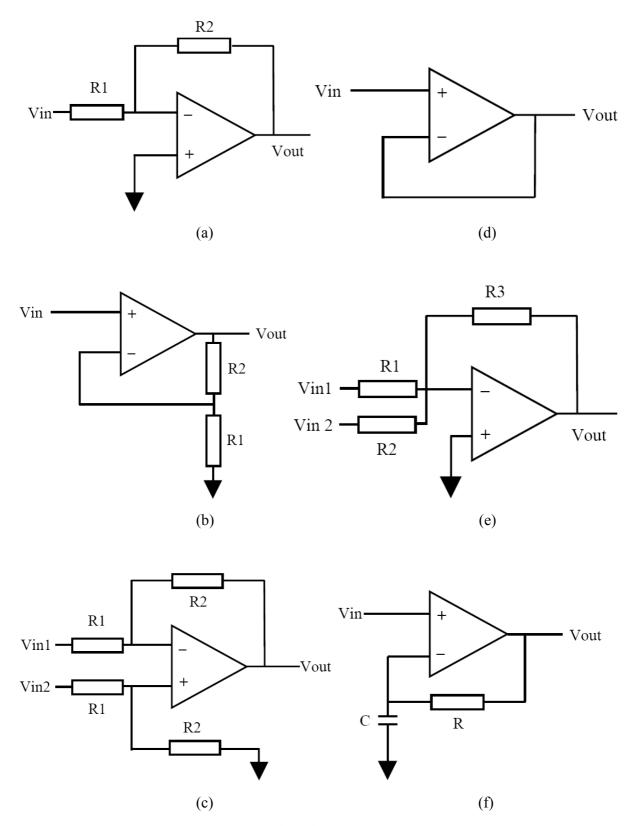

|    | 3.2   | Basic Measurement Circuits                                                                                                    |    |

|    |       | 3.2.1 Inverting amplifier                                                                                                     |    |

|    |       | 3.2.2 Non-inverting amplifier                                                                                                 |    |

|    |       | 3.2.3 Output Voltage Swing                                                                                                    |    |

|     | 3.2.4 | Unity Gain Buffer or Voltage Follower                            | 52 |

|-----|-------|------------------------------------------------------------------|----|

|     | 3.2.5 | Slew Rate                                                        | 54 |

|     | 3.2.6 | Settling Time                                                    | 54 |

|     | 3.2.7 | Input Common Mode Range                                          | 54 |

|     | 3.2.8 | Offset Voltage                                                   |    |

|     | 3.2.9 | Summing amplifier                                                |    |

|     |       | Difference amplifier                                             |    |

|     |       | Open loop Frequency Response                                     |    |

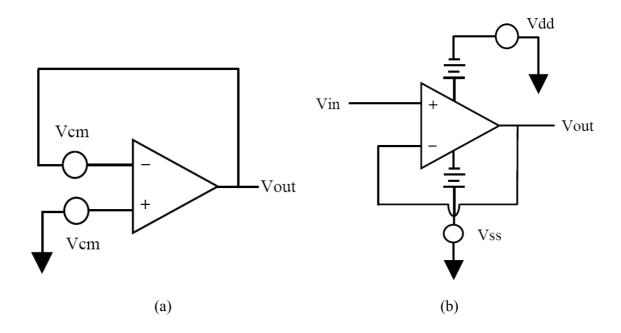

|     |       | Common Mode Rejection Ratio                                      |    |

|     |       | Power Supply Rejection Ratio                                     |    |

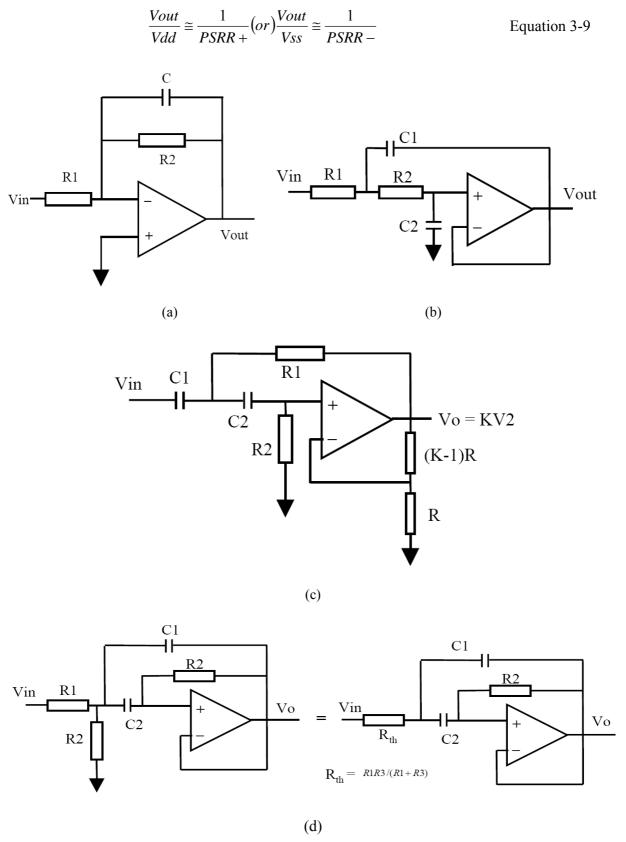

| 3.3 |       | l Conditioning                                                   |    |

|     | 3.3.1 | _                                                                |    |

|     | 3.3.1 | Voltage Regulators                                               |    |

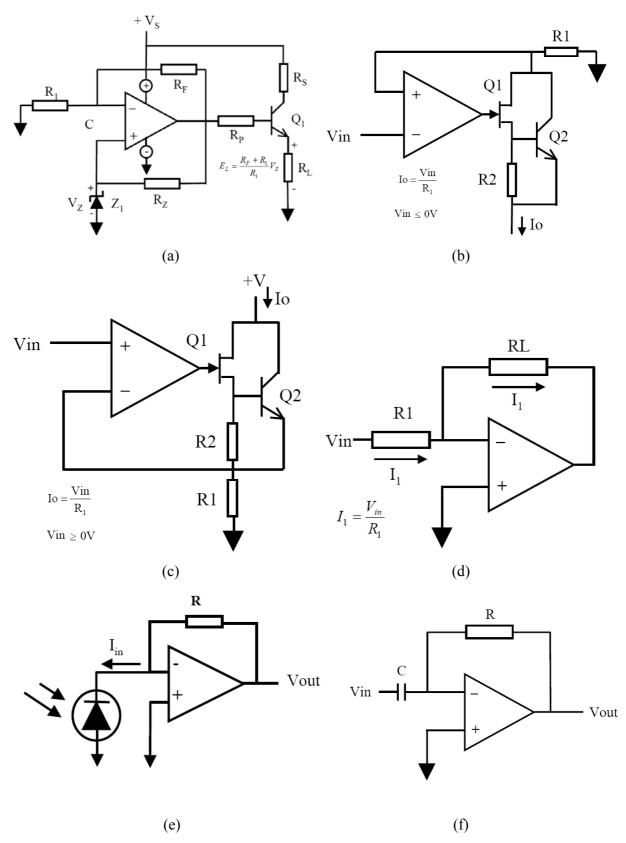

|     | 3.3.3 | Precision Current Sink and Current Source                        |    |

| 3.4 |       |                                                                  |    |

| 3.4 | _     | l Processing                                                     |    |

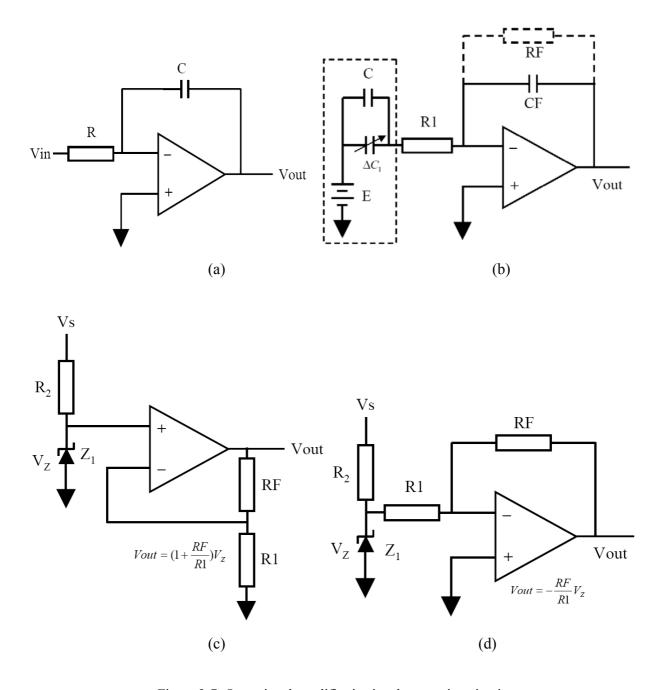

|     | 3.4.1 | Linear Circuits                                                  |    |

|     |       | 3.4.1.1 Voltage – to – Current Converters                        |    |

|     |       | 3.4.1.2 Current – to – Voltage Converter                         |    |

|     |       | 3.4.1.3 Differentiator                                           |    |

|     |       | 3.4.1.4 Integrator                                               |    |

|     |       | 3.4.1.5 Charge Amplifier                                         |    |

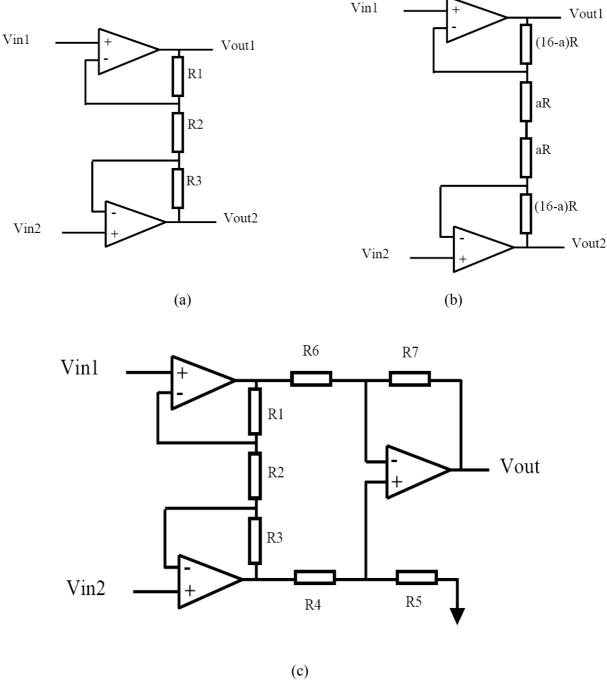

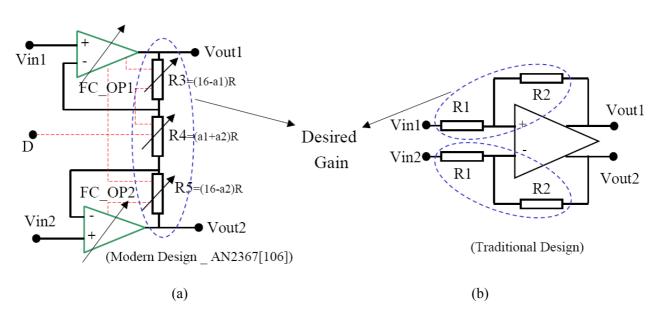

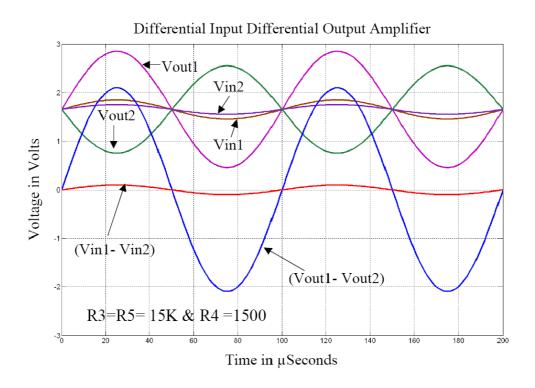

|     |       | 3.4.1.7 Differential Input Differential Output Amplifiers        |    |

|     |       | 3.4.1.8 Instrumentation Amplifiers                               |    |

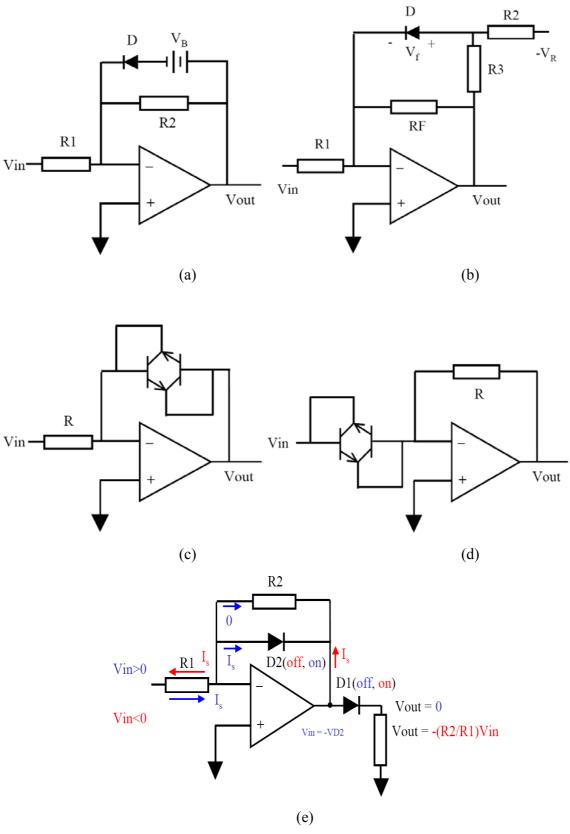

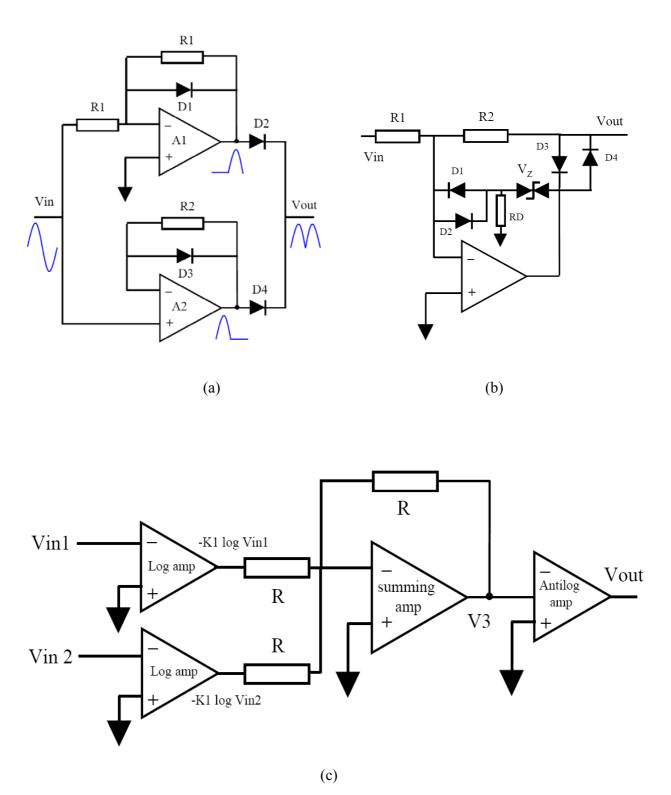

|     | 3.4.2 | Non-Linear Circuits                                              |    |

|     | 3.1.2 | 3.4.2.1 Diode Limiters                                           |    |

|     |       | 3.4.2.2 Feedback Limiters                                        |    |

|     |       | 3.4.2.3 Logarithmic Amplifiers                                   |    |

|     |       | 3.4.2.4 Anti-Logarithmic Amplifiers                              |    |

|     |       | 3.4.2.5 Non-saturating Precision Half Wave Rectifier Circuit     |    |

|     |       | 3.4.2.6 Full Wave Rectifier                                      |    |

|     |       | 3.4.2.7 Clamping Amplifiers                                      | 67 |

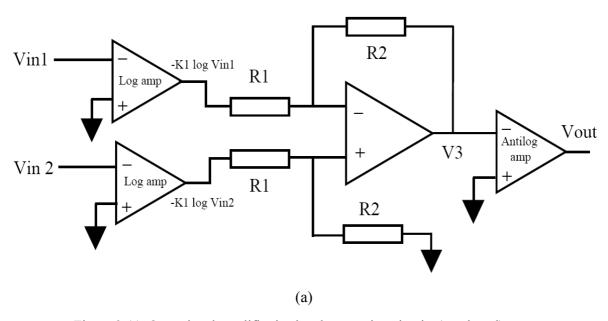

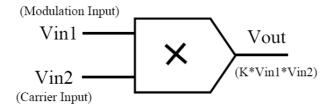

|     | 3.4.3 | Analog Multiplication and Division                               | 69 |

|     | 3.4.4 | Logarithmic Multipliers                                          | 69 |

|     | 3.4.5 | Logarithmic Division                                             |    |

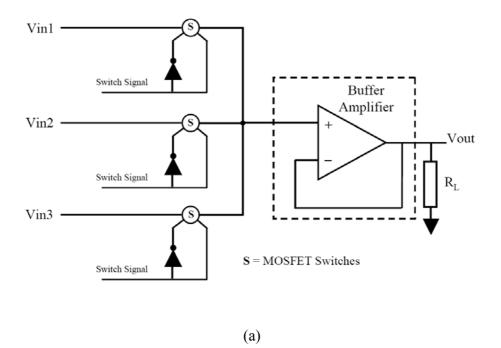

|     | 3.4.6 | Multiplexers                                                     |    |

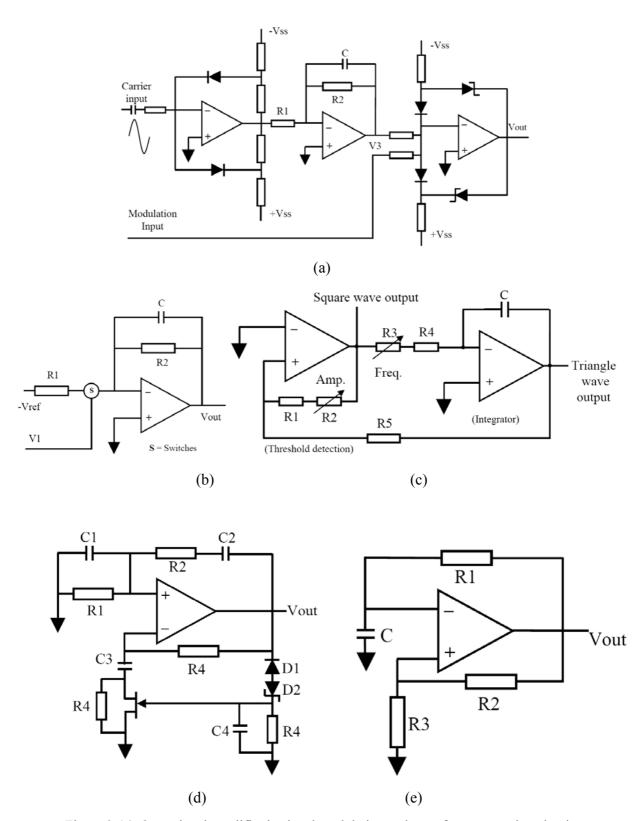

| 3.5 | Modu  | lation and Demodulation                                          |    |

|     | 3.5.1 | Amplitude Modulation                                             | 71 |

|     | 3.5.2 | Pulse Width Modulation                                           |    |

|     | 3.5.3 | Voltage to pulse width modulation with square wave carrier input |    |

|     | 3.5.4 | Pulse Width Demodulation                                         |    |

| 3.6 |       | form Generation                                                  |    |

| 5.0 |       |                                                                  |    |

|     | 3.6.1 | Triangular waveform generation.                                  |    |

|     | 3.6.2 | Wien Bridge sine wave oscillator                                 |    |

| 2.7 | 3.6.3 | Astable Multi-vibrator-Rectangular Waveform Generation           |    |

| 3.7 | Signa | l Analyser                                                       | /4 |

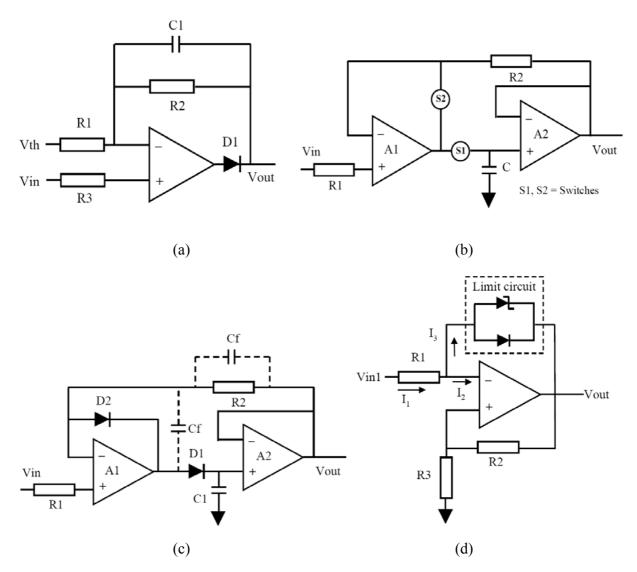

|    |      | 3.7.1 Precision Threshold Detector                                                     | 74 |

|----|------|----------------------------------------------------------------------------------------|----|

|    |      | 3.7.2 Sample and Hold                                                                  | 75 |

|    |      | 3.7.3 Peak detectors                                                                   | 76 |

|    |      | 3.7.4 Comparator/Detectors                                                             | 76 |

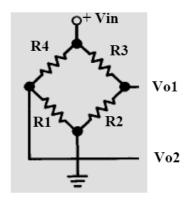

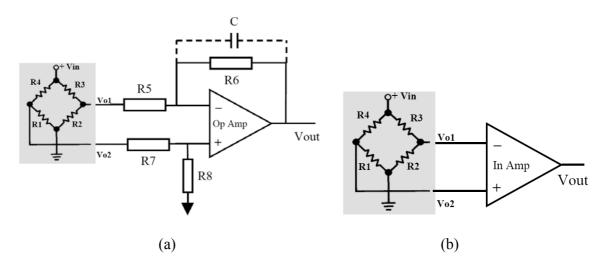

|    | 3.8  | Sensor Interface Amplifiers                                                            | 76 |

|    |      | 3.8.1 Resistive Sensors / Bridge Sensors                                               | 76 |

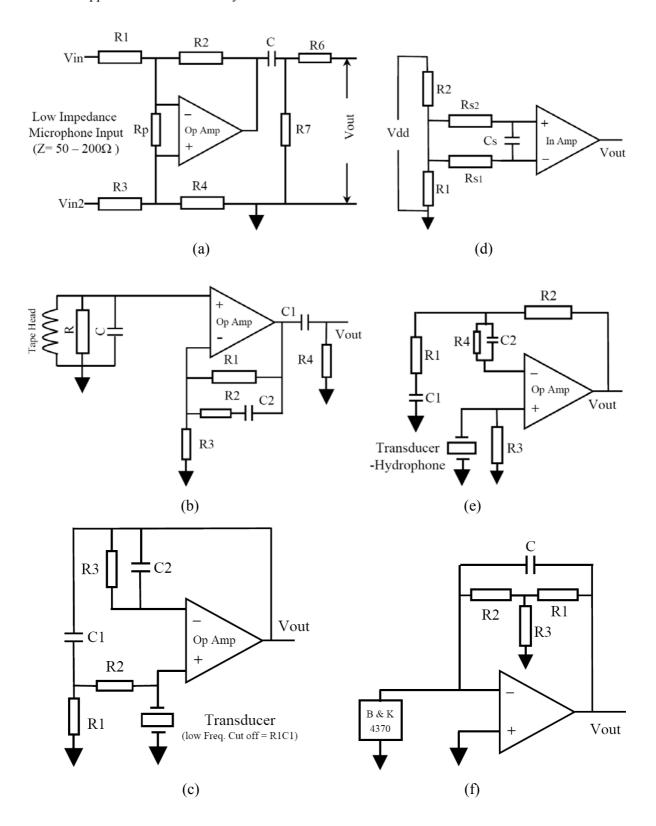

|    |      | 3.8.2 Microphone Pre-Amplifier                                                         | 78 |

|    |      | 3.8.3 NAB Tape Head Pre-Amplifier-inductor sensor                                      | 79 |

|    |      | 3.8.4 Piezoelectric Transducer Amplifier                                               | 79 |

|    |      | 3.8.5 Capacitive Sensor Amplifiers                                                     | 79 |

|    |      | 3.8.6 Hydrophone Amplifier                                                             |    |

|    |      | 3.8.7 Accelerometer – Capacitive Sensor                                                |    |

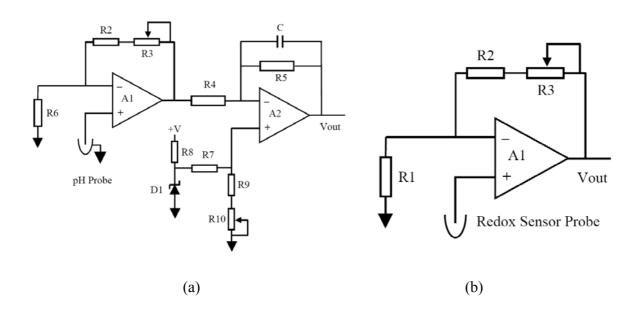

|    |      | 3.8.8 pH Sensor                                                                        |    |

|    |      | 3.8.9 Redox Sensor                                                                     |    |

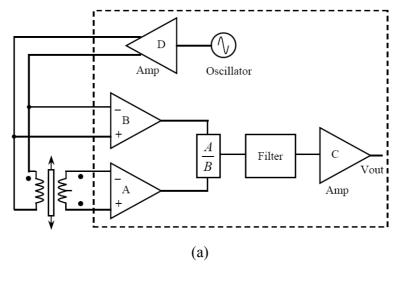

|    |      | 3.8.10 LVDT Signal Conditioners                                                        |    |

|    |      | 3.8.11 Hall Effect Sensors Used as a Rotation Sensors                                  |    |

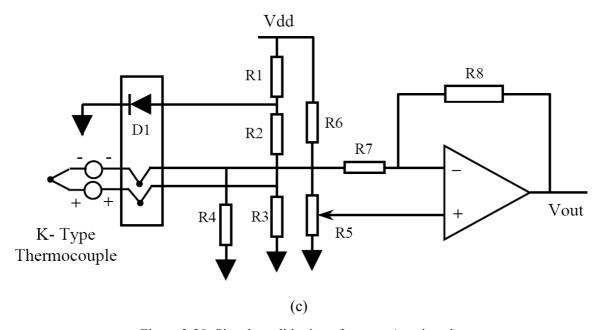

|    | 2.0  | 3.8.12 Thermocouple Amplifiers                                                         |    |

| _  | 3.9  | Resource Distillation                                                                  |    |

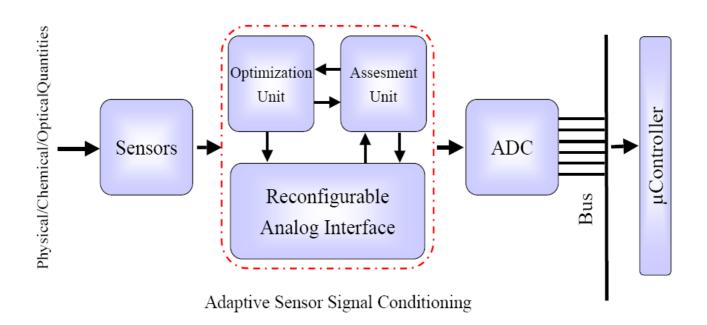

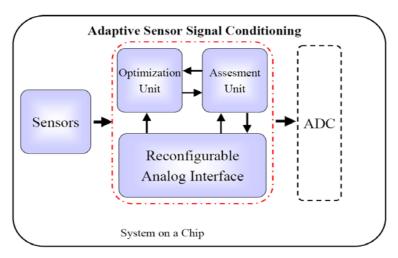

| 4. | Arcl | nitecture of Generic Intelligent and Adaptive Sensor System                            | 91 |

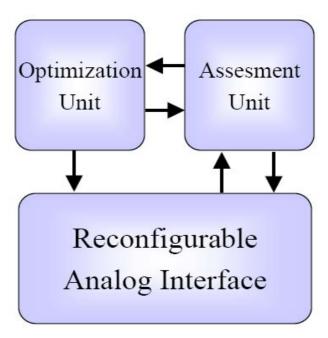

|    | 4.1  | Architecture of Target Self-x Sensor Systems                                           | 91 |

|    |      | 4.1.1 Assessment Unit:                                                                 | 92 |

|    |      | 4.1.2 Optimization Unit:                                                               |    |

|    |      | 4.1.3 Reconfigurable Analog Hardware:                                                  | 92 |

|    |      | 4.1.4 On-the-Fly Calibration through Dynamic Reconfigurable Analog Interface           |    |

|    |      | Hardware                                                                               |    |

|    | 4.2  | Architecture of the Aspired Generic/Universal Multi-sensor Signal Conditioner          |    |

|    |      | 4.2.1 Abilities of our (aspired) Generic - "One for all" Sensor Interface Electronics. |    |

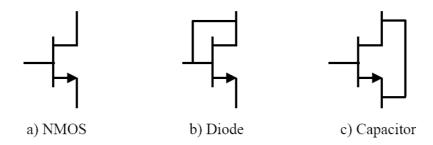

|    | 4.3  | Devices in CMOS Technology                                                             |    |

|    |      | 4.3.1 Transistors                                                                      |    |

|    |      | 4.3.2 Resistors                                                                        |    |

|    |      | 4.3.3 Capacitors                                                                       |    |

|    |      | 4.3.4 Matching of Resistor and Capacitors                                              |    |

|    | 4.4  | First Generation Programmable Basic Building Blocks                                    |    |

|    |      | 4.4.1 Programmable Transistors Array                                                   |    |

|    |      | 4.4.2 Programmable Resistors and Capacitors                                            |    |

|    |      | 4.4.3 Switches in Programmable Analog Devices                                          |    |

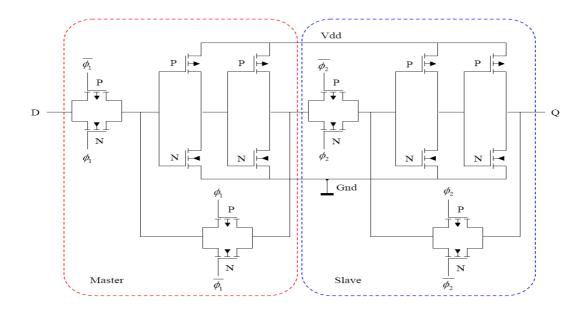

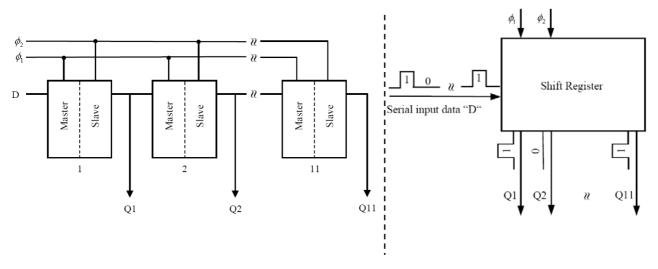

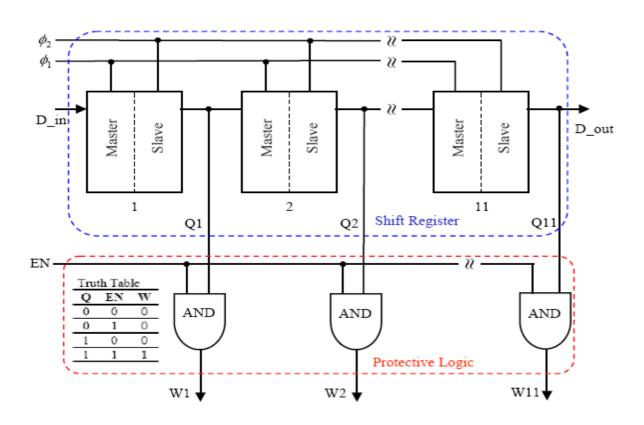

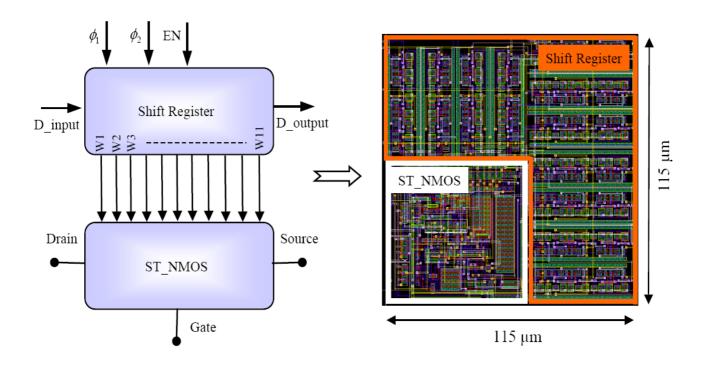

|    |      | 4.4.4 Shift Register for Sequential Device Selection                                   |    |

|    |      | 4.4.5 Comparison of Area Requirement with 6T-SRAM Cell.                                |    |

|    |      | 4.4.6 CMOS Operational Amplifiers                                                      |    |

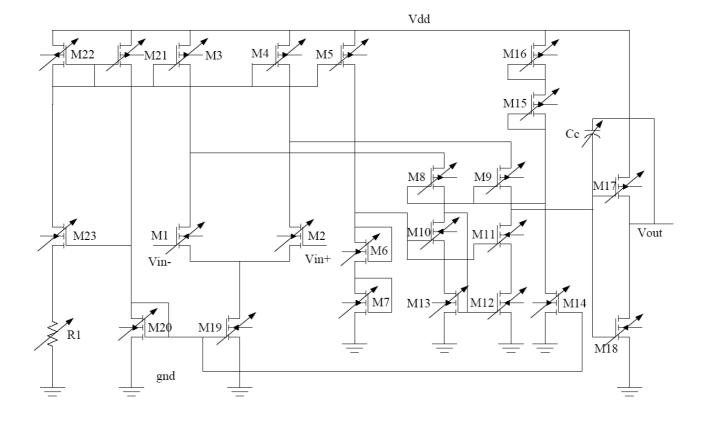

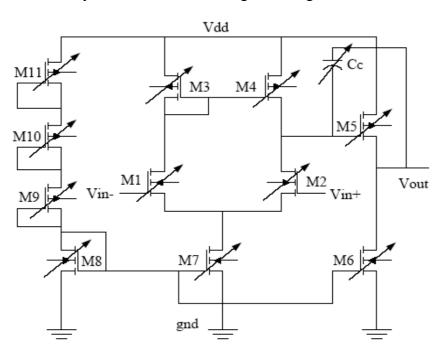

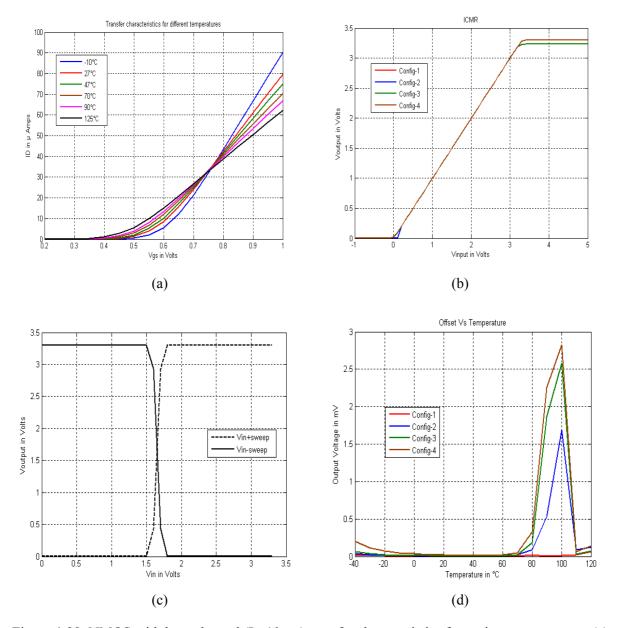

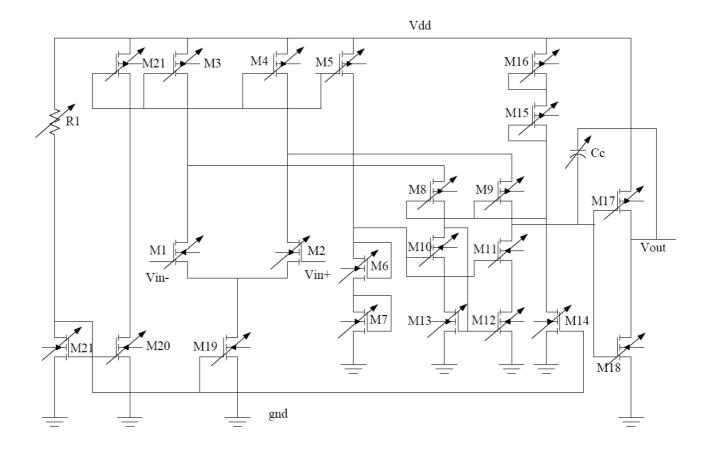

|    |      | 4.4.6.1 Miller Operational Amplifier                                                   |    |

|    |      | 4.4.6.2 Selective Node Flexibility of Op Amp                                           |    |

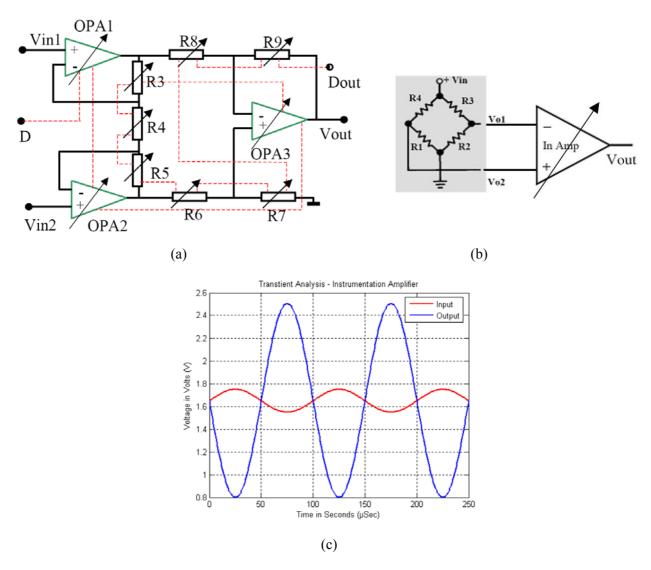

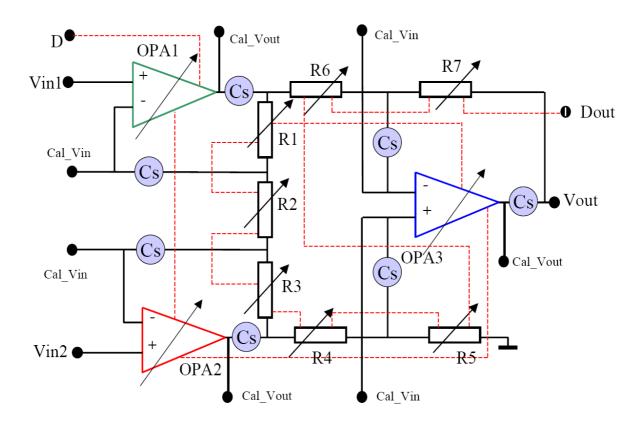

|    |      | 4.4.7 Instrumentation Amplifier                                                        |    |

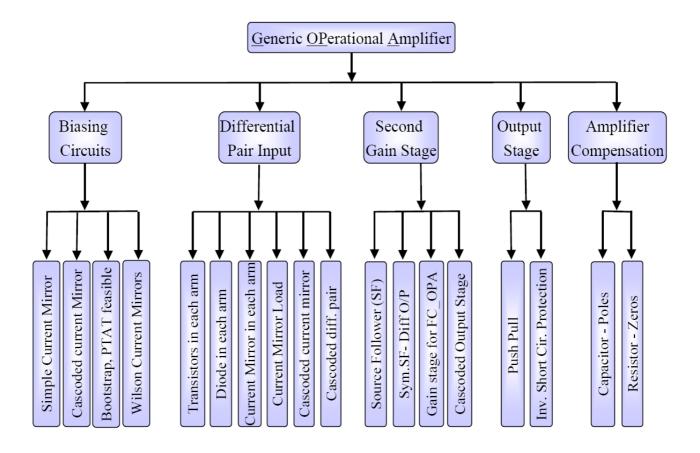

|    | 4.5  | Generic OPerational Amplifier – "GOPA"                                                 |    |

|    |      | 4.5.1 Hierarchical Switches/Topological Switches.                                      |    |

|    |      | IIII III III O III III III III III                                                     |    |

|    |     | 4.5.2 Various Amplifier Structure                                     | 116 |

|----|-----|-----------------------------------------------------------------------|-----|

|    | 4.6 | Low Power Design                                                      | 116 |

|    |     | 4.6.1 Low Power Configurations                                        | 119 |

|    |     | 4.6.2 Sub-threshold / Weak Inversion Operation of Two Stage Op Amp    | 121 |

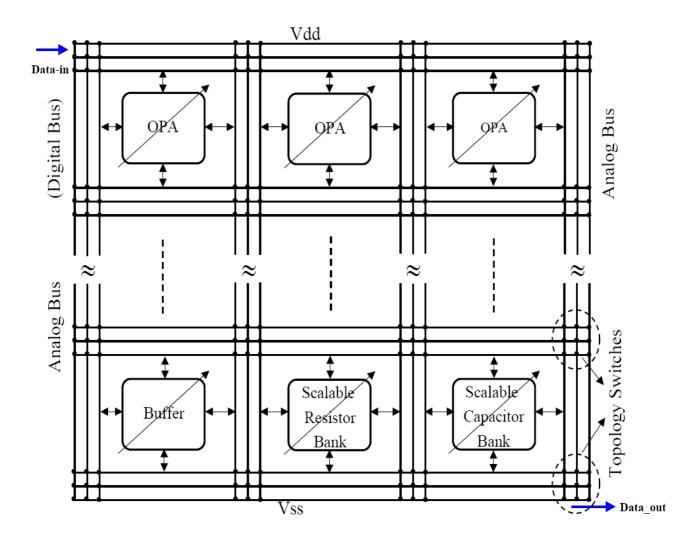

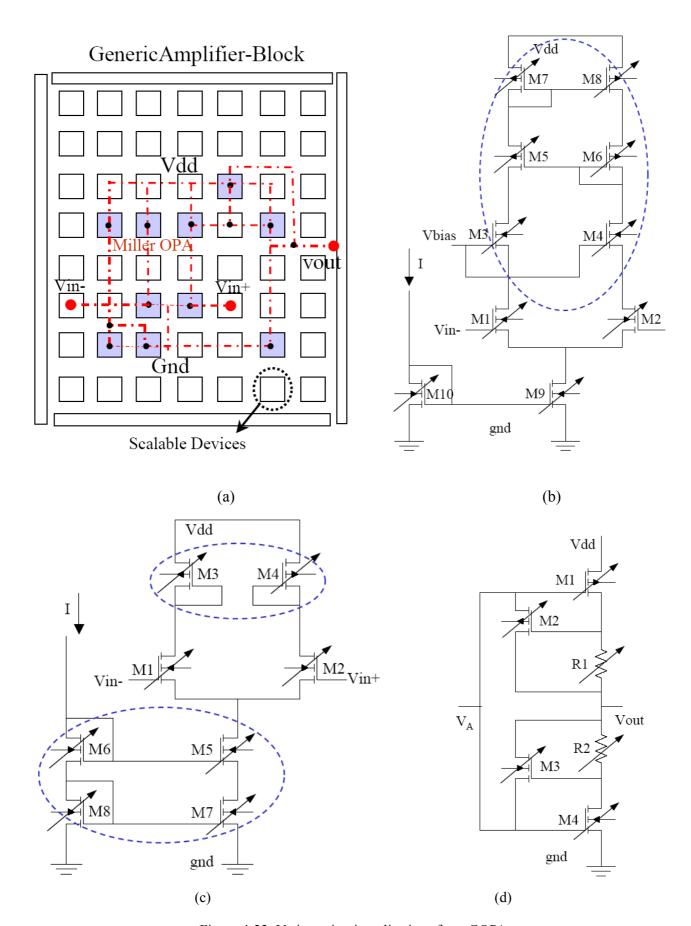

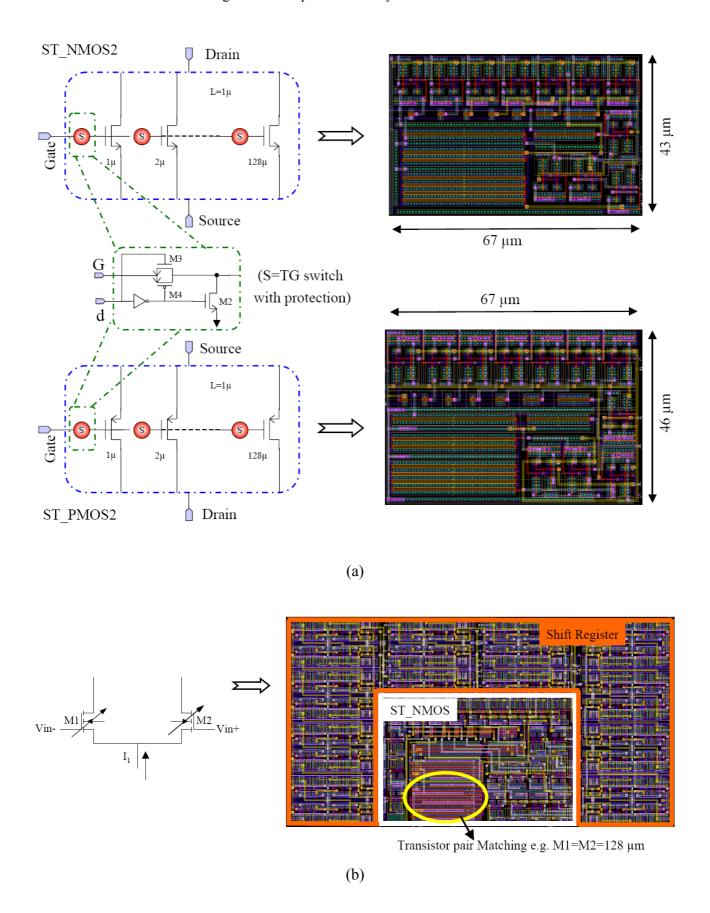

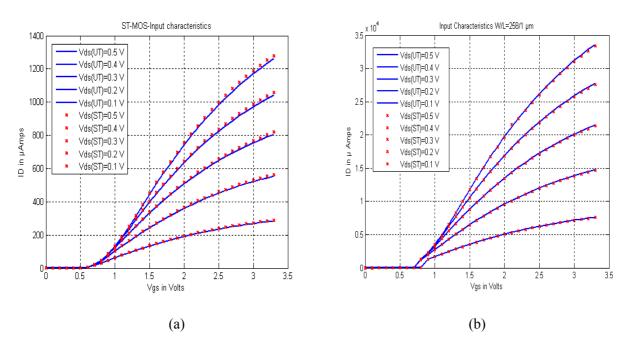

|    | 4.7 | Second Generation Programmable Basic Building Blocks                  | 123 |

|    |     | 4.7.1 Programmable Active and Passive Devices                         | 123 |

|    |     | 4.7.2 Transmission Gate Switches                                      | 128 |

|    |     | 4.7.3 Amplifiers in FPMA2                                             | 130 |

|    |     | 4.7.3.1 Miller OPA                                                    |     |

|    |     | 4.7.3.2 FC_OPA                                                        |     |

|    |     | 4.7.4 Hierarchical Design                                             |     |

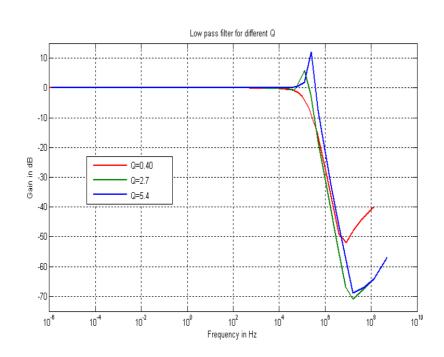

|    |     | 4.7.4.1 Low Pass Active Filter                                        |     |

|    |     | 4.7.4.2 Fully Differential Operational Amplifiers                     |     |

|    |     | 4.7.4.4 On-the-Fly Hierarchical Calibration – Offline and Online      |     |

|    |     | 4.7.4.5 "Soft Sleep" mode – Low Power Design Issues                   |     |

|    |     | 4.7.5 Noise Issues.                                                   |     |

|    |     | 4.7.5.1 Signal Integrity Challenges                                   | 139 |

|    |     | 4.7.5.2 Matched layout                                                |     |

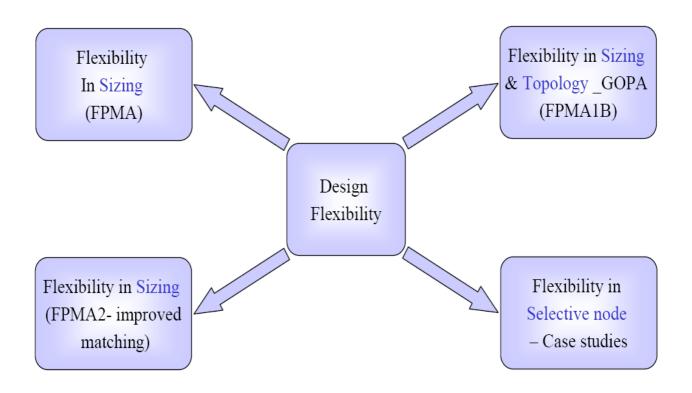

|    | 4.8 | Flexibility, Area and Fault Tolerance                                 |     |

|    |     | 4.8.1 Modes of Flexibility                                            |     |

|    |     | 4.8.2 Fault Tolerance and Area                                        |     |

|    | 4.9 | Evolvable System-on-Chip Sensor System / Generic off the Shelf Chip   | 142 |

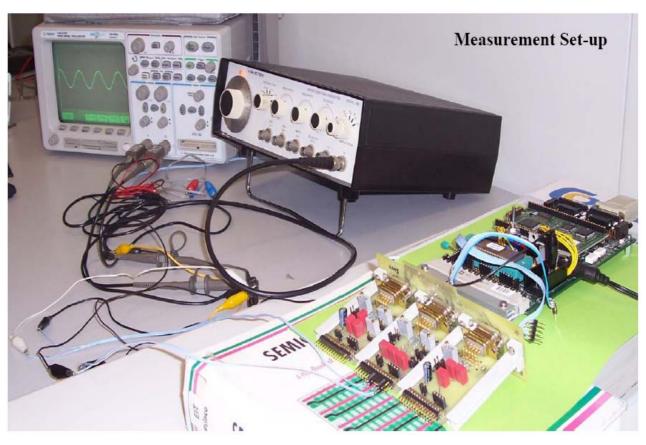

| 5. | Exp | erimental Set Up and Results                                          | 144 |

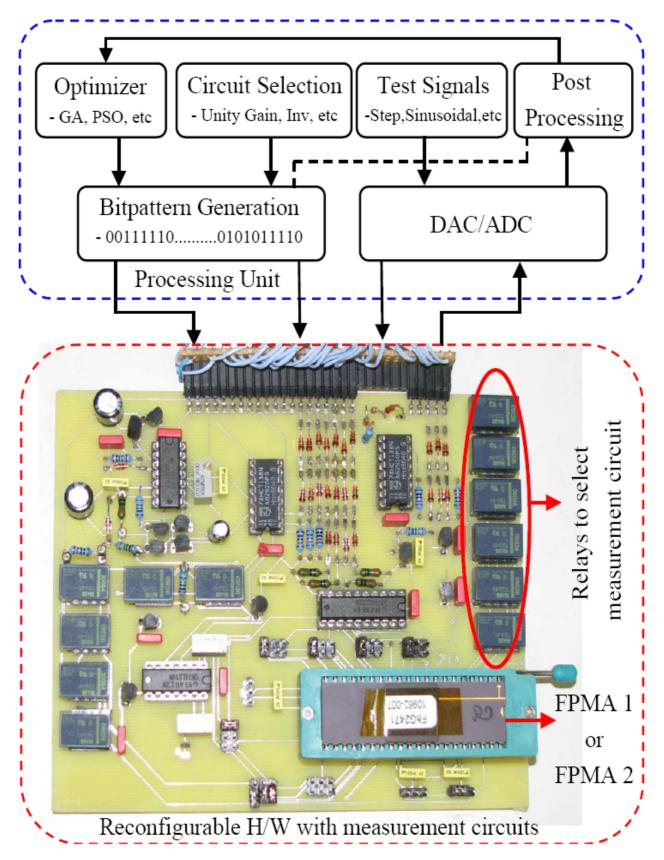

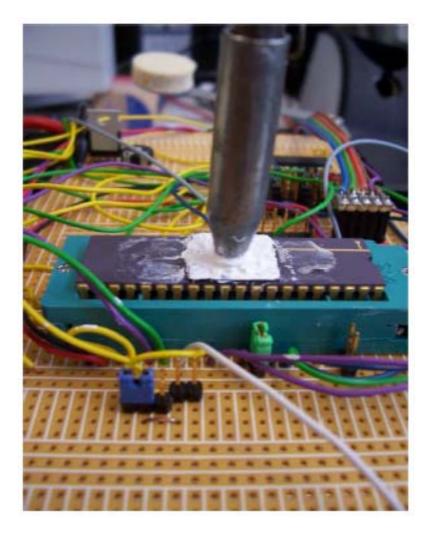

|    | 5.1 | Dynamic Reconfigurable Stand Alone Board                              | 144 |

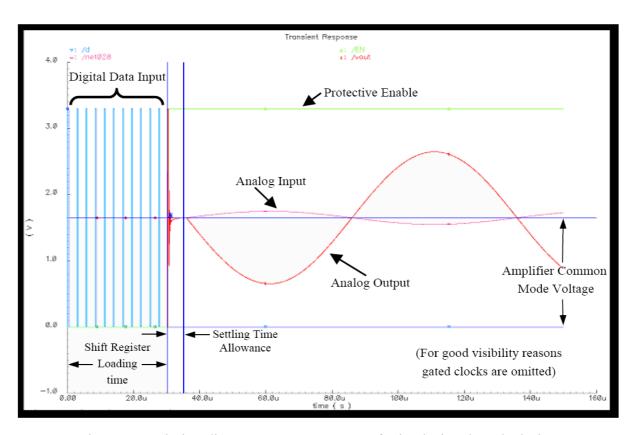

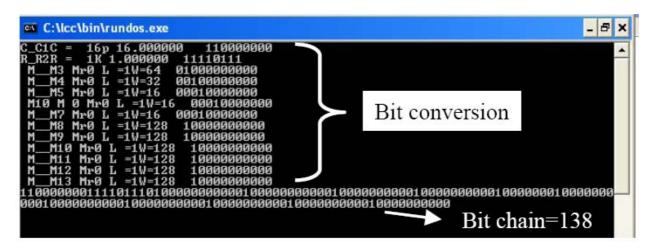

|    | 5.2 | Mixed Signal Test Sequence                                            | 146 |

|    | 5.3 | Measured Results of FPMA                                              | 148 |

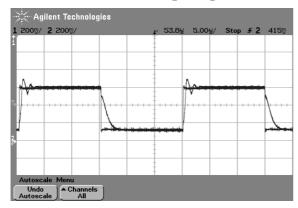

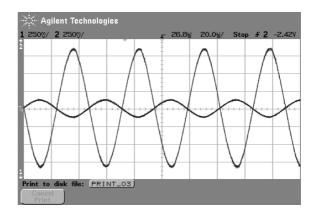

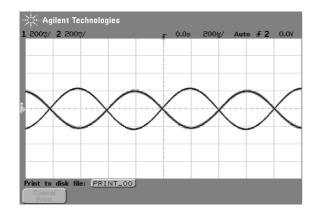

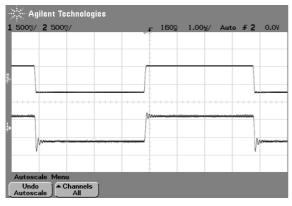

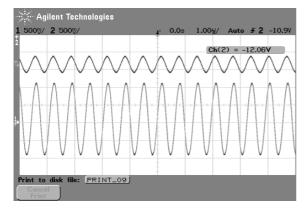

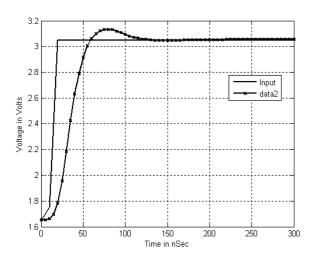

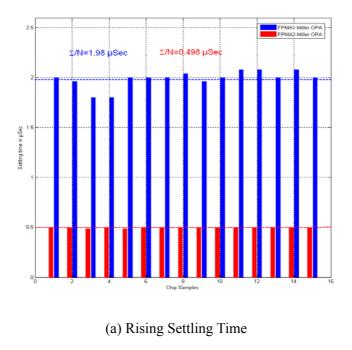

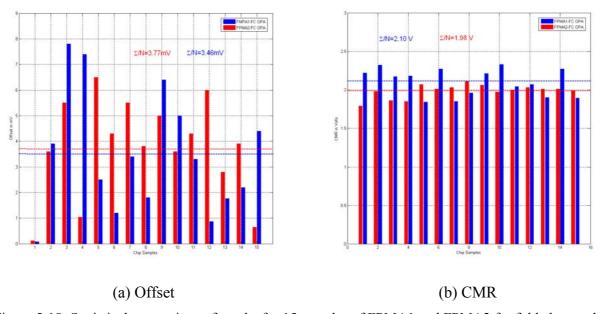

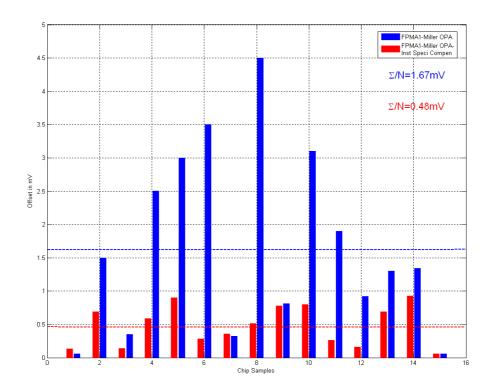

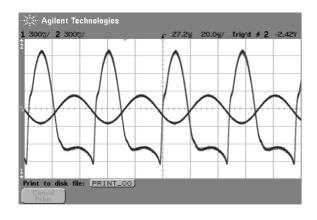

|    |     | 5.3.1 Results of Miller Op Amp                                        | 148 |

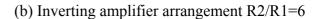

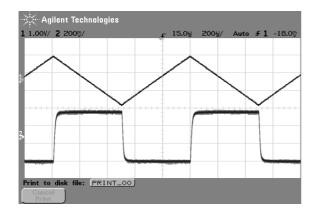

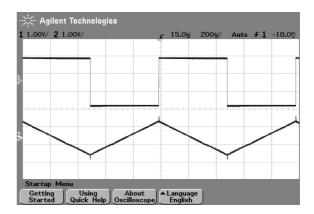

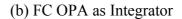

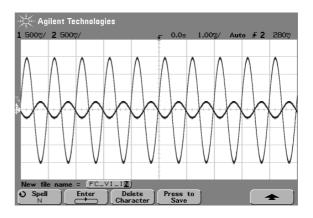

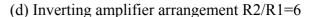

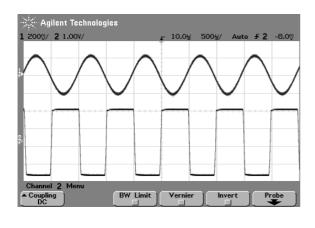

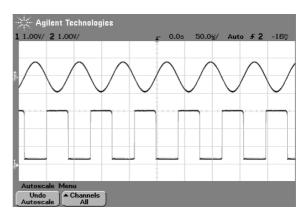

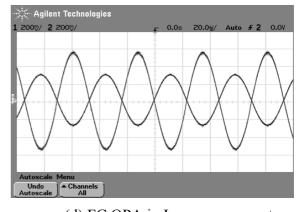

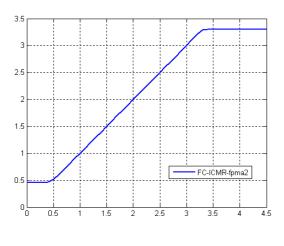

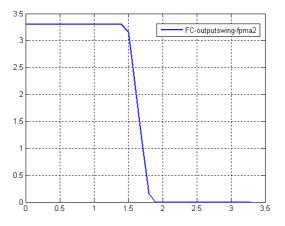

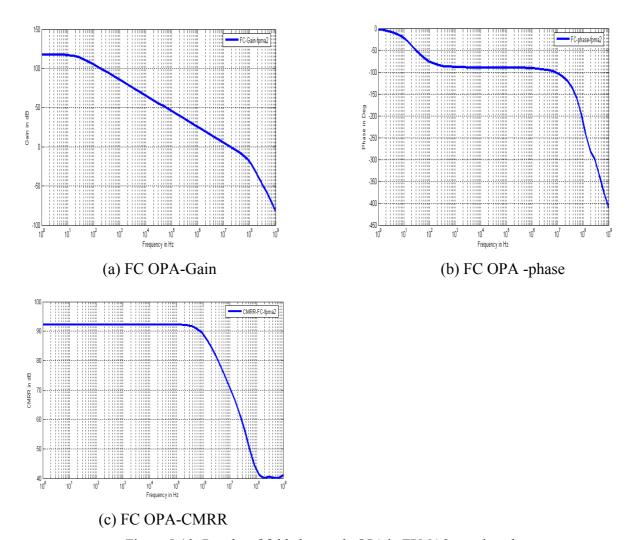

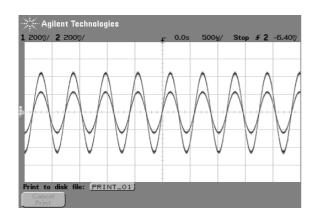

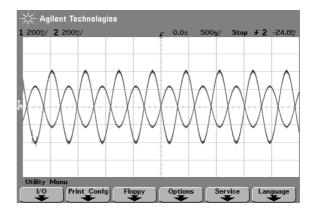

|    |     | 5.3.2 Results of Folded Cascode Op Amp                                | 150 |

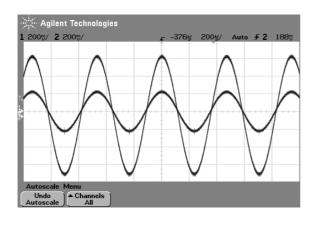

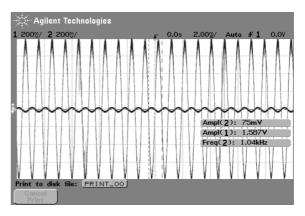

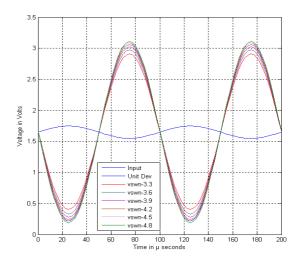

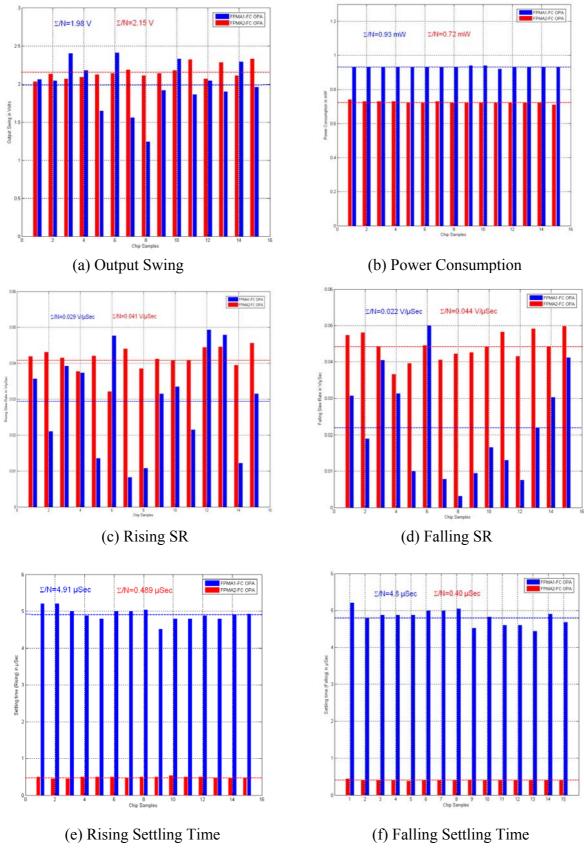

|    | 5.4 | Measured Results of FPMA2                                             | 151 |

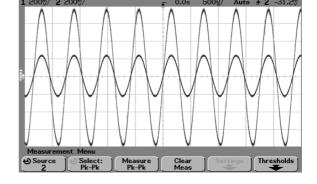

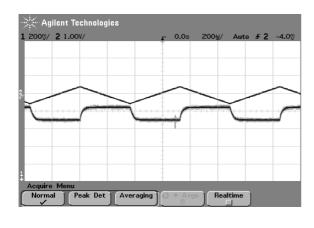

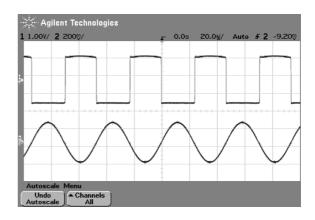

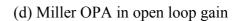

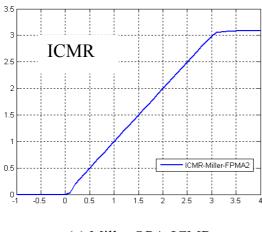

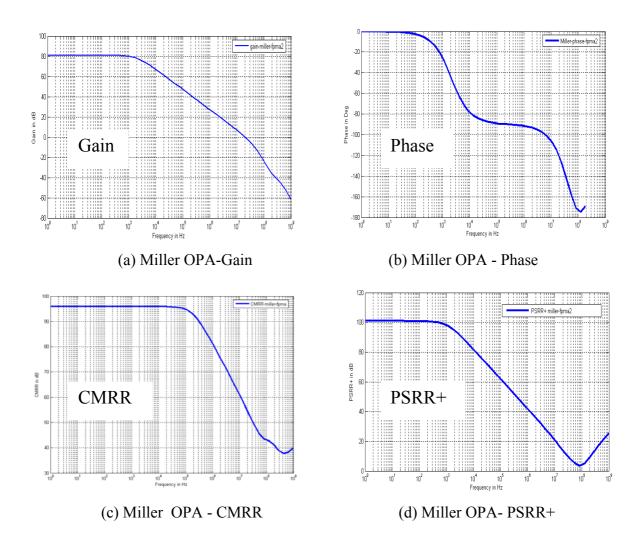

|    |     | 5.4.1 Results of Miller Op Amp                                        | 151 |

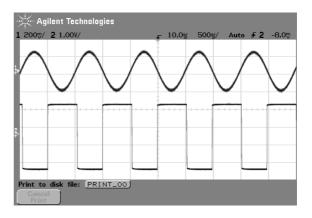

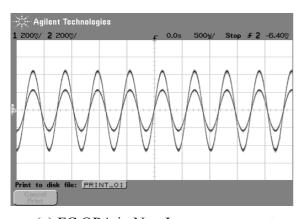

|    |     | 5.4.2 Results of Folded Cascode Op Amp                                | 153 |

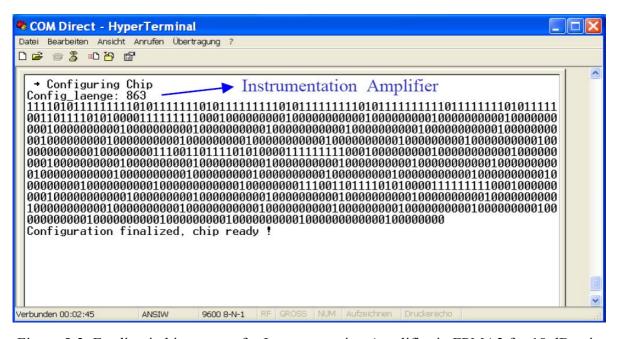

|    |     | 5.4.3 Results of Instrumentation Amplifier                            |     |

|    |     | 5.4.3.1 Hierarchical Calibration Results of instrumentation Amplifier |     |

|    | 5.5 | Reliability Analysis and Drift Compensation                           |     |

|    |     | 5.5.1 Yield Considerations for Reconfigurable Circuits                |     |

|    |     | 5.5.2 Instance Specific Drifts and Drift Compensation                 |     |

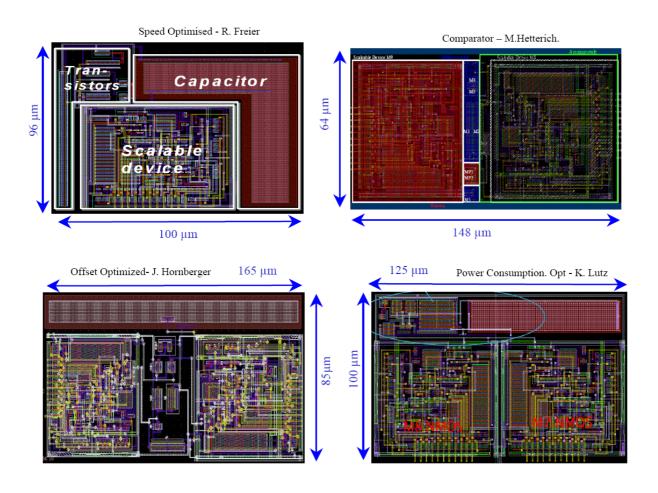

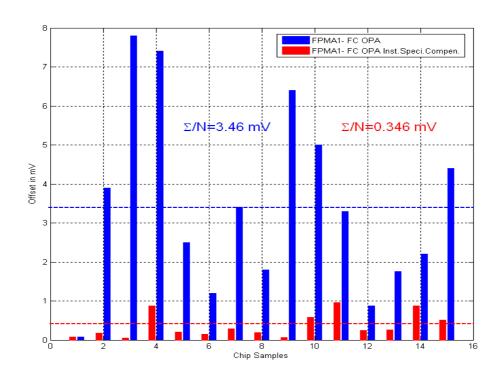

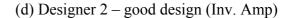

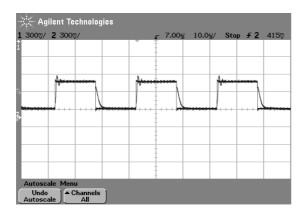

| 6. | Tru | e Front to Back Analog IC Designers' Training                         | 166 |

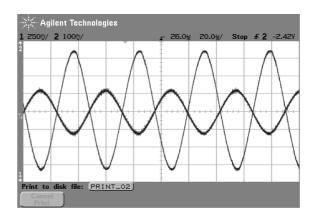

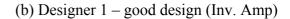

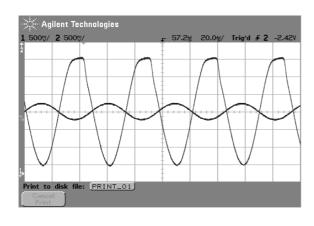

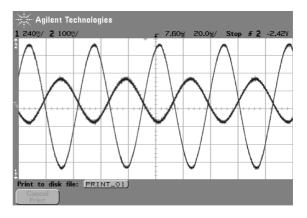

|    | 6.1 | First Generation FPMA involved in Teaching                            | 166 |

|    | 6.2 | Second Generation involved in Teaching FPMA2                          | 171 |

| 7. | Con | clusion and Future Works                                              | 174 |

|    | 7.1 | Conclusion                                                            | 174 |

|    | 7.2 | Novelties and Achievements                                            | 175 |

|    |     |                                                                       |     |

|    | 7.3 | Future works and Improvements                                         | 17  |

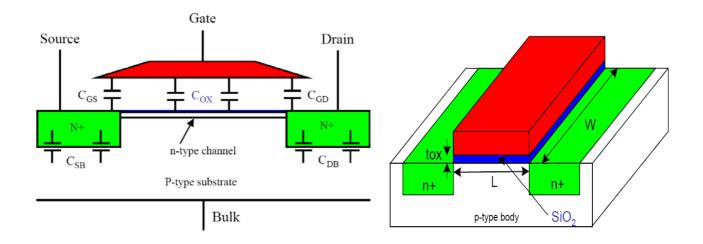

|     |       | 7.3.1 Switches                                            | 176 |

|-----|-------|-----------------------------------------------------------|-----|

|     |       | 7.3.2 Revision of the basic building block arrays         | 176 |

|     |       | 7.3.3 Separate Supply Voltage for Digital and Analog      | 177 |

|     |       | 7.3.4 Improved / Specialized Circuit Topologies           | 177 |

|     |       | 7.3.5 From Self-X Sensor System to Self-X Actuator System | 177 |

| 8.  | App   | endices                                                   | 181 |

|     | 8.1   | Appendix A:                                               | 181 |

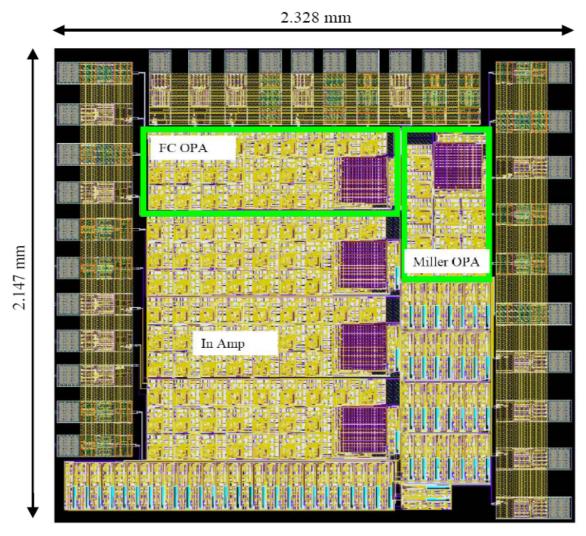

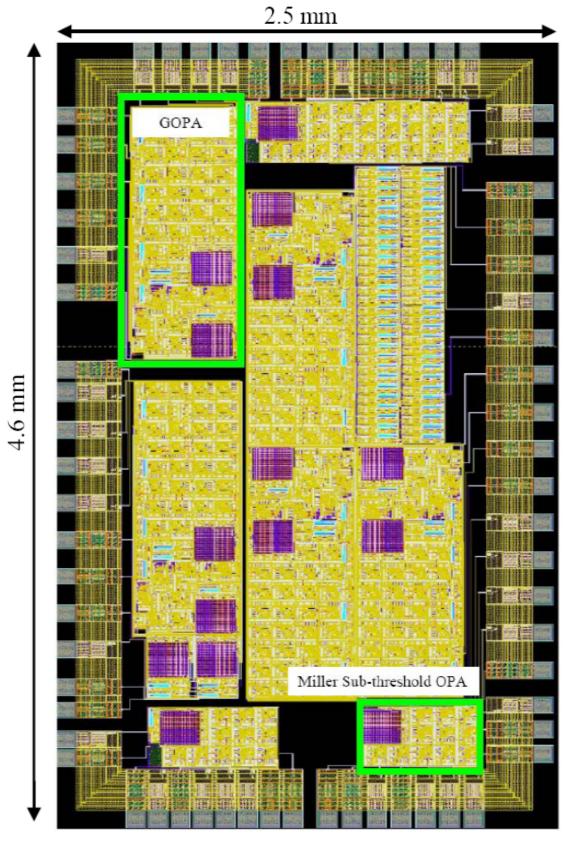

|     |       | 8.1.1 FPMA1 Chip Layout                                   |     |

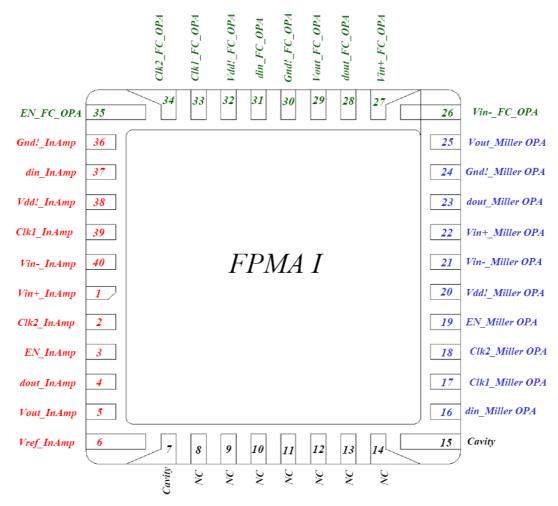

|     |       | 8.1.2 FPMA1 Chip Foot Prints                              |     |

|     |       | 8.1.3 I/O Pads and Associated Signal Type for FPMA1       | 182 |

|     |       | 8.1.4 FPMA1B Chip Layout                                  | 183 |

|     | 8.2   | Appendix B:                                               | 184 |

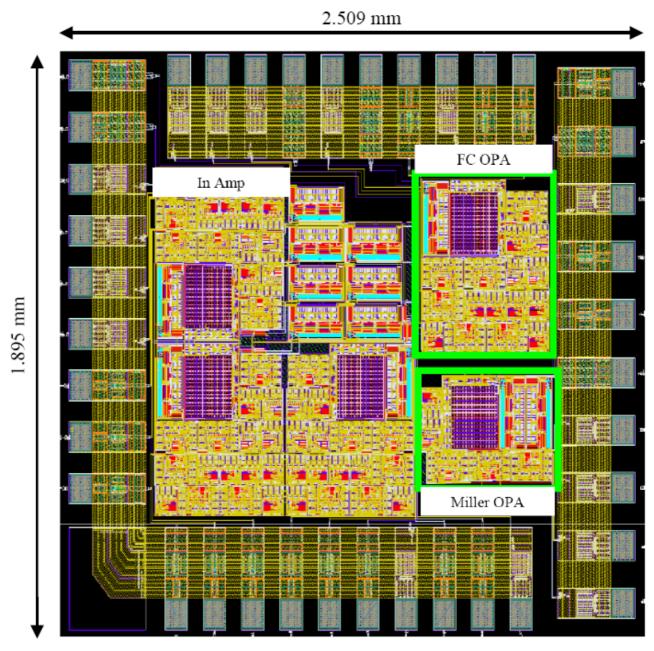

|     |       | 8.2.1 FPMA2 Chip Layout                                   | 184 |

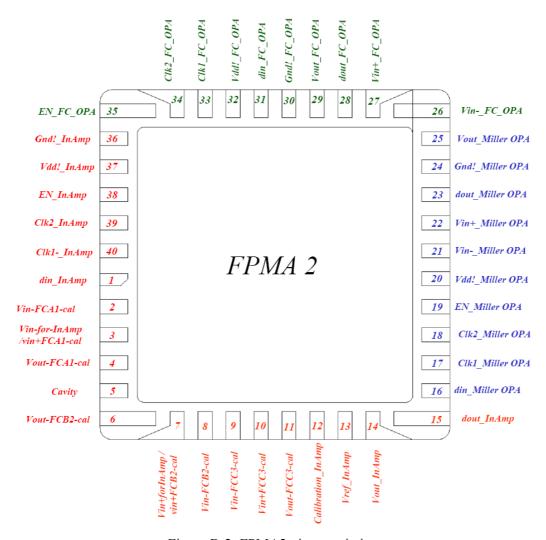

|     |       | 8.2.2 FPMA2 Chip Foot Print                               | 185 |

|     |       | 8.2.3 I/O Pads and Associated Signal Type for FPMA2       | 185 |

|     | 8.3   | Appendix C:                                               | 186 |

| 9.  | Kurz  | zfassung in Deutscher Sprache                             | 187 |

| 10. | Bibli | iography and Indices                                      | 196 |

|     | 10.1  | Bibliography                                              | 196 |

|     | 10.2  | Index of Tables                                           | 205 |

|     | 10.3  | Index of Figures                                          | 206 |

|     | 10.4  | List of often used Abbreviations                          | 210 |

#### 1. Introduction

# 1.1 Signal Conditioning in Integrated Smart Sensor System

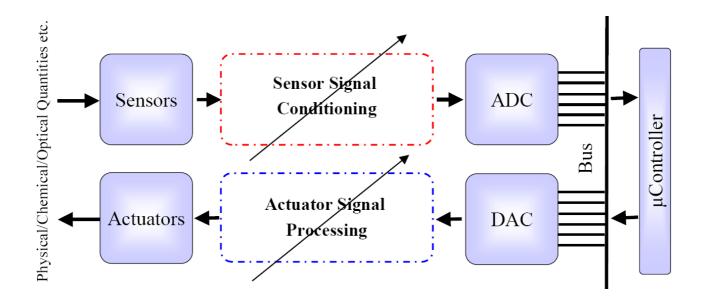

Basically, sensors are all transducers which convert physical, chemical, geometrical, optical quantities into electrical signals. Today's modern sensors find their field of application in automobile engineering, house / industry automation, and measurement and control, etc [1]. Simple realization of a smart sensor needs the following functional modules,

- 1. Sensors in a variety of materials and packaging technologies, denoted as the Sensing Element

- 2. Analog interface electronics (Amplifier)

- 3. Signal Conversion (Analog to Digital)

- 4. Bus and Bus interface to microcontroller for further processing and calibration.

The sequence of signal processing in a smart sensor system is depicted in Figure 1-1. For the sake of simplicity, actuator sections in not shown in this block diagram.

Figure 1-1: Functional block diagram of an integrated smart sensor

Ideally speaking sensors are designed to be linear, but in real world applications, sensors and sensor electronics are not ideal. This means that there are drifts and deviations in the measured quantity. The cause for errors in measuring the quantities can be several. Based on the source of the errors they are classified as systematic and random errors. Most of the systematic errors can be compensated through trimming/calibration. Whereas, random errors are difficult to trace, model and eliminate, like for example, errors due to noise. Some causes of errors in a sensor system are listed below.

1. Static and dynamic deviations like aging, doping concentration and environmental influences.

- 2. Manufacturing tolerances / Process variations.

- 3. Digitization errors, if at all the sensor signal has to be digitized.

### 1.1.1 Trimming / Calibration Techniques

Due to the above mentioned errors and due to the variations witnessed and due to the change in operating conditions for example temperature, the system tend to deviate from its normal functionality. In order to restore the system functionality back into its normal operation, careful design at the manufacturing stage or trimming/calibration is essential. The term calibration can be defined in several ways. One such definition is given as, the process of relating the measurement or sensor signal to the physical input signal in precise well defined units is referred to as *calibration* [59]. Almost all kind of sensors need some kind of calibrations.

Table 1-1: Overview of offset voltage trimming process (from [60])

| S.<br>Nr | Technique                                                                                              | Trimmed at: | Special<br>Processing | Resolution |

|----------|--------------------------------------------------------------------------------------------------------|-------------|-----------------------|------------|

| 1        | Laser Trimming (cutting resistor with laser)                                                           | Wafer       | Thin Film             | Continuous |

| 2        | Zener Zap  (Use a voltage to create a short circuit/bypass across a trim transistor)                   | Wafer       | None                  | Discrete   |

| 3        | Link Trim (Cutting metal or poly silicon to remove connection)                                         | Wafer       | Poly                  | Discrete   |

| 4        | EEPROM  (Stores value in a memory to address DAC to adjust I or V)                                     | Wafer       | EEPROM                | Discrete   |

| 5        | Chopper-Auto-Zero Amplifier  (Dynamic adjustment using Capacitors, switches, and additional Amplifier) | N/A         | CMOS                  | Continuous |

| 6        | DigiTrim  (Trade mark of Analog Devices for DAC based trimming)                                        | Wafer       | NONE                  | Discrete   |

#### 1 Introduction

Most of today's electronic devices like mobile phones are moving to low operating voltages. This leaves less tolerance for errors and increases the accuracy of the system. This makes the calibration procedure very important. Moreover, sensor themselves and the analog interface electronics are prone to manufacturing conditions, mismatches, environmental influences, etching rate, doping concentration, aging and temperature influences. Conventional calibration techniques uses adjustable potentiometers like AD8403 [60] or laser trimmed resistors [59]. The so performed conservative approaches suffer from severe drawbacks like slow deployment time due to manual interventions, static and high cost etc. This is especially true when it comes to analog circuits like amplifiers, where the offset of an amplifier is a very crucial accuracy parameter. Table 1-1 illustrates the summary of some offset voltage trimming process.

More improved approaches [52] adapt these established procedures by compensation techniques during the actual phase of operation in the name of self-diagnosis / self-calibration [61]. In particular, self-calibrating techniques are well established in analog-digital converter [62]. To put in simple words, the output of the ADCs is not affected by static or dynamic deviations of the system. Fortunately, self calibrating ADCs are available to address the problem. Choice of ADCs topology, speed and resolution has impact on the system. For example, a pipelined ADC can be used in place of a simple flash ADC thereby enjoying better speed during conversion. It is also a normal practice to use sigma-delta ADC, because the sigma-delta ADC allows modification of the transfer by summing several analog input signals which are modulated by digitally generated bit stream signals. The sigma-delta technique can also be applied in the digital bit stream generation, which makes it possible to calibrate very accurately. However, the suggested configurations only allow for low order of calibrations. It is acknowledged that digital compensation is the most attractive technique for high resolution sensor calibration. The implementation in software for a digital processing enables advanced, complex but flexible correction of sensor signals [59].

More flexibility both for rapid prototyping as well as implementation potential of self-x features like self-calibration, self-healing etc., comes from block level granular approach, called Field Programmable Analog Array, which uses digitally programmable passive components and amplifier building blocks in discrete time domain. Commercially available Anadigm chip [45] is the best-suited example. More information about this approach and other existing field programmable analog arrays are described in chapter 2.

Most recent approaches come from the field of *evolutionary electronics*, where circuit synthesis are carried out by learning procedures in a suitable flexible transistor level granular hardware structure called Field Programmable Transistor Arrays. So far there are two versions of FPTA available, first version comes from JPL group [63] and the second version from University of Heidelberg group [64]. More information about this transistor level programmable structures are explained in chapter 2 [42] [29].

#### 1.2 Motivation of this thesis

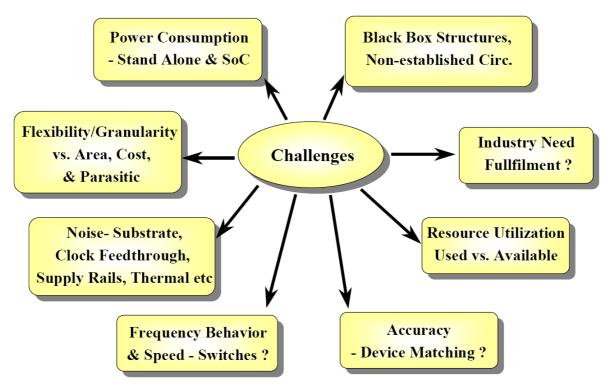

State-of-the-art hardware evolution uses a course grained or fine grained circuit structures as discussed in chapter 2 for automatic synthesis of analog circuits. Both the approaches has their own plus and minuses. Fine granular approaches for instance as described in chapter 2, in spite of yielding very good results, suffer from drawbacks which makes it, to be applicable for industries at a really high expenses. Some factors affecting to the industrial applicability and acceptance of the concept are listed below. The schematic representation of the challenges imposed on the state of the art of analog evolvable hardware is shown in Figure 1-2.

- 1. Too much flexibility becomes a design challenge, higher manufacturing cost and more parasitic.

- 2. Excessive use of switching resources hindrance in frequency behavior of the system and unwanted noise induced by switching activities into the system.

- 3. Large on-chip memory requirement.

- 4. Remains a perfect black box like structure, hiding the evolved circuit topology behind the performance, which are sometime peculiar and are not acknowledged by industries.

- 5. The approach starts to evolve every time from scratch, eventually consuming more time.

Figure 1-2: Challenges imposed on the state of the art of analog evolvable hardware

#### 1 Introduction

Whereas in case of coarse grained programmable structures, only partial flexibility is observed. This can be easily understood by studying the case of an operational amplifier circuits. An operational amplifier connected in a programmable feedback network has the advantage of gain adjustment or variable gain. But instead, rest or most of the other important performance parameters of operational amplifier remains non-programmable. Moreover, recovering the internal offset is a very crucial factor in these approaches. This implies that programmability at course granular level is limited. The limitations can be eliminated through inclusion of a variety of basic configurable blocks at the expense of more silicon.

#### 1.3 Aims of this thesis

The challenges and drawbacks of the existing programmable / evolvable analog approaches mentioned in the previous section forms the backbone and aim of this research work and are listed below.

- Investigation and advance of industrial application potential of reconfigurable self-x analog circuits. Collection of application circuits, sizing requirements of these circuits.

- Reconfigurable H/W with appropriate granularity.

- Reconfigurable H/W to realize established components and transparent circuit structures.

- H/W structure suitable to support signal conditioning for variety of sensors with self-x feature.

- Dynamically reconfigurable H/W with reduced switching resources and with better frequency behavior to meet industrial standards for low and medium frequency range applications.

- H/W with heterogeneous array of active and passive devices exhibiting fault tolerance and flexibility traded in for significant die area.

- Matched H/W structure with improved immunity to substrate induced noise and to compensate deviations.

- Rapid prototyping capabilities and focus on low power design.

# 1.4 Organization of the Thesis

Chapter 2 gives the state of the art of reconfigurable / evolvable analog circuits. Chapter 3 collection of amplifier application circuits were carried out to determine the essential number of components required along with their sizing information to formulate a generic sensor system Chapter 4 describes the architecture, design, and achieved implementation level of the research work. Chapter 5 provides the experimental set up and obtained results. Chapter 6 focuses on an interesting teaching perspective of the work. Chapter 7 concludes stating future works and field of improvements and last but not least in the Appendix section foot prints of the implemented H/W's with IO cell are defined and finally a brief application of this H/W in optimization loop is provided.

# 2. *State – of – the– Art* of Programmable / Reconfigurable CMOS Analog Electronics

#### 2.1 Introduction

Recent trends in the field of analog hardware design have witnessed a tremendous increase in the use of programmable devices such as Field Programmable Analog Arrays (FPAA). Programmable devices reduces the time and cost of hardware prototyping. A field-programmable analog array is an integrated circuit, which can be configured to implement various analog functions using a set of configurable analog blocks (CAB) and a programmable interconnection network, and is programmed using on-chip memories (sequential access / random access depending upon the application and cost). Programming of an FPAA is done both in terms of the topology of the circuit and in terms of its circuit parameters. At the simplest level, fixed-function IC chips with a programmable parameter can be used to accommodate minor changes in the analog specification. Many circuits have performance parameters (e.g., the gain or bandwidth of an amplifier or the corner frequency of a low-pass filter) that depend on the bias currents [37] [46] [54]. Programming a reference current from which other circuit currents are derived lets one to control the circuit parameter. One can use various methods to program the reference current. It can be as simple as using an external resistor [46] [52]. For those applications that require circuit parameters and functionality to be redefined, need of more complex implementation methods to implement programmability and configurability. For example, suppose you supply signal conditioning circuitry to two different users. If user A is using a sensor from company X and user B insists on using a sensor from company Y, the signal characteristics will probably be different, and the analog circuitry will require modifications. In this case, instead of having two different boards for signal conditioning, one programmable analog IC would be very much appreciable.

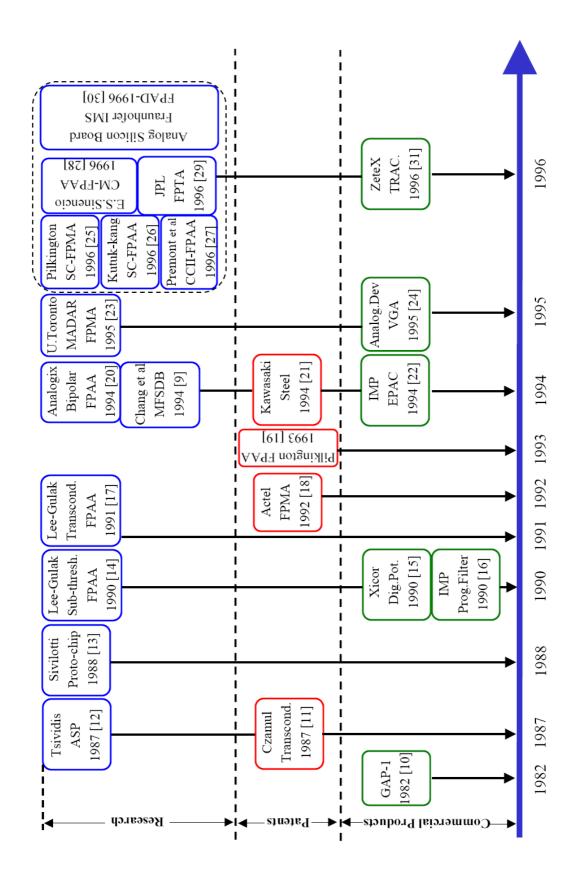

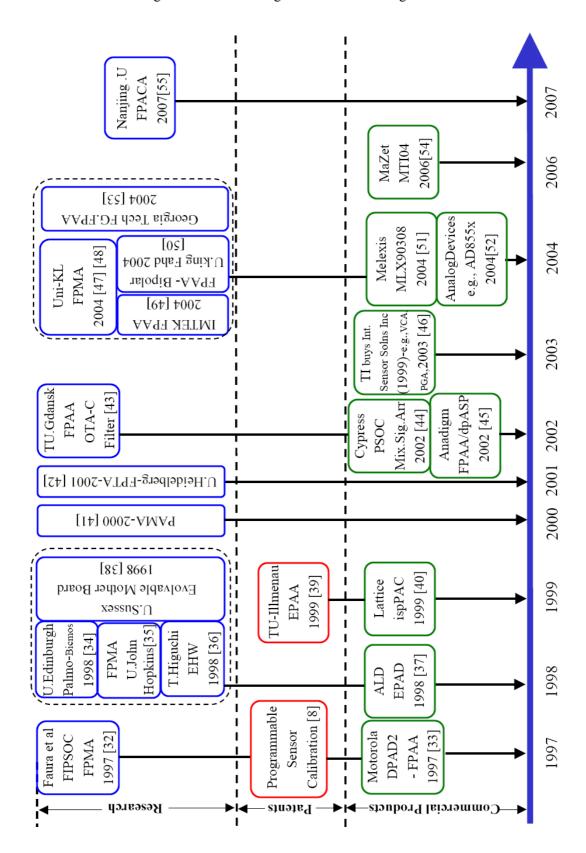

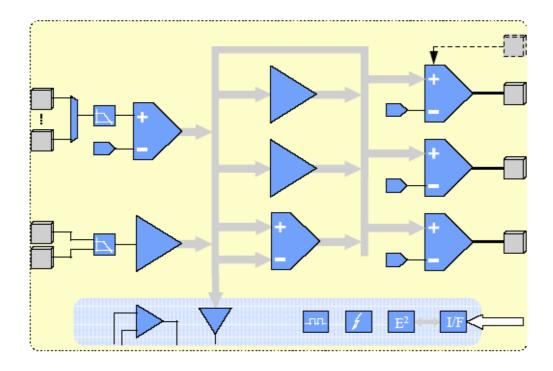

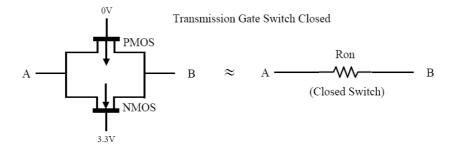

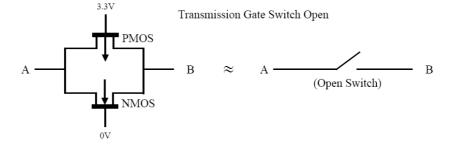

One very simple way of creating programmable analog ICs is to build circuits from a collection of building blocks (cells from primary library of the technology provider), and routing them using programmable switches (NMOS/PMOS/Transmission gate Switches). The building blocks are themselves made up of collection of components for e.g., transistor, resistors, capacitors, and operational amplifiers. Based on the level of complexity, either on transistor level or on block level, programmable analog ICs can be classified as fine grained or course grained structures. Comprehensive collection of Reconfigurable / Evolvable analog and mixed-signal hardware (Evolutionary techniques applied on to reconfigurable HW) are depicted in Figure 2-1 and Figure 2-2.

Figure 2-1: Mile stone in the field of reconfigurable / evolvable analog electronics I

Figure 2-2: Mile stone in the field of reconfigurable / evolvable analog electronics II

# 2.2 Overview of Commercial Programmable Analog / Mixed-Signal IC's

IC suppliers have devised various ways of creating configurable programmable analog ICs. The simplest uses traditional analog components in the input and feedback networks (resistors and capacitors). This option creates a continuous-time circuit, so-called because input signals are continuously used and output signals are continuously valid. The drawback is that, the parameters of filters implemented in this way usually depend on RC time constants, and resistors and capacitors implemented in ICs have large tolerances due to manufacturing deviations, making it difficult to achieve consistent filter performance. One way to solve the problem is to modify the circuit so that time constants depend rather on an amplifier's transconductance. Lattice Semiconductor combines this technique with capacitor trimming (switched capacitor technique) to achieve filters with less than  $\pm 5\%$  variation on their ispPAC chips [40]. More information about this chip and other available programmable chips will be discussed in subsequent titles.

#### 2.2.1 IMP- Electrically Programmable Analog Devices (EPAC)

In 1995 IMP Inc. released a commercial FPAA-like product, the EPAC 50E10, and then released the EPAC 50E30 [Kle96]. Both are discrete-time designs based on switched-capacitor technology. Figure 2-3 shows a diagram of the 50E10 Electrically Programmable Analog Circuit (EPAC). It includes input analog multiplexer, programmable amplifiers, routing bus, and output modules. The input and output blocks can add programmable offsets. The input multiplexer can route either 16 single-ended or 8 fully-differential signals. The EPAC 50E10 is programmed using a 200-bit configuration bit string. Bandwidths are limited to 125 kHz (clock frequency of 1MHz) due to the use of switched-capacitor technology. The 50E10 is targeted to signal conditioning applications; the 50E30 is targeted to monitoring applications, with an alarm signal triggered if an input signal goes outside a programmable voltage range. All three designs can be reconfigured on the fly, by exchanging configuration bits between the SRAM configuration shift register and an EEPROM on-chip memory. This exchange takes 250 ms for the 50E10. The first implementation of EPAC technology is based on a 1.2 micron analog EECMOS process. The EPAC family of FPAAs is no longer commercially available. The basic time discrete macro building modules for Switch Capacitor approach were called as expert cell functional modules. The first implementation of first EPAC technology was based on 1.2 µm process with supply voltage of 5V with ± 10% of variations.

#### 2.2.2 Motorola MPAA020

In 1997 Motorola Inc. released a CMOS switched-capacitor FPAA design called the MPAA020. The FPAA architecture, organized as an array of CABs, is depicted below. The FPAA includes

Figure 2-3: Block diagram of a user programmable analog signal conditioning device from [22]

four rows of five CABs and is programmed using a 619-bit string. Each CAB can realize a first-order filtering functions. A CAB can be connected to its immediate neighbours through the "local inputs" and "local outputs." It can also be connected to its other neighbours via a global bus accessed through the "global bus" input and "global outputs." As with the EPAC family, the clock speed is 1MHz, limiting bandwidths to 200 KHz. A PC-based CAD tool accompanies the MPAA020. Programming of the MPAA020 is done via the serial port of a PC. Figure 2-4 shows the architecture of MPAA and this product is no longer commercially available.

#### 2.2.3 Zetex Totally Reconfigurable Analog Circuit

Zetex has introduced the Totally Reconfigurable Analog Circuit (TRAC020), a continuous-time, log-domain bipolar design operating up to 4MHz. The TRAC includes 20 CABs, organized in two rows of 10 CABs, each capable of implementing one of the eight following functions: log, anti-log, non-inverting pass, addition, negating pass, op-amp, half-wave rectification, and off. The interconnection network is hardwired. The leftmost pins act as inputs whereas the rightmost pins act as outputs [31]. The intermediate pins can be configured either as inputs or outputs, depending on the configuration of the CAB to the immediate left of the pin. Topological programming is implemented by turning CABs off, and by external wiring of the pins. By turning a CAB off, its inputs and output are electrically disconnected, allowing the designer to use the output as an input to the subsequent CAB. Amplifier gain is determined by using off-chip

resistors. Configuration of the CABs is accomplished using a 60-bit string. Once more, a CAD tool is used to configure the TRAC; the CAD tool includes a simulator to simulate a circuit before being downloaded onto the FPAA IC. FAS advocate a computational approach to analog circuit design, where circuits are designed with their functionality in mind (a top-down approach), rather than the underlying circuitry (a bottom-up approach).

Figure 2-4: Architecture of MPAA

#### 2.2.4 Anadigm AN231E04 Dynamical Reconfigurable dpASP

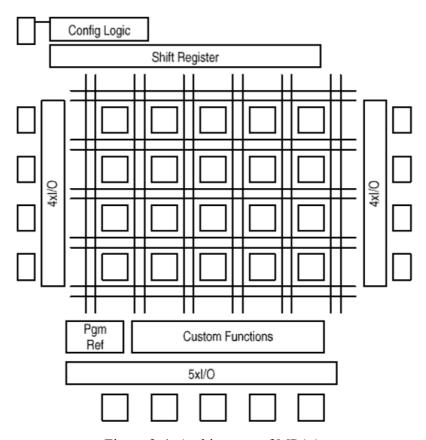

The AN231E04 device is an "Analog Signal Processor" ideally suited to signal conditioning, filtering, gain, rectification, summing, subtracting, multiplying, etc. The AN231E04 device consists of a 2x2 matrix of fully Configurable Analog Blocks (CABs), surrounded by programmable interconnect resources and analog input/output cells with active elements as shown in Figure 2-5. On chip clock generator block controls multiple non-overlapping clock domains generated from an external stable clock source. Internal band-gap reference generator is used to create temperature compensated reference voltage levels.

Figure 2-5: Architectural overview of the device AN231E04 (from [45])

The inclusion of an 8x256 bit look-up table enables waveform synthesis and several non-linear functions. Configuration data is stored in an on-chip SRAM configuration memory. The AN231E04 device features seven configurable input/output structures each can be used as input or output, 4 of the 7 have integrated differential amplifiers. There is also a single chopper stabilized amplifier that can be used by 3 of the 7 output cells. Circuit design is enabled using Anadigmdesigner2 software, a high level block diagram based circuitry entry tool. Circuit functions are represented as CAMs (Configurable Analog Modules) these are configurable block which map onto portions of CABs. The software and a development board facilitate instant prototyping of any circuit captured in the tool.

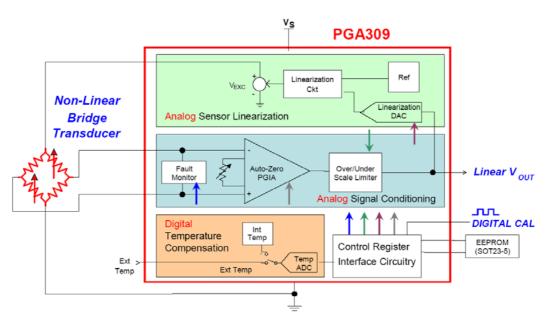

# 2.2.5 Texas Instruments – PGA- Digital Trim for Non-Linearity's

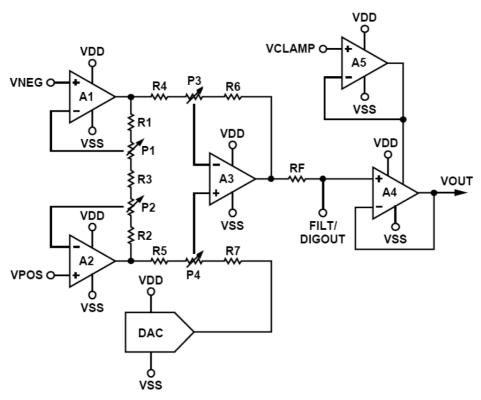

The PGA309 is a programmable analog signal conditioner designed for bridge sensors. The analog signal path amplifies the sensor signal and provides digital calibration. The calibration is done via a digital serial interface. The calibration parameters are stored in external non-volatile memory (typically SOT23-5) to eliminate manual trimming and achieve long-term stability. The all-analog signal path contains a 2x2 input multiplexer (mux), auto-zero programmable-gain instrumentation amplifier, linearization circuit, voltage reference, internal oscillator, control logic, and an output amplifier. Programmable level shifting compensates for sensor DC offsets. The core of the PGA309 (externally programmable gain amplifier) is shown in Figure 2-6. The gain of amplifier is defined by an external resistor. The overall gain of the Front-End PGA + Output Amplifier can be adjusted from 2.7V/V to 1152V/V.

Figure 2-6: Modern digital trimming for nonlinearities using PGA309 – programmable sensor signal conditioner (from [46])

#### 2.2.6 Analog Devices – Digi Trim AD855x series

The AD8555 is a zero-drift, sensor signal amplifier with digitally programmable gain and output offset. Designed to easily and accurately convert variable pressure sensor and strain bridge outputs to a well-defined output voltage range, the AD8555 also accurately amplifies many other differential or single-ended sensor outputs. Functional block diagram of sensor signal block diagram is shown in Figure 2-7. The AD8555 uses the ADI patented low noise auto-zero and DigiTrim® technologies to create an incredibly accurate and flexible signal processing solution in a very compact footprint. Gain is digitally programmable in a wide range from 70 to 1,280

through a serial data interface. Gain adjustment can be fully simulated in-circuit and then permanently programmed with proven and reliable poly-fuse technology. Output offset voltage is also digitally programmable and is ratio metric to the supply voltage. In addition to extremely low input offset voltage and input offset voltage drift and very high dc and ac CMRR, the AD8555 also includes a pull-up current source at the input pins and a pull-down current source at the VCLAMP pin. This allows open wire and shorted wire fault detection. A low-pass filter function is implemented via a single low cost external capacitor. Output clamping set via an external reference voltage allows the AD8555 to drive lower voltage ADCs safely and accurately.

Figure 2-7: Functional block diagram of digitally programmable sensor signal amplifier (from [52])

When used in conjunction with an ADC referenced to the same supply, the system accuracy becomes immune to normal supply voltage variations. Output offset voltage can be adjusted with a resolution of better than 0.4% of the difference between VDD and VSS. A lockout trim after gain and offset adjustment further ensures field reliability. The AD8555AR is fully specified over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Operating from single-supply voltages of 2.7 V to 5.5 V, the AD8555 is offered in the narrow 8-lead SOIC package and the 4 mm × 4 mm 16-lead LFCSP. Other programmable devices from the manufacturer are programmable Gain instrumentation amplifier (G=1, 10, 100, 1000) AD8253

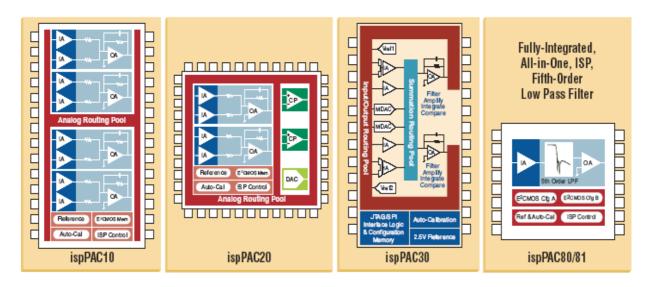

#### 2.2.7 Lattice ispPAC

The ispPAC®30 is a member of the Lattice family of In-System Programmable (ISP<sup>TM</sup>) analog integrated circuits. It is digitally configured via SRAM and utilizes E2CMOS memory for non-volatile storage of its configuration. The flexibility of ISP enables programming, verification and unlimited reconfiguration, directly on the printed circuit board. The ispPAC30 is a complete front end solution for data acquisition applications using 10 to 12-bit ADC's.

Figure 2-8: Functional block diagram of ispPAC family (from [40])

It provides multiple single-ended or differential signal inputs, multiplexing, precision gain, offset adjustment, filtering, and comparison functionality. It also has complete rout ability of inputs or outputs to any input cell and then from any input cell to either summing node of the two output amplifiers. Designers configure the ispPAC30 and verify its performance using PAC-Designer®, an easy to use, Microsoft Windows® compatible development tool. Device programming is supported using PC parallel port I/O operations. The device consists of 4 Instrumentation Amplifier, Two 8-bit multiplying ADC, and 2 configurable rail to rail output amplifiers (single-ended output, 0V-5V output swing, and 5V supply voltage) operating in as amplifier, comparator, filter or integrator modes. The block diagram of the ispPAC family is shown in Figure 2-8.

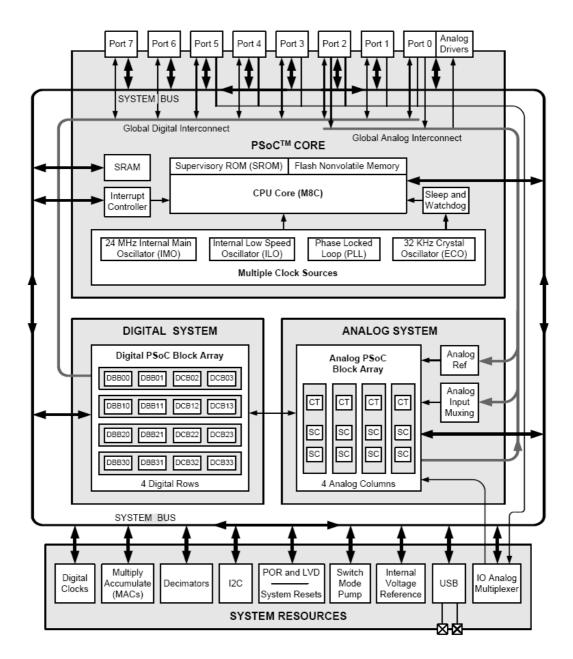

#### 2.2.8 Cypress PSoC

The PSoC<sup>TM</sup> family consists of many mixed-signal arrays with on-chip controller devices. A PSoC device includes configurable blocks of analog circuits and digital logic, as well as programmable interconnect.

Figure 2-9: Top level block diagram of PSOC (from [44])

This architecture allows the user to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable input/ output (IO) are included in a range of pin outs. The functional block diagram of PSoC is shown in Figure 2-9.

#### 2.2.9 Analog Linear Devices – EPAD

ALD EPAD Matched Pair MOSFET: Array: EPAD is a MOSFET semiconductor with electrically settable threshold voltage. As a versatile circuit design element, the ALD EPAD is an analog transistor with built-in permanent memory. Used as an in-circuit element for trimming a combination of analog voltage and/or current characteristics, an EPAD can be remotely and automatically programmed using a PC-based EPAD Programmer via software control. Once programmed, the set DC voltage and current levels are stored indefinitely, even after power-down. The EPAD MOSFET array product family is available in 3 separate categories, the first is the ALD110800/ALD110900 zero threshold mode EPAD MOSFET's. Second category is the enhancement mode EPAD MOSFET's namely ALD1108xx/ALD1109xx and the third category is the ALD1148xx/1149xx depletion mode EPAD MOSFET's.

ALD EPAD Op-Amps: are pre-trimmed electrically at the factory for very low offset voltage (Vos) and bias/offset currents (Ibias/Ios). They are ready to be used without any extra handling. These CMOS Op-Amps are economical, very-high-precision and easy-to-use. They also possess optional capability for all solid-state Vos field-trimming. EPAD Op-Amps are available in two grades, standard and E-grade. E-grade Op-Amps are specified with added electrical Vos programming ranges

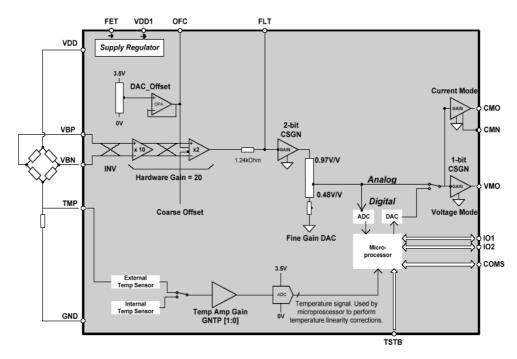

#### 2.2.10 Melexis - Programmable sensor interface MLX90308

The MLX90308 is a signal conditioning microcontroller for sensors in bridge or differential configurations. Sensors that can be used include thermistors, strain gauges, load cells, pressure sensors, accelerometers, etc. The signal conditioning includes gain adjustment, offset control, and linearity compensation. Compensation values are stored in EEPROM and are reprogrammable. The application circuits can provide an output of an absolute voltage, relative voltage, or current. A supply voltage ranging from 6V-35  $V_{DC}$  can be applied. An internal voltage regulator fix the voltage to a typical value of 4.75V.The –3dB bandwidth of this product is 3.5 KHz. The functional block diagram of MLX90308 is shown in Figure 2-10.

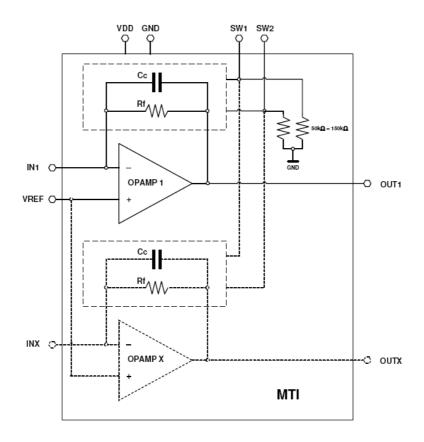

#### 2.2.11 MaZeT – Programmable Gain Transimpedance amplifier MTI04Bx-BF

The MTI-devices are a family of integrated circuits of programmable gain transimpedance amplifiers with different numbers of channels (4 standard, others custom specific). The MTI-devices are mainly used for signal conditioning of sensors with current outputs. They are especially suitable for connection of photodiodes of array and row sensors. The possibility to adjust the transimpedance in 3 steps is a special feature.

Figure 2-10: Functional block diagram of programmable sensor interface - MLX90308 (from [51])

The adjustment is made by programming two pins and is valid for all channels together. The MTI-devices are programmable gain transimpedance amplifiers with different numbers of channels (MTI04 – 4 channels). There is one transimpedance amplifier per channel between a current input INX and a voltage output OUTX. Its transimpedance is selectable in 3 stages. This adjustment can be effected by setting of digital inputs SW1 and SW2 and is valid for all channels simultaneously. The inputs SW1 and SW2 are pulled down with a resistor for a default feedback resistor of  $25k\Omega$ . The second input of all transimpedance amplifiers is used for a common supply by a reference voltage necessarily fed in through the pin VREF. The block diagram of this product is shown in Figure 2-11.

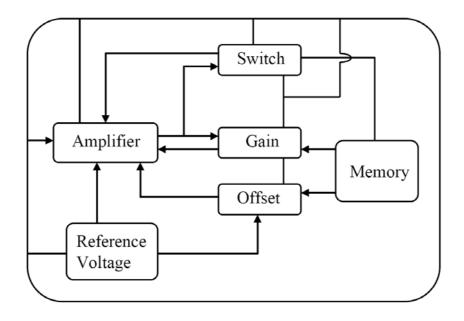

#### 2.2.12 Embedded and Programmable Sensor Calibration.

This is an approach with a US patent filed by Robert D. Juntunen in the year 1993 [8]. The block diagram of embedded programmable sensor calibration is shown in Figure 2-12. According to this patent, span and offset errors are removed using a circuit to generate corrected output signal as a function of calculated gain and offset values. Initially, sensor outputs like gain and offset are measured with no inputs. These values are then used in an equation to calculate offset and gain values. The circuits used are Op Amp, switch, gain circuit, offset circuit and a memory. The memory is a serially written memory (shift registers).

Figure 2-11: Block diagram of multi-channel programmable gain transimpedance amplifier (from [54])

Figure 2-12: Block diagram of embedded programmable sensor calibration (from [8])

# 2.3 Overview of Academic Reprogrammable Analog Hardware

# 2.3.1 FPAA - University of Toronto (Gulak)

Gulak and Lee, in their earlier contribution to FPAA based on MOSFETs working in subthreshold [14], pass transistors were used and were controlled by SRAM memory cells. They also noticed that there were die to die variations in the performance of this FPAA. The IC was designed to implement both voltage and current mode circuits and was implemented for parametrically reconfigurable neural networks applications. Later, MOS transconductor based FPAA was implemented [6]. It consists of Op Amp and programmable capacitors linked by transconductor based interconnections. The innovation in this approach is that the switches in the interconnection network are linear resistors which are implemented as four transistor MOS transconductor. This IC was implemented in 1.2 µm CMOS technology.

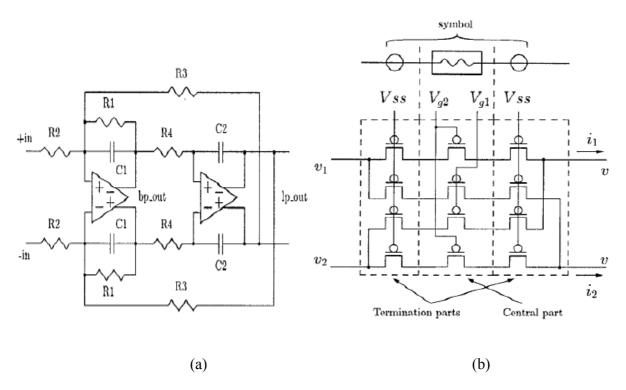

Later on, Glen Gulak and Lee of Toronto University research group has presented two other FPAAs. The first FPAA consists of fully-differential continuous-time CMOS transconductor-based CABs operating in the 100 kHz range. This FPAA was targeted toward signal processing applications in the audio range with bi quad filter as shown in Figure 2-13(a) [5]. The CABs of this FPAA contain an op-amp as well as switchable feedback capacitors, and can also be used to implement a comparator by turning off the compensation capacitor. In this design, switches in the interconnection network are implemented using the transconductor, which acts as a programmable on/off switch, polarity change switch, and variable resistor as shown in Figure 2-13(b). The transconductor is also used to realize a four quadrant multiplier. Gaudet and Gulak presented another FPAA that is based on current conveyors. This FPAA is targeted toward applications in the video frequency range (10 MHz). Each CAB of the FPAA consists of a second generation current conveyor CCII and a bank of programmable resistors and capacitors.

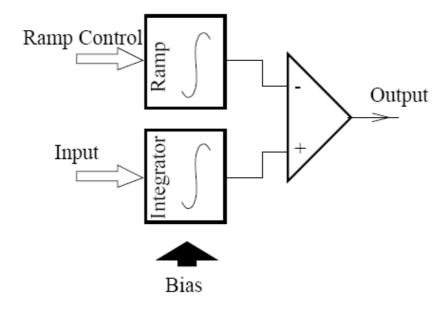

#### 2.3.2 Palmo- University of Edinburgh

The research group of the University of Edinburgh has devised a coarse grained FPAA chip called *palmo*. This chip basically works on pulse based techniques. In palmo the signals are represented neither as voltages nor as currents, but instead as digital pulses to represent discrete analog signals. The word palmo stands for pulsebeat, pulse palpitation or series of pulses. The chip consists of an array of programmable cells that performs the function of an integrator. The typical palmo cell is represented as shown in the Figure 2-14. The input pulses are integrated over time by the use of an analog integrator. This integrated value is then compared to a ramp in order to generate the pulsed output. The so compared ramp signals are global or local signals. The advantage of using such a ramp generation is that it is possible to accurately control the overall gain of the circuit. The palmo system allows the use of digital circuits to manipulate the pulses representing the analog quantities.

Figure 2-13: schematic of bi quad filter (a) and schematic of MOS transconductor (b) [5]

Figure 2-14: Representation of typical Palmo Cell

#### 2.3.3 Evolvable Motherboard – University of Sussex

Figure 2-15: Evolvable motherboard test bed for the study of intrinsic HW (from [38])

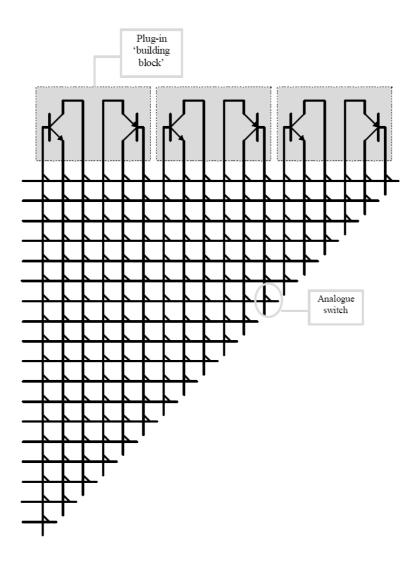

The research group at the University of Sussex had developed a tool intended for implementing evolutionary exercises. The board level tool allows large variety of components to be used as basic active elements. The components are connected to each other through an interconnection architecture, namely analog switches. The Evolvable motherboard in total has 1500 switches. The diagonal lines in the Figure 2-15 represent the switches. Different plug in daughter boards are connected is also shown in the same figure. The users can choose the type of components to be added to the plug in boards like for e.g., transistors, multiplexers, operational amplifiers etc.

### 2.3.4 PAMA Catholic University of Rio de Janeiro

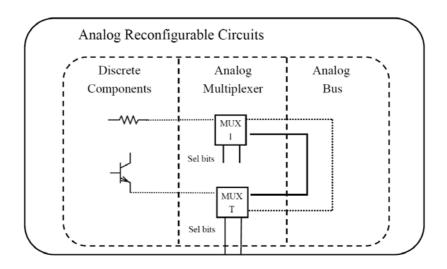

The programmable Analog Multiplexer Array (PAMA) is a fine grained, board level FPAA. This work has been inspired from the previous work of JPL group. The reconfigurable circuits are divided into three layers as shown in Figure 2-16. The three different layers constituting PAMA are discrete components, analog multiplexers and analog bus. The idea of a programmable multiplexer array was first in Zebulum et al [91] [92]. Each line of the analog bus corresponds to one interconnection point of the circuit; some of them can be associated to I/O signals or power signals, while others are associated to interconnection of the circuits. To put in simple sentences, each component terminals require one analog multiplexer. In PAMA, evolutionary techniques are able to exploit any interconnection patterns to realize different circuit topologies.

Figure 2-16: Analog reconfigurable circuit's layers (from [56])

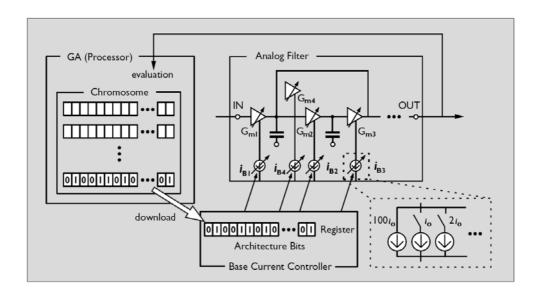

#### 2.3.5 Higuchi EHW

The proposed EHW chip was meant for filters operating in intermediate frequencies. The basic idea of the EHW chip is shown in the figure below. The chip consists of 39 transconductance amplifier whose value could be determined genetically. The values, which actually control the base current of the CMOS, are coded as configuration bits. Each *Gm* element value may differ from the target value up to a maximum of 20%. Initial simulations have shown that 95% of the chips can be corrected to satisfy the IF filter's specifications. The basic idea of the analog EHW is shown in Figure 2-17.

Figure 2-17: Basic idea of the analog EHW chip for intermediate frequency filters (from [36])

#### **2.3.6 FPAA – IMTEK**

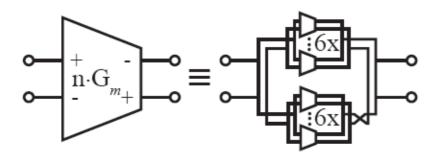

The FPAA structure consists of a two-dimensional array of CABs, which include digitally configurable transconductors (differential transconductance amplifiers). The Figure 2-18 shown below represents 1 programmable Gm cell. Figure 2-19 shows 1 CAB. The arrangement in a hexagonal layout allows reconfigurable routing of analog signals throughout the chip. Series and parallel connection as well as feedback of any order is provided by the structure. Every CAB has six branches connecting to the respective neighbour CABs and one for self-feedback. The massive parallel connections of both parasitic input capacitances as well as parasitic output capacitances at the input nodes of each CAB sum up to capacitances in an order of magnitude such that they are suitable as integrating capacitances for the filter up to unity-gain bandwidths of 200 MHz Different filter types with different orders can be synthesized on this FPAA, like for example second order low-pass filter, integrator or fourth order bi-quad Butterworth band-pass filter. A test-chip has been designed and manufactured in a 130nm CMOS technology.

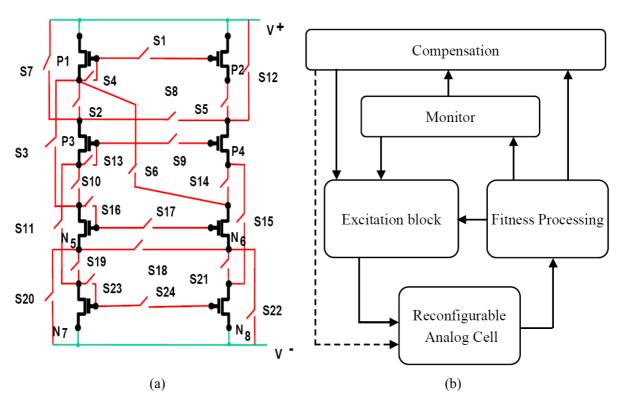

#### 2.3.7 FPTA / SRAA- JPL

Field programmable Transistor Array is a fine grained FPAA developed at the Jet Propulsion Laboratories, intended to conduct experiments in evolvable hardware. FPTA is a reconfigurable hardware at the transistor level. FPTA is an array of transistors interconnected by programmable switches as shown in Figure 2-20(a). The status of the switches ON or OFF determines the circuit topology. FPTA remains a good platform for synthesis of analog, digital and mixed signal

circuits. Figure 2-20 illustrates a module of the programmable transistor array consisting of 8 transistors and 24 programmable switches. This module consists of PMOS and NMOS transistors, and switch based connections.

Figure 2-18: Block diagram of a programmable Gm-C cell (from [57])

Figure 2-19: Block diagram of a configurable analog block (from [57])

The number of switches used in realising different circuit topologies may differ from each other. The two FPTA chip versions were implemented in 0.5µm CMOS technology and one in 0.18µm technology. The group manufactured 3 versions of FPTA chips of varying complexity [63]. The most recent FPAA version is called Self Reconfigurable Analog Array (SRAA). This version of the chip has variety of analog cells like Op Amp, comparators, pulse width modulators etc., together with the possibility of self correction at extreme temperatures ranging from –180°C to +125°C [67]. In SRAA, digital ASIC implements the compensation algorithm and the control of analog ASIC during monitoring and compensation mode. A hierarchical compensation approach was adapted. Three different levels of compensation were carried out. First, involves through mapping corrections that were predetermined by a model based or through measurement. Secondly, finding solution through gradient descent search and third approach is by global search using evolutionary approach. The block diagram of the compensation and monitor control are shown in Figure 2-20(b)

Figure 2-20: Module of the programmable transistor array (from [56] & [67])

# 2.3.8 FPTA – University of Heidelberg

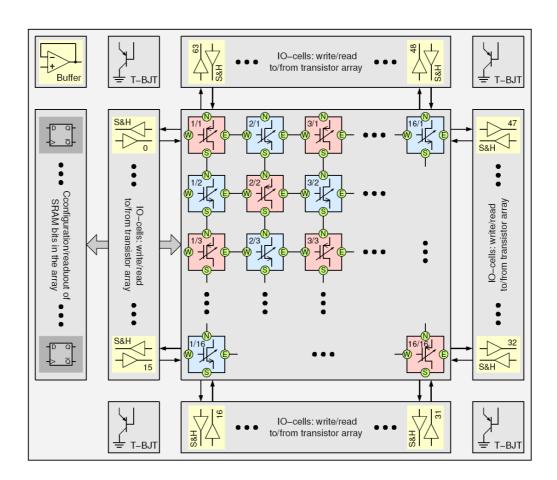

The vision group at the University of Heidelberg had developed a fine grained FPAA approach called FPTA, a system suitable for hardware evolution of analog electronics circuit at transistor

level. The CMOS VLSI chip manufactured in  $0.6\mu m$  technology consists of 16\*16 programmable transistor cells as shown in Figure 2-21. These cells contain only active devices, either a programmable PMOS or NMOS transistors, whose aspect ratio can be changed. The channel width and length of the programmable transistor itself can be adjusted to  $W=1...15\mu m$  and  $L=0.6, 1, 2, 4, 8\mu m$ , respectively [58]. The terminals of these transistors can be connected to four neighbouring cells with the help of the switches. By appropriate programming of these switches, different circuit topologies can be implemented. The configuration of the transistor array is stored in SRAM cells embedded in the transistor cells themselves. The chip was used for automatic synthesis of analog circuits using evolutionary approach.

Figure 2-21: Simplified architecture of FPTA - Heidelberg chip (from [58])

In spite of good results, the approaches mentioned in section 2.3.8 and in section 2.3.7 uses sea of transistors (tremendous area requirement) for implementing circuits using large amount of switching devices affecting the frequency behaviour of the whole system. These pitfalls remain as the incentives of this thesis work.

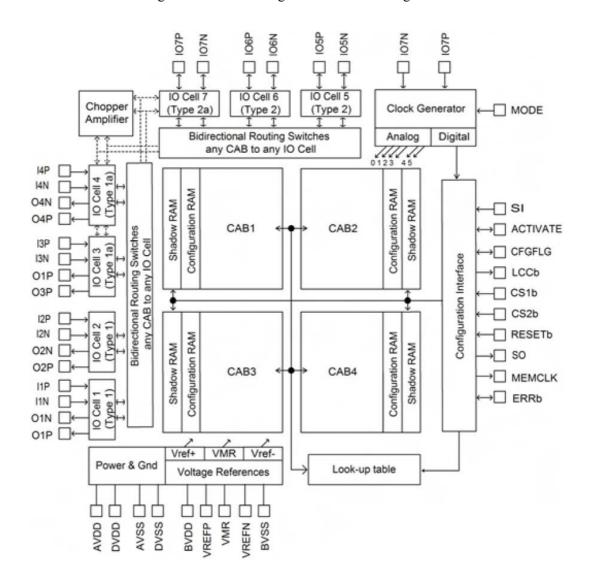

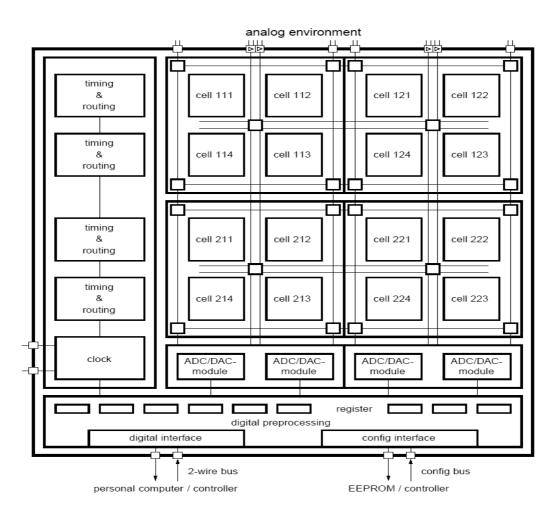

#### 2.3.9 EPAA – TU Ilmenau

Electrically Programmable Analog Array (EPAA) is a fully configurable analog array dedicated to implementation of analog and mixed-signal applications using both, continuous current (CC) and switched-capacitor (SC) techniques. Overall architecture can be seen in Figure 2-22. Partitioning to 4 clusters (each containing 4 cells) can be seen in the right-upper part. Desired EPAA configuration is autonomous downloaded via serial system interface from EEPROM, immediately after power-on sequence. EPAA architecture consists of 4 clusters and each cluster has 4 cells as shown in the figure below. Initial version of EPAA was implemented in Alcatel Mietec 0.5um CMOS technology, comprising 2x2 programmable clusters. Typical supply voltage of 3.3V was used. The EPAA was used in application circuits like magneto resistive bridges. EPAA along combined with dedicated software to form the evaluation platform called Rapid Development Kit (RDK).

Figure 2-22: Architecture of EPAA (from [39])

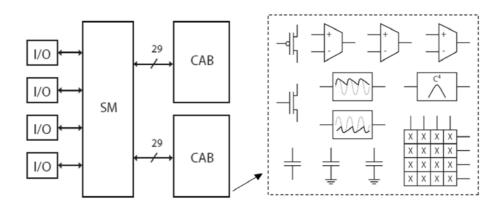

### 2.3.10 FG FPAA - Georgia Tech

As seen in Figure 2-23, the RASP 1.x FPAA is composed of two vertically aligned general purpose configurable analog blocks (CABs) connected via a single crossbar switching network. This switch matrix (SM) allows any CAB component in either CAB to be connected to any other CAB component with just two switches. The CAB components were chosen to provide a balanced mixture of granularity in order to achieve an effective trade-off between performance and flexibility. The transistors and capacitors provide fine-grain flexibility, which allows almost any circuit to be synthesized with a sufficiently large CAB array. OTAs and C4 band-pass elements were included as medium-grain components, since these elements can be used in a significant number of circuit topologies. FPAA architecture has two modes of operation, run and program. In program mode, indicated by the "prog" signal going high, the floating gate transistors used for switches and biases are configured into one large matrix for global addressing.

Figure 2-23: RASP. 1. x FPAA architecture and CAB components (from [53])

In this approach a pull-up transistors drive the sources of floating gate switch transistors, and drain lines are connected to the column programming logic. Bias transistors are disconnected from the circuits they control and are connected to the same programming lines used for the switches. The row selection circuitry is used to switch the external coupling voltage, VC, to the selected row. All unselected rows have their coupling capacitors pulled up to VDD. A decoder is used to generate the row select signals, rsel<x>. In a similar fashion, the column selection circuitry connects the selected column's drain line to the external drain signal, VD. All unselected drain lines are tied to VDD. Another decoder generates the column select signals, csel<x>. Run mode is defined when the "prog" signal in Figure is low. In this configuration, the source and drain terminals of the floating gate switches are left floating as the rows and columns of the routing fabric, and the bias floating gate transistors are switched into their corresponding CAB components. In this work several filter topologies were investigated.

# 2.3.11 FPAA Based OTA-C Filter - Technical University of Gdansk

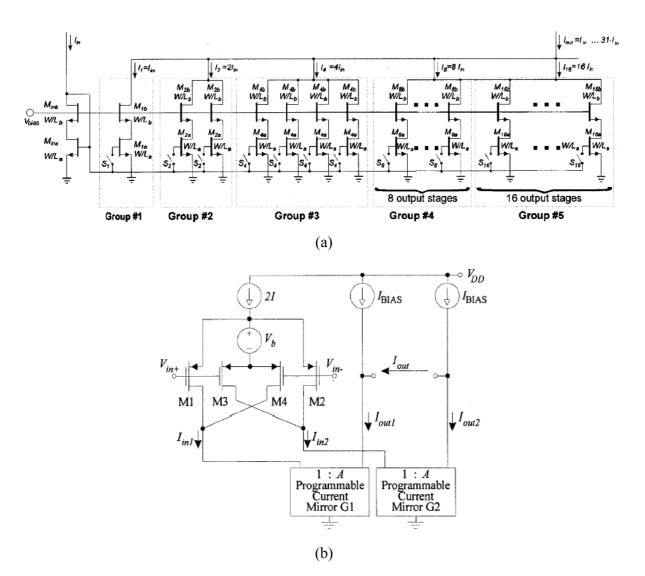

Figure 2-24: Programmable current mirror (a) programmable OTA (b) (from [43])

Bogdan Pankiewicz et al had investigated and analysed a programmable OTA. This programmable OTA along with programmable capacitors were used to realize CAM's and then to filter circuits using these CAM's. CMOS switches assist in programming the structure. Programmable OTA is obtained by using programmable current mirrors. The current mirror has 5 output stages (1, 2, 4, 8, and 16). Appropriate switch selection gives the essential current defining the currents. The programmable current mirror was focused to adjust only gain [43]. Figure 2-24(a) and Figure 2-24(b) shows CMOS programmable OTA and programmable current mirror circuits respectively.

### 2.3.12 FPMA - John Hopkins University

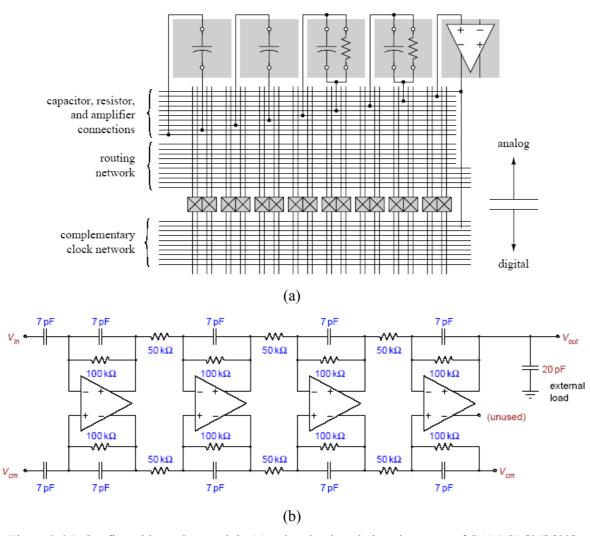

Figure 2-25: Configurable analog module (a) pulse shaping chain using array of CAM (b) [35] [83]

The architecture of an FPMA\* (Field Programmable Mixed Signal Array) is largely determined by the type of programmable interconnection technology. An anti-fuse technology provides a low resistance programmable connection and nonvolatile configuration storage in a structure in the size of a via. An FPMA architecture based on anti-fuses can implement continuous time analog circuits, as well as discrete time circuits. The programmable analog modules can be much more area efficient, because anti-fuses occupy much less area than a MOS switch. In this approach, AMOD (analog modules) architecture is based on a non-programmable fully differential Op Amp with associated programmable MOS capacitor and poly resistor arrays, as well as some MOS

<sup>\*</sup> Same abbrevation like the one used in this thesis (chapter 4) but has different meaning.

analog switches for implementing switched circuits as shown in Figure 2-25(a). The CAM is used to build pulse shaping chain as shown in Figure 2-25(b) [35] [83].

#### 2.4 Evolvable Hardware

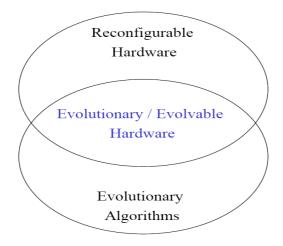

Evolvable hardware is basically reconfigurable circuits that can inherit the property of living organisms through the application of some evolutionary techniques like Genetic Algorithm (GA). Conceptually, all reconfigurable hardware devices irrespective of granularity (fine grained, medium grained or course grained) can be subjected to learning or evolutionary optimization procedures. The hardware structures can be for digital or analog domain. Some reprogrammable hardware used in today's evolutionary techniques is as listed below.

- 1. Field Programmable Gate Arrays (FPGA) for digital domain [65].

- 2. FPAA for analog domain [57].

- 3. FPTA for both analog and digital structures at transistor level [63] [64].

- 4. Evolvable Micro Electro-Mechanical System (MEMS) [66].

- 5. Evolvable Analog Neural Network [68]

Recent trends in analog circuit synthesis uses evolutionary approaches for device sizing, topology determination, etc. [72], Evolutionary approaches are stochastic search procedures employing bio–inspiration. These approaches are widely used in engineering applications in research as well as in industries [69] [70] [71]. Working of Evolvable Hardware (EHW) is based on combination of evolutionary approaches and reconfigurable devices as shown in Figure 2-26, thereby inheriting the *self-x* properties from evolutionary approaches to the hardware [73]. The self–x characteristics refer to self-organisation, self-adaptation, self-healing, self-diagnosis, etc. These desirable properties make it more attractive to modern intelligent and hybrid sensor systems.

Figure 2-26: Representation of evolvable hardware

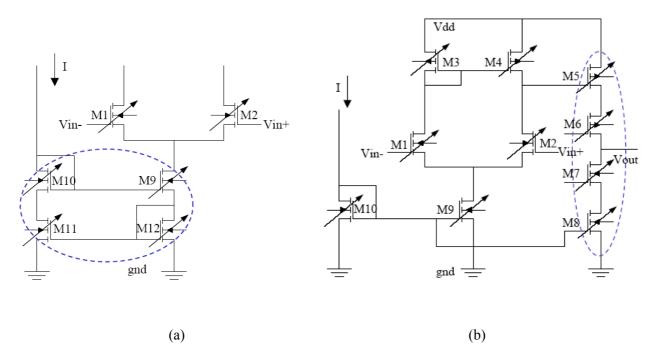

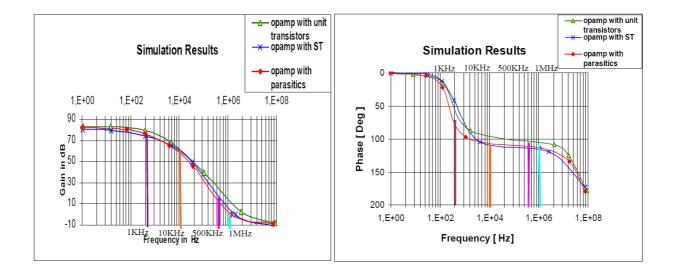

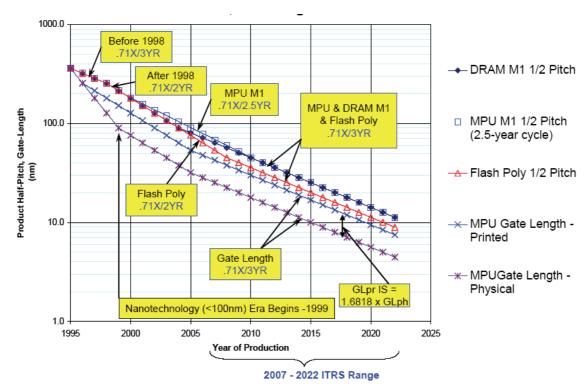

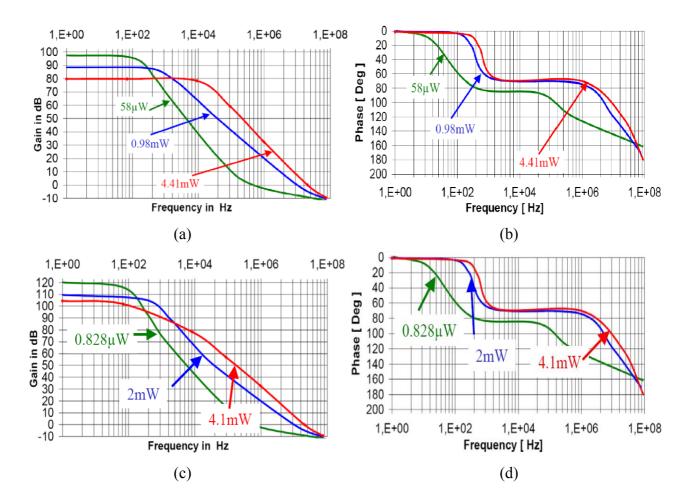

Table 2-1: State of the art of programmable analog electronics

| S. Nr | Contribution                       | Special/Product<br>Name                        | Programmability         | Granularity &<br>Config Download | Application<br>Circuit          | switches                        | Bandwidth               | Technique                            | Technology       |

|-------|------------------------------------|------------------------------------------------|-------------------------|----------------------------------|---------------------------------|---------------------------------|-------------------------|--------------------------------------|------------------|

| 1     | Precision Monolithics<br>Inc. [10] | GAP-01                                         | Gm_ Amplifier           | Coarse                           |                                 | Current mode switches [10]      | 15 KHz                  |                                      |                  |

| 2     | Tsividis et al                     | Analog Signal<br>Processor<br>(ASP)            |                         |                                  | Bi-quad filter                  | Transmission<br>Gate            | sampling rate of 16 KHz | Time continuous [77]                 |                  |

| 3     | Czamul et al                       | MRN(MOS<br>resistive<br>network)               | 4 matched mos resistor  |                                  | integrator                      |                                 |                         | Time continuous[11]                  | MOS              |

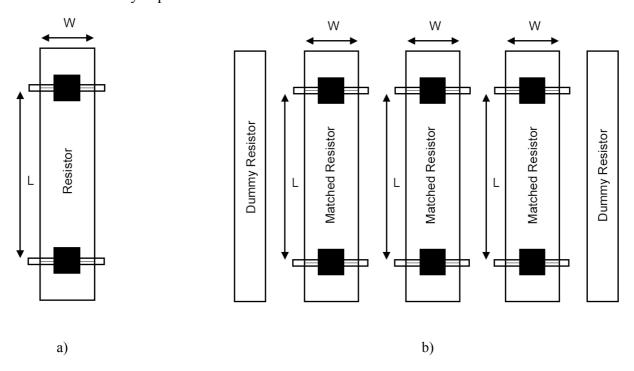

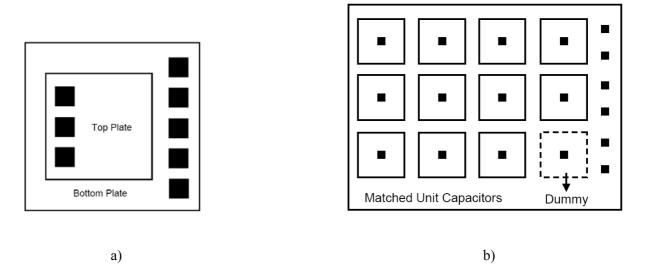

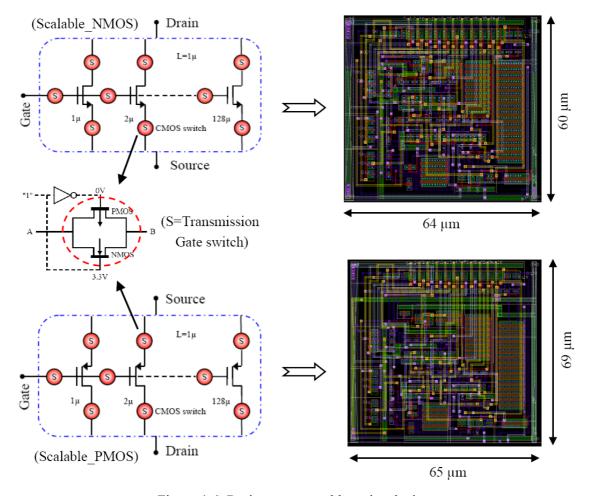

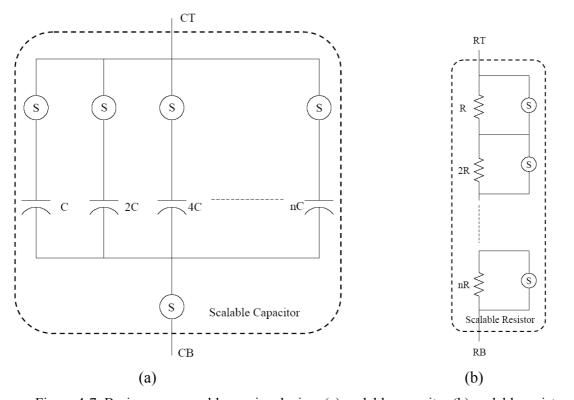

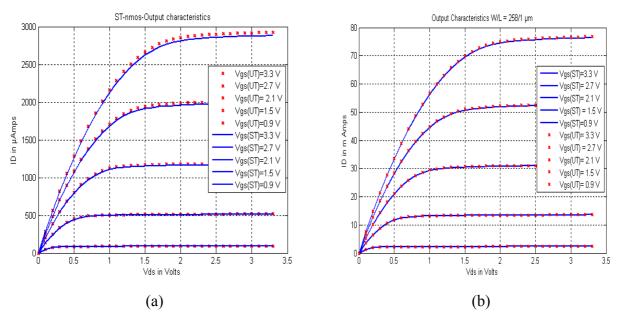

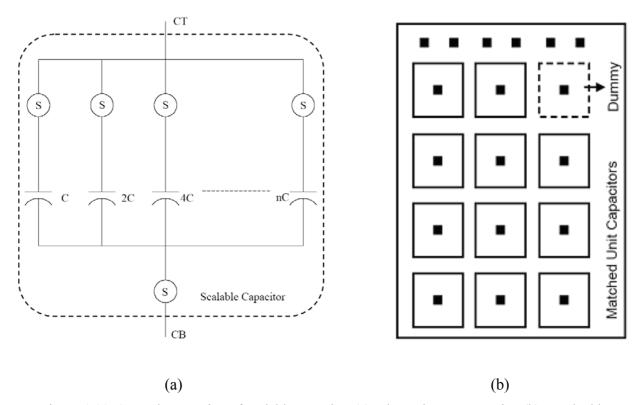

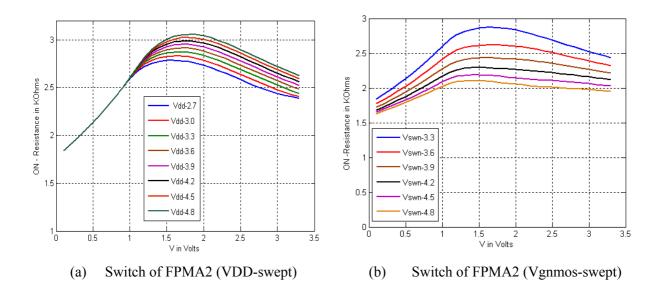

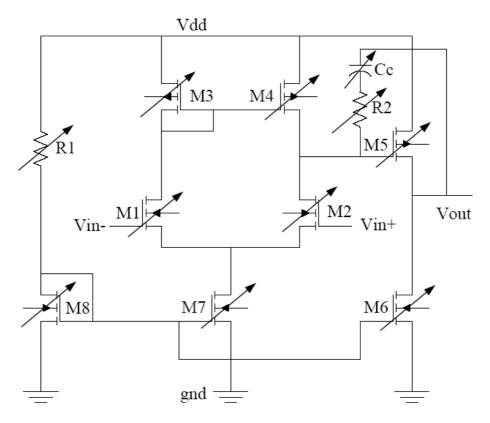

| 4     | Sivilotti et al                    | Proto-Chip                                     |                         | SRAM                             | Analog Neural<br>Network        | CMOS<br>Transmission<br>Gates   |                         | sub-threshold                        | CMOS             |