# Structural Decomposition of STGs – an Approach for Modular Asynchronous Circuit Design

## DISSERTATION

BY

## Benedictus Benyamin Kangsah

1. Tutor : Prof. Dr.-Ing. Jochen Beister

2. Tutor : Prof. Dr. Walter Vogler

Chairman of examination board : Prof. Dr.-Ing. Wolfgang Kunz

# Strukturelle Dekomposition von STGs – ein modularer Ansatz zum Entwurf ungetakteter Schaltwerke

#### vom

Fachbereich Elektrotechnik und Informationstechnik der Technischen Universität Kaiserslautern zur Verleihung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation

von

#### Benedictus Benyamin Kangsah M.Sc.

geb. Jakarta (Indonesien)

#### D 386

1. Betreuer: Prof. Dr.-Ing. Jochen Beister

2. Betreuer: Prof. Dr. Walter Vogler

Vorsitzender der Prüfungskommission: Prof. Dr.-Ing. Wolfgang Kunz

Dekan des Fachbereichs: Prof. Dr.-Ing. Hans D. Schotten

Tag der mündlichen Prüfung: 07. November 2014

# Kurze Zusammenfassung

Mit immer komplexeren asynchronen (ungetakteten) Schaltwerken – als Teilen heutiger Systems-On-a-Chip – hat auch die Größe und Komplexität ihrer Verhaltensspezifikationen mit Signalflankengraphen ("Signal Transition Graphs", STGs) zugenommen. Dieses erschwert und macht es manchmal unmöglich, die Schaltung mit dem von Signalflankengraph spezifizierten Verhalten mit einem Werkzeug wie petrify [CKK+96] oder CASCADE [BEW00] zu synthetisieren.

In der vorliegenden Arbeit wird daher ein Verfahren vorgeschlagen, welches zuerst den STG zerlegt, was zu einer modularen Umsetzung [KWVB03] [KVWB05] führt. Damit kann der Syntheseaufwand verringert werden, da eine Explosion des Zustandsraumes ("state explosion") vermieden werden kann und Wiederverwendbarkeit von Bibliothekselementen gegeben ist. Ein Ansatz für die Zerlegung eines Signalflankengraphen wird in [VW02] [KKT93] [Chu87a] vorgestellt. Der Zerlegungsalgorithmus von Vogler und Wollowski [VW02] basiert auf dem Algorithmus von Chu [Chu87a], ist aber allgemeiner anwendbar als die Algorithmen in [KKT93] [Chu87a], deren formale Korrektheit in [VW02] bewiesen wurde.

Nach der Einführung (Kapitel 1) werden in Kapitel 2 zunächst die Platz/Transitions-Netze (P/T-Netze) vorgestellt. Ihre zur Verhaltensbeschreibung nebenläufiger dynamischer Systeme erforderlichen Eigenschaften, vor allem Lebendigkeit und Beschränktheit, werden erörtert, ebenso die Besonderheiten der Signalflankengraphen als Unterklasse der P/T-Netze. Es folgen die Prinzipien der Zerlegung in Komponenten und deren Parallelkomposition auf STG- und Schaltungsebene.

Eine Motivation für die Zerlegung eines P/T-Netzes ergibt sich schon bei der Analyse, wenn z.B. herausgefunden werden soll, ob es lebendig ist oder nicht. Dazu müsste man alle erreichbaren Markierungen ermitteln. Bei einem großen, hoch nebenläufigen Netz könnte deren Anzahl so groß werden ("state explosion"), dass sie nicht mehr zu handhaben sind.

Aber auch wenn eine Schaltung ausgehend von ihrem Signalflankengraphen synthetisiert werden soll, kann die notwendige Bestimmung aller erreichbaren

Markierungen zur nicht mehr handhabbaren "state explosion" führen. Viele Synthesealgorithmen haben exponentielle Komplexität bei der Ableitung der erreichbaren Zustände. Man kann zwar versuchen, dem "state explosion"-Problem mit einem heuristischen Algorithmus mit polynomialer Komplexität beizukommen. Aber wenn das Problem groß ist, erhält man ein nichtoptimales Ergebnis. Daher wird die Zerlegung des P/T-Netzes zum Lösen der oben genannten Probleme verwendet, in der Hoffnung, dass Gesamtaufwand und Kosten für die Synthese der Komponenten deutlich kleiner werden als für die Behandlung des großen Netzes. Eines dieser Verfahren ist das Signalflanken-Zerlegungsverfahren von [VW02]. Es wird in Kapitel 3.2 beschrieben.

Das Zerlegungsverfahren aus [VW02] kann noch weiter verbessert werden, um damit Signalflankengraphen für reale Anwendungen synthetisierbar zu machen und bessere Zerlegungsergebnisse zu bekommen. Einige Verbesserungsvorschläge für [VW02] werden in Kapitel 4 behandelt. Diese Verbesserungen werden in [KVWB04] vorgeschlagen, einige von ihnen werden formal in [VK04] bewiesen. Mit diesen Verbesserungen können nicht nur Signalflankengraphen von realen Anwendungen zerlegt werden, sondern es können auch bessere Zerlegungsergebnisse erhalten werden. Dummy-Transitionen und strukturelle Auto-Konflikte sind dabei erlaubt. Durch die Ubersetzung von Hardware-Beschreibungssprachen in Signalflankengraphen [BL00] werden oft Dummy-Transitionen eingeführt. Strukturelle Auto-Konflikte mit Steuerplätzen treten in einer nicht deterministischen Spezifikation (z.B. die Spezifiation eines VME-Bus-Controller) oder in einer Arbiter-Spezifikation [Wol97] [YKKL94] häufig auf. Das Problem mit strukturellen Auto-Konflikten wird durch Einführung von Transition-Fusion gelöst. Probleme mit nicht-sicheren Dummy-Transitionen werden durch die Umwandlung in sichere Dummy-Transitionen gelöst. Diese und das Entfernen der schleifen-behafteten Dummy-Transitionen verringern die Häufigkeit von Backtracking in dem Algorithmus, wodurch man bessere Zerlegungsergebnisse bekommen kann. Die Effizienz des Algorithmus wird auch durch Kontraktion von global irrelevanten Signalen vor der Zerlegung und durch die Neuordnung der zu kontrahierenden Transitionen erhöht.

Die Zerlegungsverfahren aus [VW02] basieren auf Netzreduktion zum Finden einer Ausgangsblock-Komponente. Es ist sehr arbeitsintensiv, eine initiale Spezifikation zu reduzieren, bis die End-Komponente gefunden wird. Diese Reduktion ist nicht immer möglich, was dazu führt, dass weitere irrelevante Eingangsvariablen zu den relevanten Eingangsvariablen der Komponente hinzugefügt werden müssen. Dies führt zu einer unnötig großen Spezifikationen, was auch zu einer unnötig groß implementierten Schaltungen führt. Statt dieser Reduktion wird in Kapitel 5 dieser Dissertation ein neuer Ansatz präsentiert, indem das ursprüngliche Netz zuerst in strukturelle Komponenten – stark zusammenhängende Zustandsmaschinen ("strongly connected state machines", SCSMs) – zerlegt wird. Eine initiale Ausgangsblock-Komponente ist durch die Zusammensetzung der strukturellen Komponenten herauszufinden. Danach bekommt man eine endgülti-

ge Ausgangsblock-Komponente durch Netz-Reduktion. Durch die Nutzung dieses Ansatzes wird die Begrenzung der Netzreduktionsoperation überwunden, was zu kleineren End-Komponenten als in [VW02] führt. Zusätzlich ist diese Methode in der Praxis einfach anzuwenden.

Da wir meistens mit der Struktur eines Netzes beschäftigt sind, ist es sinnvoll, eine strukturelle Abstraktion des Netzes vorzunehmen. In Kapitel 6 dieser Arbeit wird ein struktureller Abstraktionsalgorithmus [Kan03] vorgestellt. Ein SCSM Subnetz ist in den meisten Fällen mit dem Strukturgraphen effizienter zu finden, als das Platz-Transition- (P/T-) Netz direkt zu traversieren. Der Strukturgraph eines gewöhnlichen P/T-Netzes kann nicht nur für die Suche nach SCSM-Subnetzen oder zur Kontraktion von Transitionen in der Mitte des Knotens verwendet werden, sondern auch für andere Algorithmen, welche die Knoten eines P/T-Netzes traversieren. Daher wird vorgeschlagen, einen Strukturgraphen als eine abstrakte graphische Datenstruktur für ein P/T-Netz bei der Umsetzung solcher Algorithmen zu verwenden. Einige Anwendungen von Strukturgraphen und deren experimentelle Ergebnisse können in [War05] und [Taw04] gefunden werden.

Schließlich diskutiert Kapitel 7 die Anwendung des STG-Dekompositionsalgorithmen im ungetakteten Schaltungsentwurf. "Speed independent"- (SI-) Schaltungen werden zuerst diskutiert. Danach werden 3D-Schaltungen, die aus einem erweiterten Burst-Mode-Spezifikationen ("extended burst mode", XBM) synthetisiert werden, diskutiert. Der [VW02]-Algorithmus ist gut für die Umsetzung in SI-Schaltungen, da eine solche Umsetzung das Netz nicht zu stark reduziert. Eine zu starke Reduktion könnte Eingangssignale entfernen, die wichtig sind, um ein kompletten Zustandskodierung zu erreichen. Es kann also dazu führen, dass keine komplette Zustandskodierung gefunden werden kann. Stattdessen ist der SCSM-Subnetz-basierte Algorithmus gut für die Umsetzung in 3D-Schaltungen, da dieser kleinere Komponenten liefert und weniger Probleme mit Schleifen-behafteten Transitionen hat, die oft in XBM-Spezifikationen aufgrund von Pegel-Transitionen vorhanden sind.

Ein Algorithmus zum Übersetzen einer Signalflankengraph-Spezifikation in eine XBM-Spezifikation wurde zuerst in [BEW99] vorgeschlagen. Dieser Algorithmus leitet von der Signalflankengraph-Spezifikation einen endlichen Automaten ab und übersetzt dann die Automaten in eine XBM-Spezifikation. Obwohl die XBM-Spezifikation einen Automaten darstellt, lässt sie gewisse Nebenläufigkeiten zu. Diese können direkt übersetzt werden. Ein Algorithmus, der direkt eine Signalflankengraph-Spezifikation in eine XBM-Spezifikation übersetzt, wird in Kapitel 7.3.1 vorgestellt. Dieser Algorithmus verbessert die Effizienz des in [BEW99] vorgeschlagenen Verfahrens. Allerdings können nicht alle Signalflankengraph-Spezifikation nur eine XBM-Spezifikation übersetzt werden, da die XBM-Spezifikation nur eine Teilmenge der im Signalflankengraph möglichen Nebenläufigkeiten erlaubt. Die Zerlegung des Signalflankengraphen kann verwendet werden, um eine Signalflankengraph-Spezifikation in eine XBM-Spezifikation übersetzbar

zu machen. Zerlegung löst aber nicht alle Probleme, da auch nach der Zerlegung einige Komponenten nicht in XBM-übersetzbar sind.

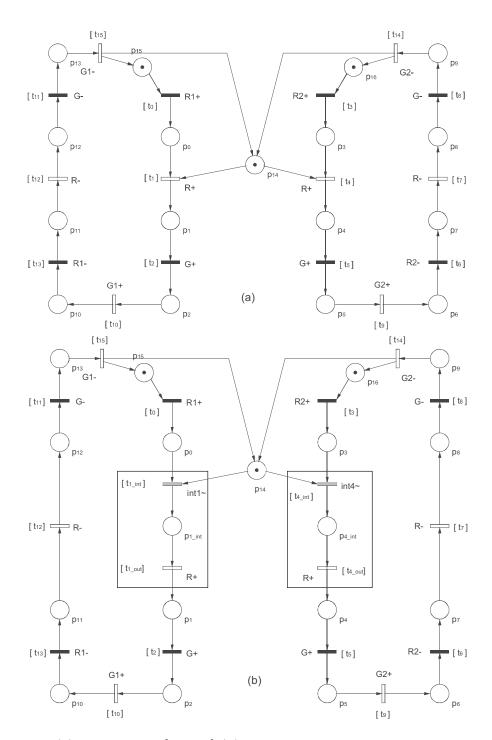

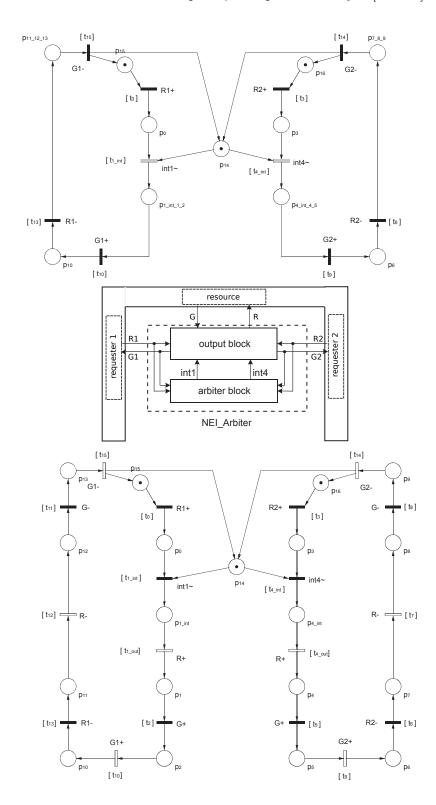

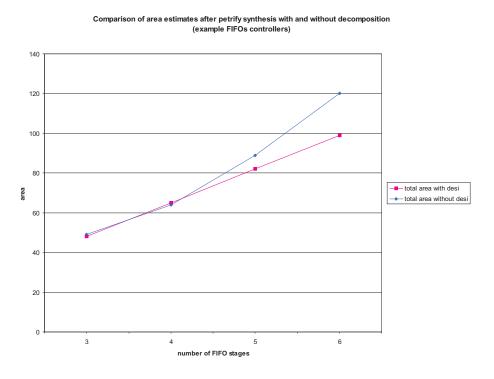

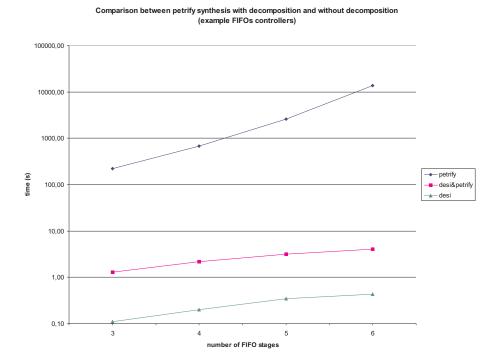

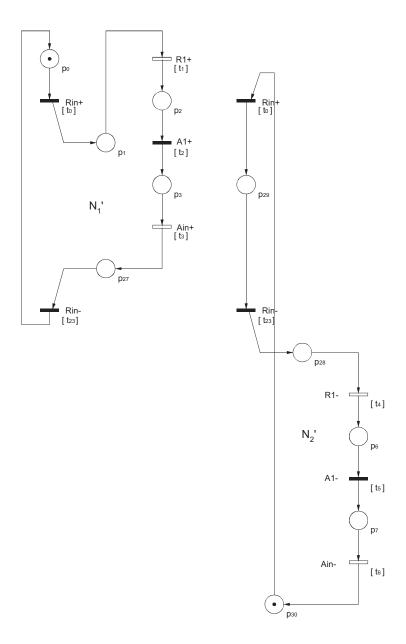

Am Ende werden mit DESI, ein Werkzeug zum Zerlegen von Signalflankengraphen und dessen Zerlegungsergebnisse vorgestellt. Es wird in Kapitel 7.4.1 gezeigt, dass mit DESI zerlegte Signalflankengraphen, welche eine große Anzahl von erreichbaren Markierungen aufweisen, effektiv zerlegt werden können. Mit Werkzeugen wie Petrify ist eine solche effektive Synthese nicht möglich, wenn die Anzahl der erreichbaren Markierung groß ist, da die Schaltung mehr Platz auf dem Chip benötigt wird. Es werden auch mehr Rechenressoucen und Zeit benötigt. Dies machte es unmöglich die Signalflankengraph-Spezifikation einen 7-stufigen FIFO-Speichersteuerung zu synthetisieren. Solche Probleme mit Rechenressourcen und Zeit gibt es bei der Zerlegung des Signalflankengraphen nicht. Die daraus resultierende Fläche ist nicht nur kleiner, sondern für eine kleine Anzahl von erreichbaren Markierungen, wie beispielsweise beim NEI-Arbiter kann man auch von der Zerlegung des Signalflankengraphen profitieren, indem man Bibliothekselemente wie z.B. ME-Elemente aus der Spezifikation extrahiert.

#### to my parent

$Johannes\ Sulaiman\ Kangsah\ and\ Maria\ Natalia\ Goretti$

# Acknowledgments

I would like to thanks Prof. Jochen Beister, my doctor father, who gives me advices, comments and corrections for my work, also he gives me the infrastructure and financial support to do research in his chair. Ralf Wollowski and Prof. Walter Vogler, who give me the chance to do research in the STG-decomposition project with them. Roland Hecker, who gives me financial and spiritual support at the hard time of my study. Prof. Wolfgang Kunz, who makes my promotion happen. My colleague, Karsten Laux, Meinrad Fiedler and Peter Kosack, who give feedbacks about my research. Peter Tawdross, Surya Warman, and Zhong Wei Li, for testing and implementing part of the proposed algorithm in this dissertation. Roland Hecker, Max Thalmeier and Stephan Herzog, who give me continuous motivation and spiritual support until the end phase of this dissertation. Also for Indonesian friends and neighbours, Ivan Solihin, Bahter and Maureen Bukit who help me a lot during the end phase. Dekanat Mr Hauck and Guthail for the promotion formalities. All the member of Stammtisch "der Freunde des Entwurfs programmierter Systeme" and the colleagues of Fa. Wipotec who cheering me up until the end phase of my promotion. For my wife, Ninasari, and the children, Hosea, Micha and Stella for their patience and support.

# $\overline{\text{Contents}}$

| A        | cknov      | wledgments                                             | vii       |

|----------|------------|--------------------------------------------------------|-----------|

| 1        | Intr       | roduction                                              | 1         |

| <b>2</b> |            | ri Net Background                                      | 3         |

|          | 2.1<br>2.2 | Place/Transition Nets                                  | 3<br>13   |

| 3        | Exis       | sting Decomposition Methods                            | 23        |

|          | 3.1        | P/T Net Decomposition: Analysis Purpose                | 24        |

|          | 3.2        | STG Decomposition: Synthesis Purpose                   | 26        |

|          |            | 3.2.1 Vogler-Wollowski algorithm                       | 27        |

| 4        | Imp        | provements for [VW02] algorithm                        | 35        |

|          | 4.1        | Grouping and ordering divining transitions             | 35        |

|          | 4.2        | Reuse of intermediate components                       | 37        |

|          | 4.3        | Deleting loop-only dummy transitions                   | 39        |

|          | 4.4        | Deleting duplicate transitions                         | 40        |

|          | 4.5        | Transition fusion                                      | 41        |

|          | 4.6        | Inserting internal signals                             | 48        |

|          | 4.7        | Securing non-secure t-contractions                     | 51        |

|          | 4.8        | Vogler-Kangsah algorithm                               | 52        |

| 5        | STO        | G Decomposition with SMD-subnets as Initial Components | <b>59</b> |

|          | 5.1        | The SMD-subnet method                                  | 61        |

|          | 5.2        | Free choice net extension                              | 71        |

|          |            | 5.2.1 Regulation circle path                           | 71        |

|          |            | 5.2.2 Level SCSM                                       | 72        |

|          |            | 5.2.3 Release of non-FC nets                           | 73        |

|          | 5.3        | Finding an SCSM cover algorithm                        | 74        |

|                           | 5.4   | SMD subnet algorithm                              | 77  |

|---------------------------|-------|---------------------------------------------------|-----|

| 6                         | P/T   | Γ-net Abstraction into Structure Graphs           | 87  |

|                           | 6.1   | Structure Graphs                                  | 88  |

|                           | 6.2   | Contracting middle node transitions               | 94  |

| 7                         | STO   | G Decomposition in Asynchronous Circuit Design    | 103 |

|                           | 7.1   | Asynchronous Circuits                             | 103 |

|                           | 7.2   | Speed Independent Circuits                        | 106 |

|                           | 7.3   | 3D Circuits                                       | 108 |

|                           |       | 7.3.1 From STG specification to XBM specification | 111 |

|                           | 7.4   | DESI                                              | 119 |

|                           |       | 7.4.1 Experimental Results for SI Circuits        | 120 |

| 8                         | Cor   | nclusion and Future Work                          | 127 |

| $\mathbf{B}^{\mathbf{i}}$ | bliog | graphy                                            | 133 |

## Chapter 1

## Introduction

Specification of asynchronous circuit behaviour becomes more complex as the complexity of today's System-On-a-Chip (SOC) design increases. This also causes the Signal Transition Graphs (STGs) – interpreted Petri nets for the specification of asynchronous circuit behaviour – to become bigger and more complex, which makes it more difficult, sometimes even impossible, to synthesize an asynchronous circuit from an STG with a tool like petrify [CKK<sup>+</sup>96] or CASCADE [BEW00].

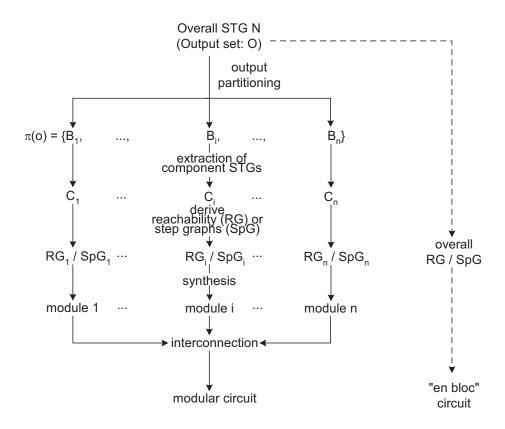

It has, therefore, been suggested to decompose the STG as a first step; this leads to a modular implementation [KWVB03] [KVWB05], which can reduce synthesis effort by possibly avoiding state explosion or by allowing the use of library elements. A decomposition approach for STGs was presented in [VW02] [KKT93] [Chu87a]. The decomposition algorithm by Vogler and Wollowski [VW02] is based on that of Chu [Chu87a] but is much more generally applicable than the one in [KKT93] [Chu87a], and its correctness has been proved formally in [VW02].

This dissertation begins with Petri net background described in chapter 2. It starts with a class of Petri nets called a place/transition (P/T) nets. Then STGs, the subclass of P/T nets, is viewed. Background in net decomposition is presented in chapter 3. It begins with the structural decomposition of P/T nets for analysis purposes – liveness and boundedness of the net. Then STG decomposition for synthesis from [VW02] is described.

The decomposition method from [VW02] still could be improved to deal with STGs from real applications and to give better decomposition results. Some improvements for [VW02] to improve decomposition result and increase algorithm efficiency are discussed in chapter 4. These improvement ideas are suggested in [KVWB04] and some of them are have been proved formally in [VK04].

The decomposition method from [VW02] is based on net reduction to find an output block component. A large amount of work has to be done to reduce an initial specification until the final component is found. This reduction is not always possible, which causes input initially classified as irrelevant to become relevant input for the component. But under certain conditions (e.g. if structural

auto-conflicts turn out to be non-dynamic) some of them could be reclassified as irrelevant. If this is not done, the specifications become unnecessarily large, which intern leads to unnecessarily large implemented circuits. Instead of reduction, a new approach, presented in chapter 5, decomposes the original net into structural components first. An initial output block component is found by composing the structural components. Then, a final output block component is obtained by net reduction.

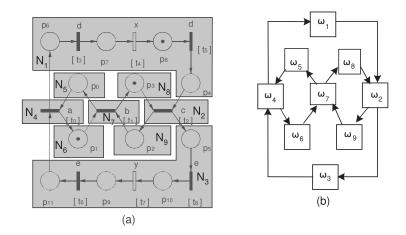

As we cope with the structure of a net most of the time, it would be useful to have a structural abstraction of the net. A structural abstraction algorithm [Kan03] is presented in chapter 6. It can improve the performance in finding an output block component in most of the cases [War05] [Taw04]. Also, the structure net is in most cases smaller than the net itself. This increases the efficiency of the decomposition algorithm because it allows the transitions contained in a node of the structure graph to be contracted at the same time if the structure graph is used as internal representation of the net.

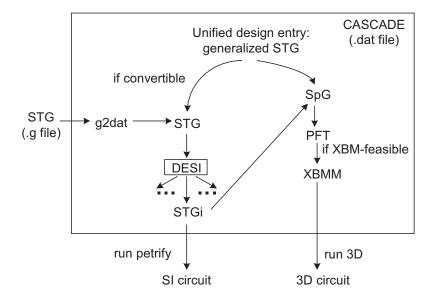

Chapter 7 discusses the application of STG decomposition in asynchronous circuit design. Application to speed independent circuits is discussed first. After that 3D circuits synthesized from extended burst mode (XBM) specifications are discussed. An algorithm for translating STG specifications to XBM specifications was first suggested by [BEW99]. This algorithm first derives the state machine from the STG specification, then translates the state machine to XBM specification. An XBM specification, though it is a state machine, allows some concurrency. These concurrencies can be translated directly, without deriving all of the possible states. An algorithm which directly translates STG to XBM specifications, is presented in chapter 7.3.1. Finally DESI, a tool to decompose STGs and its decomposition results are presented.

#### Chapter 2

# Petri Net Background

Petri nets have captured a large amount of interest since they were introduced by C.A.Petri [Pet66]. Many researchers have spent their effort in the theoretical and practical use of petri nets. Its graphical representation makes it easier for humans to capture the information it represents than text based representations do; petri nets are used in practice for modelling; e.g. to model the behaviour, especially concurrent behaviour, of dynamic systems. Not only that, they are a precise formal mathematical notation, which is a great advantage. Because of its formality, the model can be analyzed to determine, whether it has the properties needed for synthesis. If the model can be synthesized, then it can be implemented; e.g. as a circuit. Being a precise and compact formal model of concurrent behaviour, Petri nets have become a much used way of specifying the complex behaviour of systems which consist of components that work concurrently.

A petri net is a bipartite directed graph. A bipartite graph is a graph with two kinds of nodes, such that no arc connects two nodes of the same kind. In a directed graph, the arc connecting two nodes has direction. In petri nets, a *node* is either a place or a transition. In the graph representation, places are represented as circles and transitions as boxes. The places can be marked by tokens.

## 2.1 Place/Transition Nets

In this dissertation, a class of petri nets called a place/transition (P/T) nets is used. Unlike elementary nets, where places can only have Boolean markings (token/no token), or coloured nets, where tokens are distinguished by their so-called colours, the places of P/T nets can be marked by an integer number ( $\in IN_0$ ) of otherwise indistinguishable tokens [BC92]. The dynamics are modelled by the flow of tokens along the directed arcs to and from firing transitions. The number of token flowing over an arc will be called its weight.

**2.1.1.** DEFINITION. A place/transition net N is a tuple  $(P, T, F, M_0, W)$  where P is the set of places,

T is the set of transitions, (P and T are disjoint)

$F \subseteq P \times T \cup T \times P$  is the set of flow relation represented by directed arcs,

$M_0: P \to \mathbb{N}_0$  is the initial marking,

$C: P \to I\!\!N$  is the place capacity,

and  $W: P \times T \cup T \times P \to I\!N_0$  assigns weight to every pair (p,t) and (t,p). The weight denotes the number of tokens that must flow from p to t, repsectively from t to p, whenever transition t is fired. If p and t are connected by a directed arc, i.e. if (p,t) or (t,p) belong to F, a weight > 0 is assigned to the arc. If no arc connects p and t, i.e. if neither (p,t) nor (t,p) belongs to F, then W assigns weight 0 to both pairs.

Sometimes when applying a structural operation to N which only considers its initial marking,  $M_0$  of N is shortly denoted as  $M_N$ .

Because only P/T nets are discussed here, P/T nets will be referred to only as nets later in this dissertation. If a net N or N', etc. is introduced, it is assumed that implicitly this introduces its components  $(P, T, F, M_0, W)$  or  $(P', T', F', M'_0, W')$ , etc. For each node  $x \in P \cup T$  the preset of x is  ${}^{\bullet}x = \{y \mid (y, x) \in F\}$  and the postset of x is  $x^{\bullet} = \{y \mid (x, y) \in F\}$ .

By the weak firing rule, a transition t is enabled under a marking  $M(M:P \to IN_0)$ , denoted by M[t], if  $\forall p \in {}^{\bullet}t : W(p,t) \leq M(p)$ . If M[t]M', then we say t can be fired under M, yielding the follower marking M', in which  $\forall p \in P : M'(p) = M(p) + W(t,p) - W(p,t)$ . In contrast to the strong firing rule, the post places of t are not checked for, whether they have enough capacity to receive the tokens. Because of this, there is no need to consider the capacity of the places in the weak firing rule, and it is assumed that the capacity of the places is infinite. Because only the weak firing rule is used in this dissertation, when a transition is mentioned as firing, this will mean it fires under the weak rule.

If a finite sequence of firing transitions  $w \in T^*$  ( $T^*$  is a set of firing sequences) is enabled under a marking M, denoted by M[w], and yields the follower marking M' when occurring, this will be denoted by M[w]M'. A marking M is called reachable if  $\exists w \in T^*$  such that  $M_0[w]M$ . The set of markings reachable from  $M_0$  is denoted as  $R_{M_0}$ . It is represented graphically by a reachability graph.

A step is a set consisting of a single transition or of several concurrent and simultaneously firing transitions. If steps of more than one transition are to be considered, the reachability graph must be extended to become a step graph [Bei00]. A *state graph* with its *reachable states* is derived from the reachability graph or step graph for synthesis purposes.

#### **2.1.2.** DEFINITION. Let N be a P/T net.

•  $p \in P$  is n-bounded  $(n \in I\!\!N)$  iff for all reachable markings  $M \in R_{M_0}$ ,  $M(p) \leq n$ .

- N is n-bounded iff for all places  $p \in P$ , p is n-bounded.

- N is safe iff N is 1-bounded.

#### **2.1.3.** DEFINITION. Let N be a P/T net.

- $t \in T$  is live in  $M_0$  iff  $\forall M \in R_{M_0}, \exists M[w\rangle M'$  such that t is enabled under M'.

- N is live iff for all  $t \in T$ , t is live in  $M_0$ .

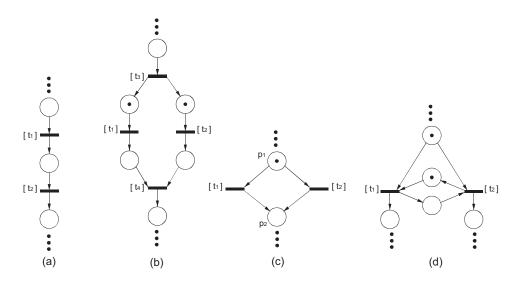

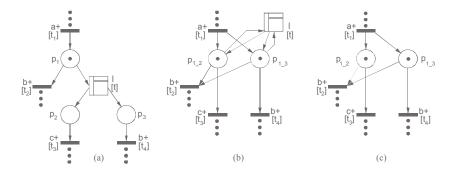

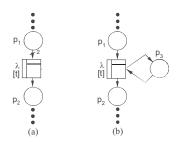

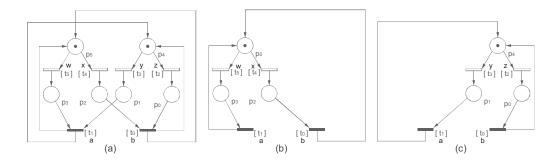

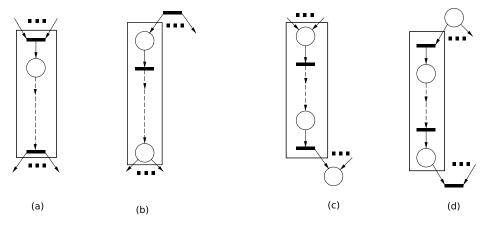

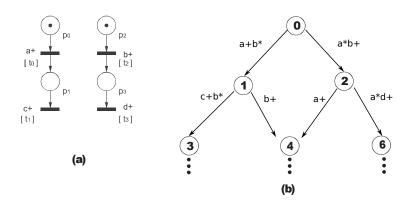

Figure 2.1. Basic relations in petri nets: (a) causal dependence (b)  $t_1, t_2$  are concurrent (c)  $t_1, t_2$  are in a structural conflict which is also a dynamic conflict (d)  $t_1, t_2$  are in a structural conflict which is not dynamic

A transition is called a *fork* transition iff  $|t^{\bullet}| > 1$  and it is called a *join* transition iff  $|{}^{\bullet}t| > 1$ ; e.g.  $t_3$  is a fork transition and  $t_4$  is a join transition in Fig. 2.1b. A place is called a *choice* place iff  $|p^{\bullet}| > 1$ , and it is called a *meeting* place iff  $|{}^{\bullet}p| > 1$ ; e.g.  $p_1$  is a choice place and  $p_2$  is a meeting place in Fig. 2.1c.

The terms fork, join, choice, and meeting, characterize not only the structure of the net. They also have a great influence on the dynamics of the net. A fork transition places tokens on each of its post places after firing. A join transition, instead, removes tokens from all of its pre places before firing. In contrast to a transition that can produce or consume tokens, places are passive. They can only distribute or gather tokens. A choice place distributes the tokens it has to one of its post transitions. A meeting place, instead, gathers tokens from its pre transitions.

Note that a transition (place) can be both a fork and a join transition (a choice and a meeting place). Hence, a transition can be classified either as a simple

transition or a fork transition or a join transition, or a fork and join transition. The same with the place: a place can be classified either as a simple place or a choice place or a meeting place or a choice and meeting place. This place and transition classification is important later when net abstraction is discussed.

There are three kinds of basic relations that we can represent by petri nets, namely:

- 1. The dependence relation: Transition  $t_2$  depends on transition  $t_1$  if  $t_1 \circ \cap t_2 \neq \emptyset$  (see Fig. 2.1a). Firing  $t_1$  will give concession to  $t_2$ .

- 2. The *independence* (concurrency) relation: Transition  $t_1$  and  $t_2$  are concurrent or (mutually) independent if there are enough tokens to enable  $t_1$  and  $t_2$  under a marking M (see Fig. 2.1b). Note that in Fig. 2.1c, if we add a token to  $p_1$ , we will have  $t_1$  concurrent to  $t_2$ .

- 3. the exclusion (conflict) relation: Transitions  $t_1$  and  $t_2$  are in structural conflict if there is a choice place  $p \in P, p \in {}^{\bullet}t_1 \cap {}^{\bullet}t_2$ . They could also be in dynamic conflict if there is a reachable marking M which enables  $t_1$  and  $t_2$ , and firing  $t_1$  will disable  $t_2$  or vice versa (deconcession). In Fig. 2.1c,  $t_1$  and  $t_2$  are in structural and dynamic conflict; but in Fig. 2.1d,  $t_1$  and  $t_2$  are in structural but not dynamic conflict.

A net N is an ordinary net, if  $\forall (x,y) \in F : W((x,y)) = 1$ , i.e. if all arc weights are restricted to 1. The following are subclasses of ordinary nets.

- A net N is a state machine (SM) if each transition has exactly one input place and one output place  $(\forall t \in T, |t^{\bullet}| = |^{\bullet}t| = 1)$ .

- A net N is a marked graph (MG) if each place has exactly one input transition and one output transition  $(\forall p \in P, |p^{\bullet}| = |^{\bullet}p| = 1)$ .

- A net N is a free choice (FC) net if  $\forall p \in P : \text{if } |p^{\bullet}| > 1 \text{ then } \bullet(p^{\bullet}) = \{p\}.$

- A net N is an extended free choice (EFC) net if  $\forall p, p' \in P$ : if  $p^{\bullet} \cap p'^{\bullet} \neq \emptyset$  then  $p^{\bullet} = p'^{\bullet}$

An essential property of FC nets is that if  $t_1$  and  $t_2$  share a common input place then it can never be the case that one of them is enabled while the other is not. That is, every marking enables either both of them or none of them. Hence, in a FC net, every structural conflict also is a dynamic conflict in a safe net. In the case of a non free choice conflict, the dynamic behaviour of the net, i.e. its reachable markings  $R_{M_0}$ , have to be derived first, before it can be determined whether the conflict is dynamic or not. This is the important difference between free choice and non free choice conflicts.

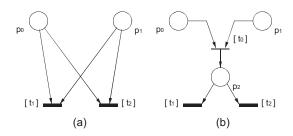

An EFC net can be transformed into an FC net as suggested by [Bes87]. Therefore, only FC nets will be considered further on this dissertation. Fig. 2.2 shows an example of a transformation of an EFC net into an FC net.

Figure 2.2. An EFC net (a), transformed into an FC net (b)

**2.1.4.** DEFINITION. A (directed) path of a net N is an alternating sequence of places and transitions  $(x_1, ..., x_i, x_{i+1}, ..., x_n)$ , n > 1, in which  $x_i \in P \cup T$  for  $1 \le i \le n$ ,  $(x_i, x_{i+1}) \in F$  and all  $x_i$ s are distinct for  $1 \le i < n$ . A path is called circle path iff  $x_1 = x_n$ . A circle path is called a loop iff n = 3.

**2.1.5.** DEFINITION. A net N is strongly connected iff  $\forall x, y \in P \cup T$  in which  $x \neq y$ , there is a directed path from x to y.

In a strongly connected net, there is always a path from one node to any other node in the net.

**2.1.6.** PROPOSITION. If there is a marking  $M_0$  such that an ordinary net N is live and bounded, then N is strongly connected.

**Proof:** See Satz 14.5 in [Sta90].

To be strongly connected is only a necessary condition for a net to be live and bounded. Hence, there are strongly connected nets which are not live or not bounded; see Fig. 2.3 for examples.

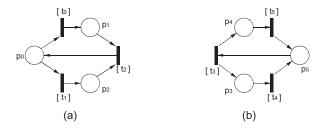

Figure 2.3. Strongly connected nets that are not (a) structurally live or (b) structurally bounded

In practice, nets may occur that are not strongly connected. They follow the pattern: start routine, process, stop routine (see Fig. 2.4a). But, such nets can be made strongly connected by adding dummy transitions which are connected

Figure 2.4. (a) not strongly connected net (b) strongly connected net

with all the stop places as pre places and all the start places as post places (see Fig. 2.4b). Clean-up transitions – e.g. the *dummy* transition in Fig. 2.4b – restore the initial state of the net from a final state.

Sometimes, it is easier first to consider the underlying structure of N. Only after the structural properties have been found, then the dynamic properties of the net – starting from initial marking  $M_0$  – are considered. This approach is used for example to find liveness and boundedness properties of N. The following are the structural definitions of liveness and boundedness of N: N is structurally bounded iff  $\exists k \in I\!N : \forall M_0, N$  is k-bounded. N is structurally live iff  $\exists M_0$  such that N is live.

**2.1.7.** Proposition. A marked graph has a live and safe initial marking iff it is strongly connected.

**Proof:** See Satz 14.11. in [Sta90].

**2.1.8.** Proposition. A state machine net is live and safe iff it is strongly connected and has only one token.

**Proof:** see Folgerung 14.13. in [Sta90].

The following definition is needed to find structural subnets of N.

**2.1.9.** DEFINITION. N' is a partial subnet of an ordinary net N  $(N' \leq N)$  iff  $P' \subseteq P$ ,  $T' \subseteq T$  and  $F' \subseteq F \cap ((P' \times T') \cup (T' \times P'))$ . N' is a subnet of an ordinary net N  $(N' \subseteq N)$  if  $P' \subseteq P$ ,  $T' \subseteq T$ , and  $F' = F \cap ((P' \times T') \cup (T' \times P'))$ .

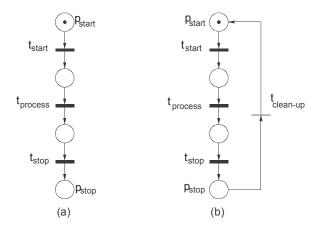

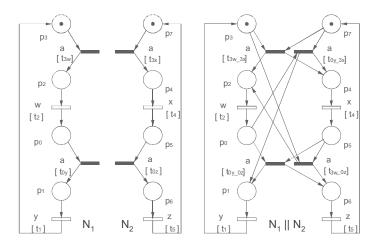

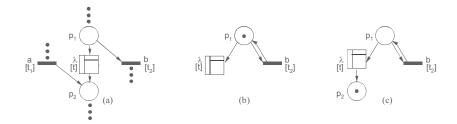

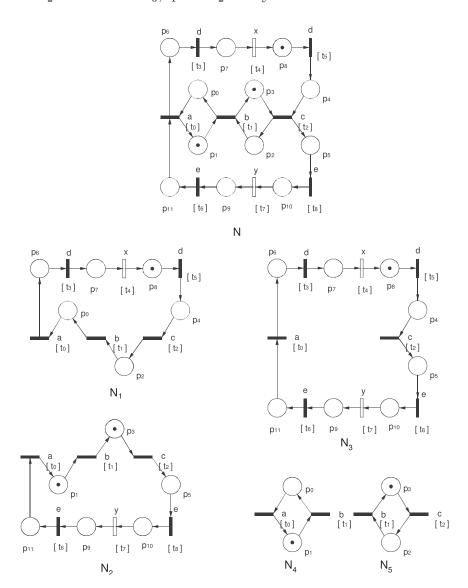

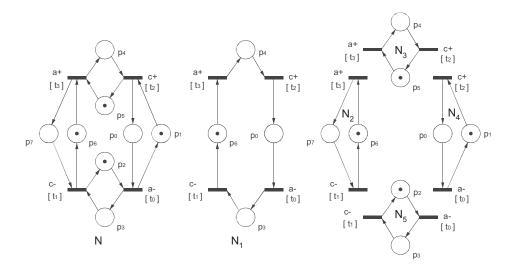

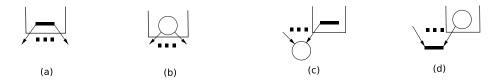

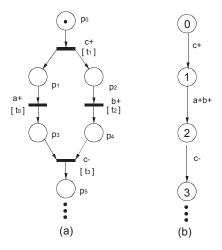

Figure 2.5. (a) A net N, (b) an SCSM subnet of N, (c) a subnet of N, (d) a partial subnet of N

Later, in decomposition of the net, a *component* which is responsible for producing a specified output is derived from a subnet. Fig. 2.5 shows examples for definition 2.1.9.

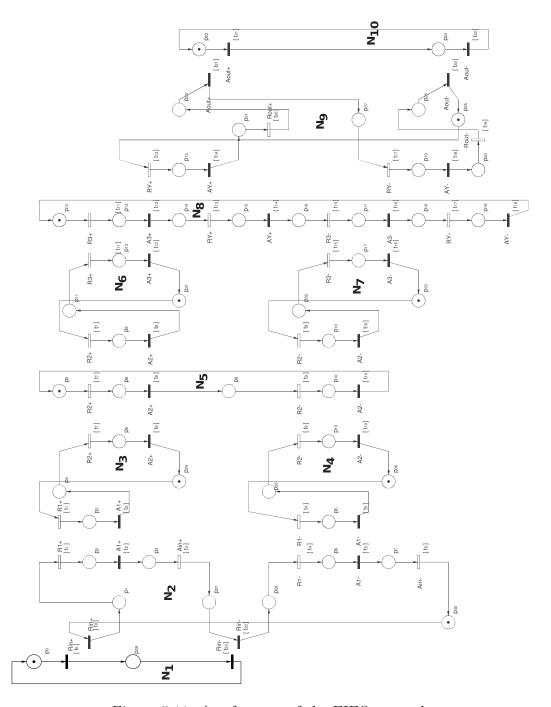

**2.1.10.** DEFINITION. An ordinary net N is state machine decomposable (SMD) iff there exists a collection of SCSM subnets  $N_i (1 \le i \le a)$  of N such that  $P = \bigcup P_i, T = \bigcup T_i, F = \bigcup F_i$ .  $\{N_1, ..., N_a\}$  is called a cover of N, and it is said that N is covered by  $\{N_1, ..., N_a\}$ .  $N' \subseteq N$  is the SMD-subnet of N if N' is an SMD net.

In an SMD net, the interaction between SCSM subnets is established through a subset of transitions which are called *synchronization transitions*.

- **2.1.11.** DEFINITION. Let N be an SMD net. A transition  $t \in T$  is a synchronization transition iff  $| {}^{\bullet}t | > 1$  or  $| t^{\bullet} | > 1$ .

- **2.1.12.** PROPOSITION. Let N be an SMD net. Every synchronization transition  $t \in T$  belongs to at least two different SCSM subnets of any cover of N.

**Proof:** In an SCSM subnet, each transition has only one pre- and one post place. Hence, if there is a synchronization transition in N, it should be owned by at least two different SCSM subnets of any cover of N.

**2.1.13.** DEFINITION. Let  $N_1$  be a partial subnet of an ordinary net N A path  $H = (x_1, ..., x_r), r > 1$  of N is a handle of  $N_1$  iff  $H \cap (P_1 \cup T_1) = \{x_1, x_r\}$ .

Note that from Def. 2.1.4,  $x_1, x_r$  could be the same node.

The handle is classified according to its first and last node; hence, a handle can be a PP-, PT-, TP-, or TT-handle.

Intuitively, a marked graph can be built from a single transition by successively adding TT-handles. The resulting net is a strongly connected marked graph which

has a live and safe initial marking according to proposition 2.1.7. Also, a state machine can be built from a single place by successively adding PP-handles. The resulting net is a strongly connected state machine which is live and safe if it has only one token according to proposition 2.1.8. Therefore, PP- and TT-handles are known as good handles.

In contrast, PT- and TP-handles could cause structurally non-live or non-bounded nets. Therefore they are called bad handles. In Fig. 2.3a, adding the PT-handle  $(p_0, t_0, p_1, t_2)$  to the circle path  $(t_1, p_2, t_2, p_0, t_1)$  results in a structurally non-live net. The net in Fig. 2.3b is structurally non-bounded because of the TP-handle  $(t_3, p_4, t_5, p_5)$  of the circle path  $(p_3, t_4, p_5, t_3, p_3)$ .

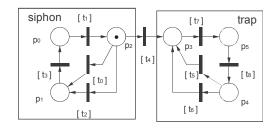

The notions of siphons (formally called deadlocks) and traps, both introduced by Commoner [Com72], have very interesting and useful properties concerning the liveness of a net.

A  $siphon\ S$  is a set of places in N such that every transition which puts a token on some place in S requires at least one token from some place in S. Hence, a siphon loses tokens each time a transition which has a pre place but no post place in S fires. This implies that if a siphon contains no tokens, it will receive no tokens from any possible firing sequence. Every transition having a pre place in the empty siphon will never be enabled.

A  $trap\ \Theta$  is a set of places in N such that every transition which takes a token from  $\Theta$  puts at least one token back into  $\Theta$ . Hence, a trap gains tokens each time a transition which has a post place but no pre place in  $\Theta$  fires. This implies, that once a trap is marked (i.e. contains at least one token), it will remain marked.

The formal definitions of siphons and traps are as follows.

- **2.1.14.** DEFINITION. Let N be an ordinary net.  $S \subseteq P$  is a siphon iff  $S \neq \emptyset$  and  ${}^{\bullet}S \subseteq S^{\bullet}$ . A siphon S is minimal iff there exists no siphon S' such that  $S' \subset S$ .  $\Theta \subseteq P$  is a trap iff  $\Theta \neq \emptyset$  and  $\Theta^{\bullet} \subseteq {}^{\bullet}\Theta$ .  $ST \subseteq P$  is a siphon trap iff  $ST \neq \emptyset$  and ST is a siphon which is also a trap. Hence,  ${}^{\bullet}ST \subseteq ST^{\bullet}$  and  $ST^{\bullet} \subseteq {}^{\bullet}ST$ ; i.e.  ${}^{\bullet}ST = ST^{\bullet}$ .

- **2.1.15.** DEFINITION.  $N' \subseteq N$  is the siphon(S)-subnet of N induced by siphon P' with  $T' = {}^{\bullet}P'$ .

$N' \subseteq N$  is the trap(T)-subnet of N induced by trap P' with  $T' = P'^{\bullet}$ .  $N' \subseteq N$  is the siphon-trap(ST)-subnet of N induced by siphon-trap P' with  $T' = {}^{\bullet}P' \cup P'^{\bullet}$ .

The set  $\{p_0, p_1, p_2\}$  in Fig. 2.6 is a siphon S, because the pre transitions of S,  $\{t_0, t_1, t_2, t_3\}$ , are a subset of  $\{t_0, t_1, t_2, t_3, t_4\}$ , which are the post transitions of S. The S-subnet induced by S is the one in the box marked "siphon" (see Fig. 2.6). If  $t_4$  is fired, then all the transitions in the S-subnet cannot be fired anymore.

The set  $\{p_3, p_4, p_5\}$  in Fig. 2.6 is a trap  $\Theta$ , because the post transitions of  $\Theta$ ,  $\{t_5, t_6, t_7, t_8\}$ , are a subset of  $\{t_4, t_5, t_6, t_7, t_8\}$ , which are the pre transitions of  $\Theta$ .

Figure 2.6. Siphon and trap example

The T-subnet induced by  $\Theta$  is the one in the box marked "trap" (see Fig. 2.6). If  $t_4$  is fired, then all the transitions in the T-subnet could be fired forever.

If a transition  $t_9$  with arcs  $(p_3, t_9)$  and  $(t_9, p_2)$  are added to the net in Fig. 2.6, then all the places in the net form a siphon-trap, and the ST-subnet of the siphon-trap is the net itself. In a siphon-trap net, there is token flow neither out of nor into the net.

**2.1.16.** DEFINITION. Let N be a net and N' a partial subnet of N.

A path (t, p) in N is a meeting path of N' iff  $p \in P'$  and  $(t, p) \notin F'$ . A meeting path (t, p) can be extended to a handle iff there exists a handle  $(x_1, ..., x_r) = (x_1, ..., t, p)$  of N';  $x_r = p$ ; if r = 2 then  $x_1 = t$ .

**2.1.17.** Proposition. In a strongly connected net, a meeting path can always be extended to a handle.

#### **Proof:**

From Def. 2.1.16, a meeting path (t,p) of N' has an arc  $(t,p) \notin F'$ . If  $t \notin T'$  then there is a directed path from  $x(x \in N')$  to t because N is strongly connected (see Def. 2.1.5); i.e. we have a handle (x, ..., t, p). If  $t \in T'$  then we have a TP-handle (t, p).

The following definition of a redundant place was introduced by [Ber87] and is adapted for decomposition by [VW02].

- **2.1.18.** DEFINITION. A place p of a net N is (structurally) redundant if there is a set of places  $Q \subset P$  with  $p \notin Q$ , a valuation  $V : Q \cup \{p\} \to I\!N$  and some  $c \in I\!N_0$  with the following properties for all  $t \in T$ :

- 1.  $V(p)M_N(p) \sum_{q \in Q} V(q)M_N(q) = c$  (For the initial marking, the valuated number of tokens on p is greater than or equal to the sum of the validated numbers of tokens on the places belonging to Q.)

<sup>&</sup>lt;sup>1</sup>The valuation V(r) of a place  $r \in Q \cup \{p\}$  is given to every token on r, flowing into r, and out of r

- 2.  $V(p)(W(t,p)-W(p,t)) \sum_{q\in Q} V(q)(W(t,q)-W(q,t)) \ge 0$  (When transition t occurs, the growth of the valuated number of tokens on p is greater than or equal to that of the places of Q.)

- 3.  $V(p)W(p,t) \sum_{q \in Q} V(q)W(q,t) \le c$  (The difference between the valuated number of tokens on p and those of places belonging to Q necessary to give concession to t must be less than or equal to this difference in the initial marking.)

- **2.1.19.** DEFINITION. Place p is a general duplicate of place q, if  $\forall t : W(p,t) W(q,t) = c, W(t,p) W(t,q) \ge c$ , and  $M_N(p) M_N(q) \ge c$ .

- **2.1.20.** Proposition. General duplicate place is a redundant place.

**Proof:** Substitute equation 1 to equation 3 of Def. 2.1.18 gives the following equation:  $V(p)(M_N(p) - W(p,t)) - \sum_{q \in Q} V(q)(M_N(q) - W(q,t)) \ge 0$ . We have  $Q = \{q\}$  and for V(p) = V(q) = 1, the above equation become  $M_N(p) - M_N(q) \ge W(p,t) - W(q,t)$  which is fulfilled per Def. 2.1.19; equation 2 of Def. 2.1.18 become  $W(t,p)-W(t,q) \ge W(p,t)-W(q,t)$  which is also fulfilled per Def. 2.1.19.

- **2.1.21.** DEFINITION. Place p is an extended duplicate of place q, if  $\forall t : W(t, p) = W(t, q), W(p, t) = W(q, t)$  and  $M_N(p) \geq M_N(q)$ .

- **2.1.22.** Proposition. Extended duplicate place is a redundant place.

**Proof:** Extended duplicate place is a general duplicate place with c = 0. Hence based on proposition 2.1.20, extended duplicate place is a redundant place.  $\Box$

- **2.1.23.** DEFINITION. In ordinary net, place p is a practical duplicate of place q, if  ${}^{\bullet}p = {}^{\bullet}q$ ,  $p^{\bullet} = q^{\bullet}$  and  $M_N(p) \geq M_N(q)$ .

- **2.1.24.** Proposition. Practical duplicate place is a redundant place.

**Proof:** Practical duplicate place is an extended duplicate place, i.e. if  $t \in {}^{\bullet}p$  then  $t \in {}^{\bullet}q$  and W(t,p) = W(t,q) = 1; if  $t \notin {}^{\bullet}p$  then  $t \notin {}^{\bullet}q$  and W(t,p) = W(t,q) = 0; if  $t \in p^{\bullet}$  then  $t \in q^{\bullet}$  and W(p,t) = W(q,t) = 1; if  $t \notin p^{\bullet}$  then  $t \notin q^{\bullet}$  and W(p,t) = W(q,t) = 0. Hence based on proposition 2.1.22, practical duplicate place is a redundant place.

### 2.2 Signal Transition Graphs

As event-driven systems, asynchronous circuits respond immediately and in general concurrently to rising and falling edges of their binary input signals x, namely by generating edges of their output signals y. The interaction between circuit and environment across their interface can be modeled from the causal point of view by signal transition graphs (STGs). The first proposals were made by [Wen77], [RY85], and [Chu86], with extensions and generalization by [VYCLdM94], [Wol97], and [WB00]. In this dissertation, unless otherwise mentioned only STGs without extensions and generalizations are considered.

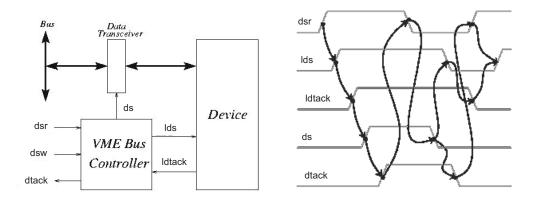

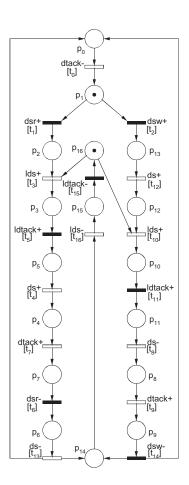

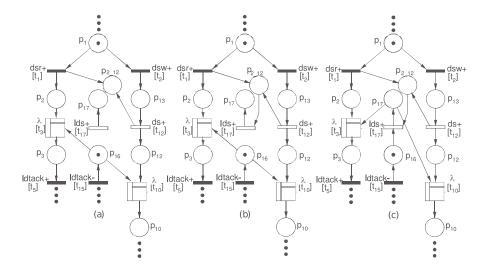

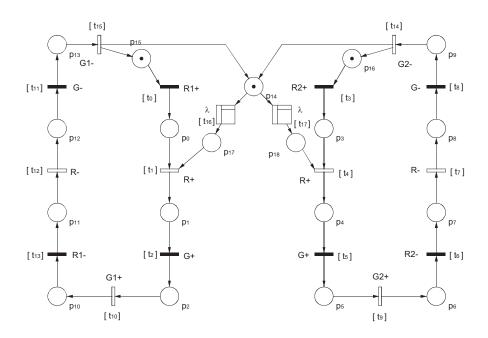

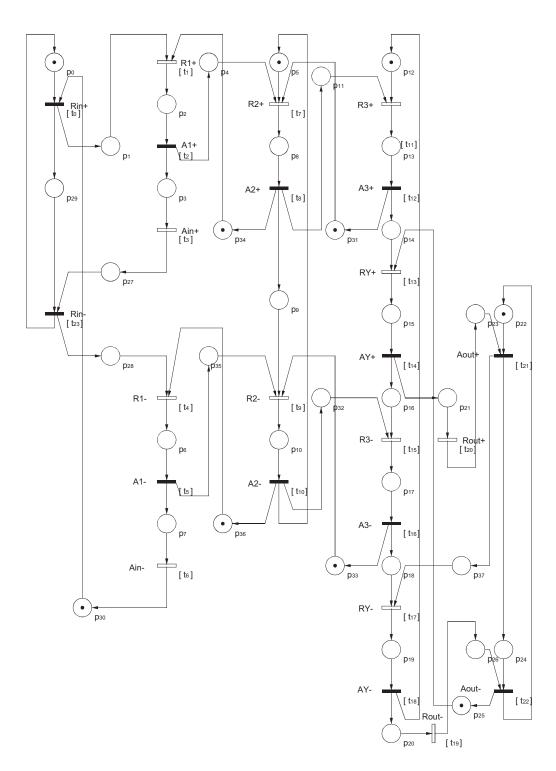

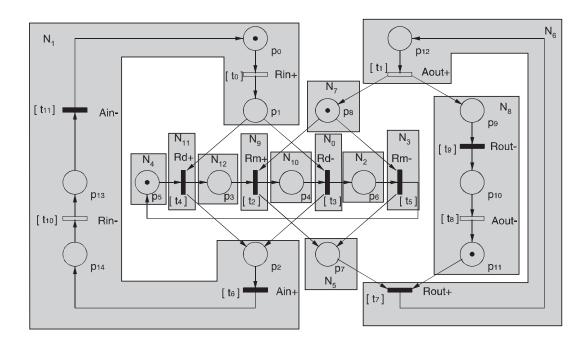

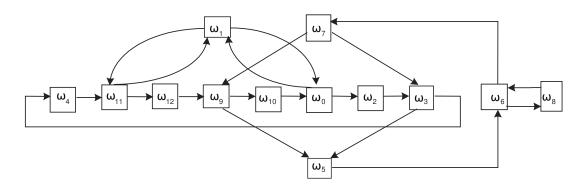

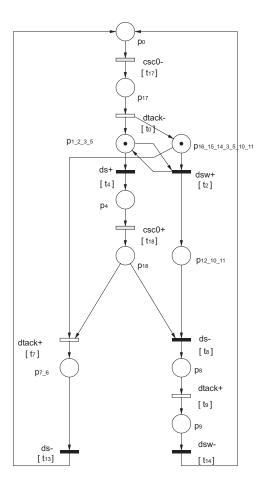

A controller is a circuit that synchronize the operations performed by an operational unit – e.g. counter, ALU, etc. – through a protocol. Fig. 2.7 shows part of the timing diagram of a VME bus controller from [CKK $^+$ 02] (only for the dsr+ case). The STG describing the complete timing diagram is shown in Fig. 2.8.

Figure 2.7. Timing diagram example

Firing a transition in the STG means an occurrence of a signal edge; therefore, transitions in an STG are labelled with signals from some alphabet  $\Sigma \times \{+, -\}$  or with the empty word  $\lambda$ .  $\{+, -\}$  denote the edges: s+ means a rising edge of s and s- means a falling edge of s.

The types of transitions in this dissertation are:

- input transitions,

- output transitions,

- divining transitions transitions that have been silenced,

- internal transitions transitions of internal signals that are unobservable at the system interface and required for synthesis,

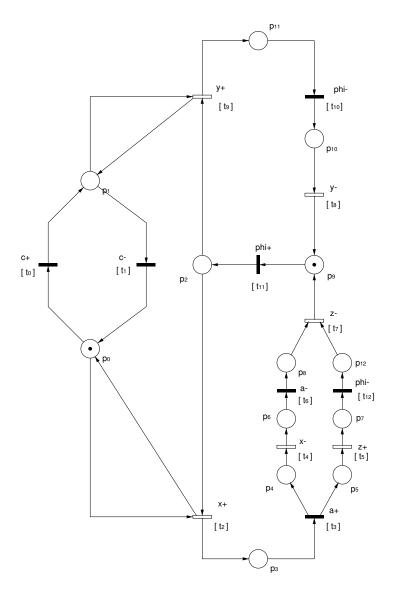

Figure 2.8. VME bus controller STG  $\,$

• dummy transitions do not represent signal changes and are labelled with the empty word  $\lambda$  – used to simplify petri net structure and to make the graph easier to understand.

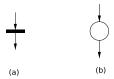

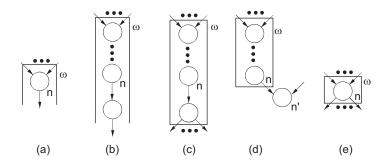

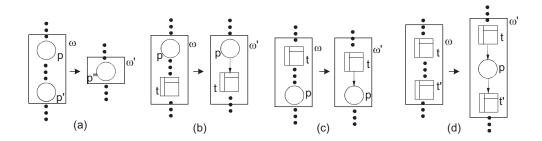

In a graph, transitions are represented as a filled box (input), an empty box (output), a gray box (internal), a line (dummy), or box with two lines (divining). See Fig. 2.9 for illustration.

Figure 2.9. (a) An input transition, (b) an output transition, (c) an internal transition, (d) a dummy transition, (e) a divining transition

**2.2.1.** DEFINITION. An STG N is a tuple  $(P, T, F, M_0, W, l, In, Out)$  where P is the set of places,

T is the set of transitions, (P and T are disjoint)

$F \subseteq P \times T \cup T \times P$  is the flow relation, i.e. the set of directed arcs,

$M_0: P \to I\!N_0$  is the initial marking,

$C: P \to I\!\!N$  is the place capacity,

$W: P \times T \cup T \times P \to \mathbb{N}_0$  assigns weights to the pairs (p,t) and (t,p). Pairs belonging to F (the directed arcs) are assigned weights > 0; pairs  $\notin F$  (non-existent arcs) are assigned weight 0,

$l: T \to In \times \{+, -\} \cup Out \times \{+, -\} \cup \{\lambda\}$  is the label of transitions, where  $In \subset \Sigma$  is the set of input signals,

$Out \subseteq \Sigma$  is the set of output signals,

and  $\overline{In}$  and Out are disjoint.

The labelling of transition sequences can be extended as follows;  $l(t_1...t_n) = l(t_1)...l(t_n)$ , where the empty word is deleted automatically. A sequence v of signal edges is enabled under a marking M, denoted by M[v], if there is some transition sequence w with M[w] and l(w) = v; M[v] if M[w] if M[w]. If  $M = M_0$ , then v is called a trace. The language L(N) is the set of all traces. Two STGs are language equivalent if they have the same traces.

Due to the physical nature of the signal, signal edges are required to alternate. An STG is *consistent* if for all signals  $s \in l$ , in every trace of the STG, the edges s+ and s- alternate, and there are no two traces where s+ comes first in the one and s- in the other.

Two different transitions  $t_1$  and  $t_2$  are enabled concurrently under a marking M if  $W(.,t1) + W(.,t2) \leq M$ , i.e. if there are enough tokens for both transitions to be fired together. If both transitions have the same label  $s_{edge}$ , then  $s_{edge}$

is enabled auto-concurrently under M. An STG has no auto-concurrency, if no  $s_{edge}$ -transitions are enabled auto-concurrently under any reachable marking.

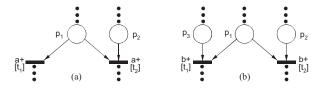

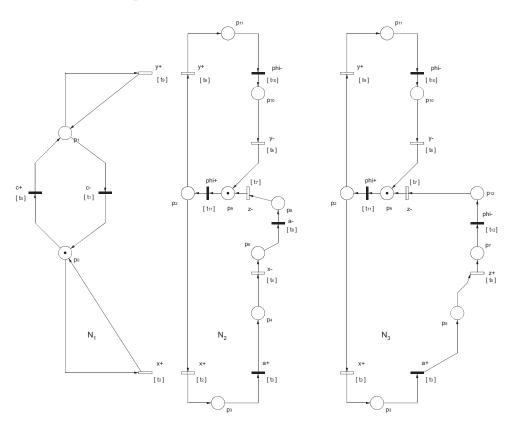

If two different transitions  $t_1$  and  $t_2$  are in structural conflict and are labelled with the same  $s_{edge}$ , then they are in *structural auto-conflict*, and the STG has such a conflict. If  $t_1$  is an input and  $t_2$  an output transition, then they form a *structural input-output conflict* and the STG has such a conflict. If both  $t_1$  and  $t_2$  are output transitions labelled with different signals, then they form a *structural output-output conflict*, and the STG has such a conflict.

If two different transitions  $t_1$  and  $t_2$  are in dynamic conflict and are labelled with the same  $s_{edge}$ , then they are in *dynamic auto-conflict*, and the STG has such a conflict.

Transitions in free choice conflict are transitions that have the same pre places:  ${}^{\bullet}t_1 = {}^{\bullet}t_2$ . In a safe net, these transitions are in dynamic conflict: if one transition is enabled, then the others also are enabled. If there is another place in pre place of t besides the choice places, then this place is called control place. Another example of dynamic conflict are transitions in structural conflict where the choice place(s) are the only pre places of at least one transition:  ${}^{\bullet}t_1 \cap {}^{\bullet}t_2 = {}^{\bullet}t_1$  or  ${}^{\bullet}t_1 \cap {}^{\bullet}t_2 = {}^{\bullet}t_2$ ; i.e. there is a transition without control places. In contrast, if each of the transitions in structural conflict has a control place in addition to the conflict place(s), then these transitions would not be in dynamic conflict, unless there is a reachable marking M that enables two or more of them.

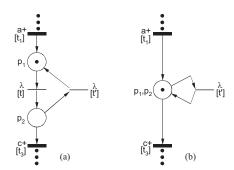

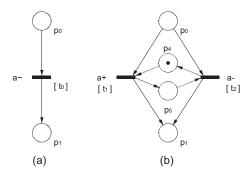

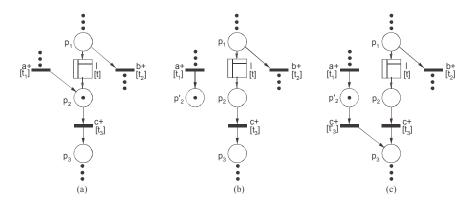

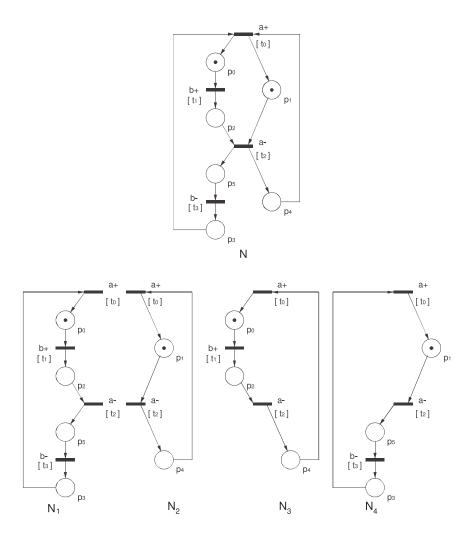

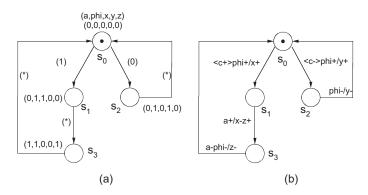

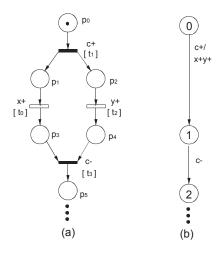

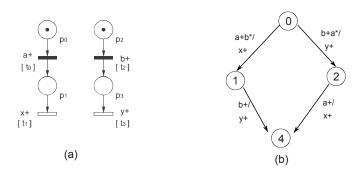

Figure 2.10. Structural auto-conflict

Fig. 2.10 shows two STGs with a structural auto-conflict. The STG in Fig. 2.10a has a structural auto-conflict between the transitions  $t_1$  and  $t_2$  (both labelled a+); it also is a dynamic auto-conflict, because the choice place  $p_1$  is the only pre place of  $t_1 - t_1$  has no control place, so that when  $t_2$  is enabled,  $t_1$  is also enabled. In contrast, the structural auto-conflict between  $t_1$  and  $t_2$  (both labelled b+) in Fig. 2.10b is not necessarily dynamic because each transition in conflict has a control place; perhaps there is no reachable marking under which both transitions are enabled.

An STG is deterministic if it has no internal transitions and if for each of its reachable markings and each  $s_{edge}$ , there is at most one  $s_{edge}$ -labelled transition enabled under the marking, i.e., no auto-concurrency and no dynamic auto-conflict.

An STG is *synthesizable* <sup>2</sup> if it is deterministic and consistent. It is also required that the synthesizable STG has no dynamic input-output conflict, because such an STG cannot be synthesized into a reliable (i.e. hazard free) digital circuit; except with some timing constraint. Most synthesis tools also require STGs to be live and safe to be synthesizable.

The following backgrounds are needed for STG decomposition.

- **2.2.2.** DEFINITION. A secure t-contraction (based on [And83]) of STG N, resulting in  $\overline{N}$ , is done as follows:

- (a) Merge each pre place of t with each post place of t:  $\overline{P} = \{p \mid p \in P {}^{\bullet}t \cup t^{\bullet}\} \cup \{(p, p') \mid p \in {}^{\bullet}t, p' \in t^{\bullet}\}$   $\underline{M}_{\overline{N}}((p, p')) = M_{N}(p) + M_{N}(p')$   $\overline{W}((p, p'), t_{1}) = W(p, t_{1}) + W(p', t_{1}), \forall t_{1} \in T$   $\overline{W}(t_{1}, (p, p')) = W(t_{1}, p) + W(t_{1}, p'), \forall t_{1} \in T$

- (b) Delete t and all its incident loop arcs:  $\overline{T} = T - t$   $\overline{W}((p, p'), t) = 0$   $\overline{W}(t, (p, p')) = 0$

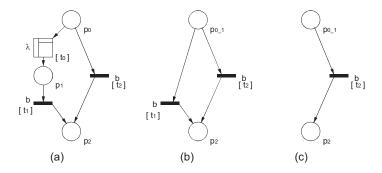

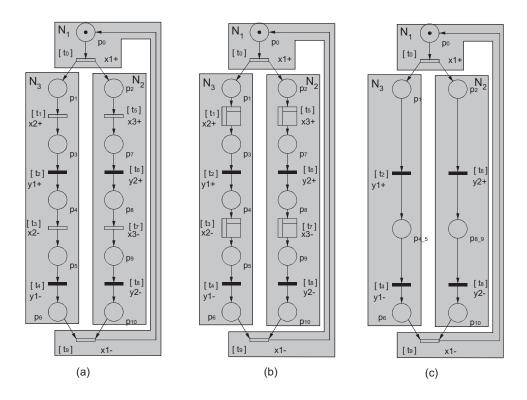

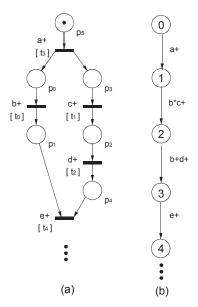

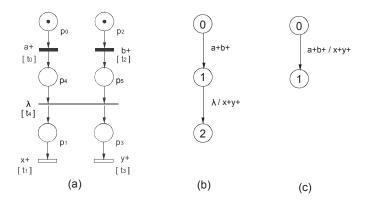

For simplicity, in the graph, the merge place of  $p_1$  and  $p_2$  is denoted as  $p_{1,2}$  instead of  $(p_1, p_2)$ . Fig. 2.11 shows an example for step by step contraction. Fig. 2.11a is the initial STG, upon which secure contraction of transition t will be performed. Fig. 2.11b is the STG after merging each  $p \in {}^{\bullet}t = \{p_1\}$  with each  $p \in t^{\bullet} = \{p_2, p_3\}$ . Hence we have  $p_{1,2}$  with  $M_{\overline{N}}(p_{1,2}) = M_N(p_1) + M_N(p_2) = 1$  and  $p_{1,3}$  with  $M_{\overline{N}}(p_{1,3}) = M_N(p_1) + M_N(p_3) = 1$ . Note that when merging places, the incident arcs of the place are kept intact. Fig. 2.11c is the STG after deleting loop-only transition t and all its incident loop arcs.

Figure 2.11. Secure t-contraction

$<sup>^2</sup>$ means "synthesizable without hazards and timing constraints", e.g. that a hazard-free asynchronous circuit without timing constraints can be built

Simulations are a well-known important device for proving language inclusion or equivalence. A simulation from  $N_1$  to  $N_2$  is a relation  $\mathcal{S}$  between markings of  $N_1$  and  $N_2$  such that  $(M_{N_1}, M_{N_2}) \in \mathcal{S}$  and for all  $(M_1, M_2) \in \mathcal{S}$  and  $M_1[t\rangle M_1'$  there is some  $M_2'$  with  $M_2[l_1(t)\rangle\rangle M_2'$  and  $(M_1', M_2') \in \mathcal{S}$ . If such a simulation exists, then  $N_2$  can go on simulating all signals of  $N_1$  forever. If there exists a simulation from  $N_1$  to  $N_2$ , then  $L(N_1) \subseteq L(N_2)$ .

A relation  $\mathcal{B}$  is a bisimulation between  $N_1$  and  $N_2$  if it is a simulation from  $N_1$  to  $N_2$  and  $\mathcal{B}^{-1}$  is a simulation from  $N_2$  to  $N_1$ . If such a bisimulation exists, we call the STGs bisimilar; intuitively, the STGs can work side by side such that in each stage each STG can simulate the signals of the other.

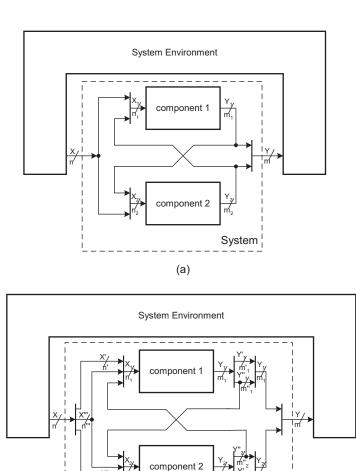

In the following definition of parallel composition  $\parallel$ , the distinction between input and output signals is important and will be considered. The idea of parallel composition is that the composed systems run in parallel synchronizing on common signals. Since a system controls its outputs, it is not allowed that a signal is an output of more than one component; input signals, on the other hand, can be shared. An output signal of one component can be an input of one or several others, and in any case it is an output of the composition (see Fig. 2.12).

The parallel composition  $\parallel$  of STGs  $N_1$  and  $N_2$  is defined if  $Out_1 \cap Out_2 = \emptyset$ . Then, let  $A = (In_1 \cup Out_1) \cap (In_2 \cup Out_2)$  be the set of common signals. In Fig. 2.12b, these common signals are  $(X''', Y_2'', Y_1'')$ . In the parallel composition  $N = N_1 \parallel N_2$ , each  $s_{edge}$ -labelled transition  $t_1$  of  $N_1$  is combined with each  $s_{edge}$ -labelled transition  $t_2$  from  $N_2$  if  $s_{edge} \in A$ . In the formal definition of parallel composition, \* is used as a dummy element, which is formally combined e.g. with those transitions that do not have their label in the synchronization set A. (\* is assumed not to be a transition or a place of any net.) Thus, N is defined by

$$P = P_1 \times \{*\} \cup \{*\} \times P_2$$

$$T = \{(t_1, t_2) \mid t_1 \in T_1, t_2 \in T_2, l_1(t_1) = l_2(t_2) \in A\}$$

$$\cup \{(t_1, *) \mid t_1 \in T_1, l_1(t_1) \notin A\}$$

$$\cup \{(*, t_2) \mid t_2 \in T_2, l_2(t_2) \notin A\}$$

$$W((p_1, p_2), (t_1, t_2)) = \begin{cases} W_1(p_1, t_1) & \text{if } p_1 \in P_1, \ t_1 \in T_1 \\ \text{or} \\ W_2(p_2, t_2) & \text{if } p_2 \in P_2, \ t_2 \in T_2 \end{cases}$$

$$W((t_1, t_2), (p_1, p_2)) = \begin{cases} W_1(t_1, p_1) & \text{if } p_1 \in P_1, \ t_1 \in T_1 \\ \text{or} \\ W_2(t_2, p_2) & \text{if } p_2 \in P_2, \ t_2 \in T_2 \end{cases}$$

Figure 2.12. (a) parallel composition block diagramm and (b) its detail

(b)

$$l((t_1, t_2)) = \begin{cases} l_1(t_1) & \text{if } t_1 \in T_1 \\ l_2(t_2) & \text{if } t_2 \in T_2 \end{cases}$$

$$M_N = M_{N_1} \dot{\cup} M_{N_2}, \text{ i.e. } M_N((p_1, p_2)) = \begin{cases} M_{N_1}(p_1) & \text{if } p_1 \in P_1 \\ M_{N_2}(p_2) & \text{if } p_2 \in P_2 \end{cases}$$

$$In = (In_1 \cup In_2) - (Out_1 \cup Out_2)$$

$$Out = Out_1 \cup Out_2$$

For simplicity, in the graph, a place of the composition is denoted as p instead of (p,\*) or (\*,p); also transition is denoted as t instead of (t,\*) or (\*,t), and  $t_{1,2}$  instead of  $(t_1,t_2)$ . Also, to keep the example small, the transitions are only labelled with signals instead of signal edges. An example of parallel composition follows.

Figure 2.13. Parallel composition example

In the example, there are two transitions with label a in  $N_1$ :  $t_{3w}$  and  $t_{0y}$ , and two in  $N_2$ :  $t_{3x}$  and  $t_{0z}$ . Each transition with label a in  $N_1$  should be synchronized with each transition with label a in  $N_2$ . Therefore, in  $N_1 \parallel N_2$ , there are four transitions with label a: a synchronization of  $t_{3w}$  with  $t_{3x}$  ( $t_{3w-3x}$ ),  $t_{3w}$  with  $t_{0z}$  ( $t_{3w-0z}$ ),  $t_{0y}$  with  $t_{3x}$  ( $t_{0y-3x}$ ) and  $t_{0y}$  with  $t_{0z}$  ( $t_{0y-0z}$ ). Note that though there is a synchronization between  $t_{0y}$  and  $t_{3x}$ , and between  $t_{3w}$  and  $t_{0z}$ , the synchronized transitions  $t_{0y-3x}$  and  $t_{3w-0z}$  in  $N_1 \parallel N_2$  will never be fired. However, all these possible pairings have to be done, because it is not known a priori which s-labelled transition of  $N_2$  will occur together with which s-labelled transition of  $N_1$ .

One can consider the place set of the composition as the disjoint union of the place sets of the components. Therefore, markings of the composition (regarded as multisets) can be considered as the disjoint union of markings of the components. Sometimes – e.g. if a bisimulation-like correctness definition (see section 3.2.1) is

used –, it is useful to look only at the restriction  $M|_{P_i}$  of a marking M of the composition.

A marking  $M_1 \dot{\cup} M_2$  of the composition is also denoted by  $(M_1, M_2)$ . By definition of  $\parallel$ , the firing  $(M_1, M_2)[(t_1, t_2)\rangle(M_1', M_2')$  of  $N(N = N_1 \parallel N_2)$  corresponds to the firings  $M_i[t_i\rangle M_i'$  in  $N_i$ , i=1,2; here, the firing of \* means that the empty transition sequence fires. Therefore, all reachable markings of N have the form  $(M_1, M_2)$ , where  $M_i$  is a reachable marking of  $N_i$ , i=1,2.

If the components do not have internal transitions, then their composition has none. To see that N is deterministic if  $N_1$  and  $N_2$  are, consider different transitions  $(t_1, t_2)$  and  $(t'_1, t'_2)$  with the same label that are enabled under the reachable marking  $(M_1, M_2)$ . The transitions should differ in at least one component; suppose  $t_1, t'_1$  are different transitions in  $N_1$ . It cannot be the case that  $t_1$  is a transition while  $t'_1 = *$ , because we would have  $l((t_1, t_2)) \in In_1 \cup Out_1$  but  $l((t'_1, t'_2)) \notin In_1 \cup Out_1$ ; i.e.  $l((t'_1, t'_2)) \notin A$ . Therefore,  $t_1$  and  $t'_1$  are different transitions with the same label. Because  $(t_1, t_2)$  and  $(t'_1, t'_2)$  are enabled under the reachable marking  $(M_1, M_2)$ ,  $t_1$  and  $t'_1$  are enabled under the reachable marking  $M_1$ , which contradicts that  $N_1$  is deterministic. But note that  $N_1$  might have structural auto-conflicts even if none of the  $N_i$  has. The example in Fig. 2.13 shows this case.

Up to isomorphism, composition is associative and commutative. Therefore, the parallel composition of a family (or collection)  $(C_i)_{i\in I}$  of STGs can be denoted as  $||_{i\in I} C_i$ , provided that no signal is an output signal of more than one of the  $C_i$ . The markings of such a composition will be denoted by  $(M_1, \ldots, M_n)$  if  $M_i$  is a marking of  $C_i$  for  $i \in I = \{1, ..., n\}$  where n is the number of an output block in a partition.

#### Chapter 3

# Existing Decomposition Methods

In the time of imperialism in this world, the strategy 'divide et impera' is used by a conqueror to conquer a large country with a small force. He first divides the large country into two or more parts governed by opposing parties, and then conquer them, one by one. The same strategy is used by many researchers to conquer (to analyze and synthesize) a large net (with high concurrency degree) by dividing it into two or more small nets. I.e. by decomposition, a net is divided into subnets.

The first motivation for decomposing a P/T net is to analyze it. For example, to find whether a net is live or not, one must first derive its reachable markings. This task is difficult and sometimes impossible for a large, highly concurrent net due to the  $state\ explosion$  problem; i.e. the number r of reachable markings is too large to handle.

As P/T nets are used more and more to model systems, another problem is encountered if a circuit is to be synthesized from the net. Because one should derive the reachable markings of the net as the first synthesis step, the same problem as when analyzing the net occurs, i.e. the state explosion problem. Not only that, many of the synthesis algorithms that derive the implementation from reachable states have exponential complexity. This task is difficult and sometimes impossible for a large number of reachable states. One can try to alleviate this problem by using a heuristic algorithm which has polynomial complexity. But if the problem is large, sometimes one can find only a solution that represents a local minimum in solution space, i.e. a non-optimal result. Therefore, the decomposition of P/T nets is used to address the above problems, hoping that the overall effort and cost of synthesizing the components will be significantly smaller than for handling the large net.

This chapter begins with the structural decomposition of P/T nets for analysis purposes – liveness and boundedness of the net. Then STG decomposition for synthesis from [VW02] is described.

## 3.1 P/T Net Decomposition: Analysis Purpose

The early P/T net decomposition is aimed at analyzing the liveness and boundedness of the net. The researchers first looked for the smallest structures of P/T nets that can be used to characterize liveness and boundedness. This is the cause for the birth of the siphon and trap definitions, which were first suggested by [Com72]. [Com72] and [Hac72] used siphons and traps to prove liveness and safeness of FC nets. Similar approach was also used by [BT87] and [EBS89].

A siphon S which contains a trap  $\Theta$  which is marked at  $M_0$  will always contain a token; hence the transitions of  $S^{\bullet}$  can always be fired. If all the siphons in the net contain a trap which is marked at  $M_0$ , then all the transitions in the net can be fired. For an FC net, this also means that the net is live.

**3.1.1.** Proposition. An FC net N is live iff every minimal siphon of N contains a trap which is marked at  $M_0$ .

Proof: see [Hac72]. □

3.1.2. PROPOSITION. A live FC net N is safe iff it is covered by SCSM-subnets which have exactly one token each at M<sub>0</sub>.

Proof: see Theorem 6.5. in [BT87]. □

Note that proposition 3.1.2 implies strong connectedness of N.

3.1.3. PROPOSITION. In a live and safe FC net N, if S is a minimal siphon of N, then S is also a trap.

Proof: see Lemma 6.9. in [BT87]. □

**3.1.4.** Proposition. In a live and safe FC net N, a subnet  $N_S$  induced by a minimal siphon  $P_S$  is an SCSM-subnet of N.

**Proof:** see Lemma 6.10. in [BT87].

**3.1.5.** COROLLARY. Let N be a live and safe FC net. Every SCSM-subnet of N is marked at  $M_0$  and there exists an SCSM-cover of N, such that each  $N_i$  belonging to the SCSM-cover has exactly one token at  $M_0$ .

**Proof:** N is live. Therefore, every minimal siphon contains a trap which is marked at  $M_0$  (proposition 3.1.1). N also is safe; therefore every subnet  $N_S$  induced by a minimal siphon  $P_S$  is an SCSM-subnet of N (proposition 3.1.4). Hence, being both live and safe, FC net N is covered by SCSM subnets which have exactly one token each at  $M_0$  (proposition 3.1.2).

Using a graph theoretical approach, [BL89] characterize minimal siphons in P/T nets. Based on this characterization, [EBS89] derive a minimal siphon characterization for FC nets.

**3.1.6.** PROPOSITION. Let N be an FC net,  $P_S \subseteq P$  a siphon of N and  $N_S$  the subnet of N induced by  $P_S \cup {}^{\bullet}P_S$ .  $P_S$  is minimal iff  $P_S$  is strongly connected and we have  $|{}^{\bullet}t \cap P_S| = 1$  for every transition  $t \in N_S$ .

Proof: see [EBS89] □

Based on proposition 3.1.6, [EBS89] propose an algorithm to find the subnet  $N_S$  induced by minimal siphon S. The algorithm concentrates on a specific part of the net. Beginning with a seed node of the net, it gradually adds parts of the net (handles) until the subnet is found.

#### Algorithm S-subnet

**Input:** A strongly connected FC net with a *seed* place  $\bar{p}$

**Output:** S-subnet induced by the minimal siphon  $P_S$

- 1.  $P_S := \{\overline{p}\}; T_S := \emptyset; F_S := \emptyset;$

- 2. while  $\exists p \in P_S \text{ and } \exists t \in {}^{\bullet}p \text{ such that } (t,p) \notin F_S \text{ do}$

- 3.  $get\_meeting\_path\_handle(N_S, N, p, t, N_H);$

- 4. (\*  $N_H$  (which is a path in N but not a path in  $N_S$ ) is a handle of  $N_S$  that begins with a node in  $N_S$  and ends with t, p \*)

- 5.  $P_S := P_S \cup P_H; T_S := T_S \cup T_H; F_S := F_S \cup F_H;$

- 6. (\* end of while there is still a meeting path of  $N_S$  \*)

The algorithm S-subnet begins with  $N_S$  which has only one seed place p. The S-subnet  $N_S$  is found by iteratively adding a meeting path handle to the current  $N_S$ , so long as the resulting  $N_S$  still has meeting paths.

The net in Fig. 2.6 is taken as an example.  $p_2$  is the seed place. After adding  $p_2$  to  $N_S$ , there is a meeting path  $(t_1, p_2)$  that should be extended to a handle. The extension is the handle  $H_1 = (p_2, t_0, p_1, t_3, p_0, t_1, p_2)$ . After adding  $H_1$  to  $N_S$ , there is still a meeting path  $(t_2, p_1)$  that should be extended to a handle. The extension is the handle  $H_2 = (p_2, t_2, p_1)$ . After adding  $H_2$  to  $N_S$ , there is no more meeting path to be found. Hence,  $N_S$  (the net in the siphon box of the Fig. 2.6) is an S-subnet and  $P_S$  is a minimal siphon of N.

The algorithm *S-subnet* generates S-subnets with the following properties [EBS89]:

- 1. The resulting net is strongly connected, because at the beginning there is only one place and the operation of adding a meeting handle (see definition 2.1.16 and proposition 2.1.17) preserves strong connectedness.

- 2. Every transition t in  $T_S$  has exactly one incoming arc in  $N_S$ . t has at least one incoming arc due to strong connectedness, and t has at most one incoming arc because the added meeting handle always ends in a place.

- 3. Because all the meeting paths of  $p \in P_S$  are taken, we have  $T_S = {}^{\bullet}P_S$ ; and because not all choice paths of  $p \in P_S$  are taken, we have  $T_S \subseteq P_S^{\bullet}$ .  $N_S$  is an S-subnet of N; i.e. all the arcs  $f \in F$  between nodes in  $N_S$  should also be in  $F_S$ . Assume this is not the case, which means there is an arc  $f \in F$  between nodes in  $N_S$  that is not in  $F_S$ . It could be an arc from a place  $p \in P_S, |p^{\bullet}>1|$  to a transition  $t \in T_S, |{}^{\bullet}t>1|$ , which cannot be the case in an FC net; or it could be an arc from a transition  $t \in T_S$  to a place  $p \in P_S$ , which cannot be the case because all the meeting paths have been taken.

From the above properties, it is obvious that the proposition 3.1.6 is true; i.e.  $P_S$  is a minimal siphon of N.

Using the rank theorem, [Esp90] improved the liveness and boundedness characterization of an FC net. [KB92] used this improvement and proposed a polynomial algorithm to decide liveness and boundedness of an FC net. It also decides state machine decomposability by finding minimal siphons of the FC net using the [EBS89] algorithm and checks whether the net induced by the minimal siphon is a state machine.

An improved version of the [Esp90] algorithm proposed by [Kem93] yields a linear-time algorithm for finding the minimal siphons of a strongly connected FC net. The C++ implementation of the [Kem93] algorithm and experiment results can be seen in [War05].

#### 3.2 STG Decomposition: Synthesis Purpose

[Chu87a], [Chu87b], and [KKT93] suggest decomposition methods for STGs, but these approaches can only deal with very restricted net classes. [Chu87a] only decomposes live and safe FC nets, which cannot model controlled choices or arbitration, and makes further restrictions; e.g. each transition label is allowed only once (which makes the STG deterministic in the sense of language theory), and conflicts can only occur between input signals. The conference version [Chu87b] restricts attention even further to marked graphs, which have no conflicts at all.

The method in [Chu87a] and [Chu87b] constructs for each output signal s a component  $C_i$  that generates this signal;  $C_i$  has as inputs all signals that – according to the net structure – may directly cause s to change. The component is obtained from the STG N by contracting all transitions belonging to the signals

that are neither input nor output signals for this component. This contraction is required to be tr-preserving (as defined in [Chu87a]) , and it might be necessary to add further signals to the inputs to ensure this.

In [Chu87a] [Chu87b], it is stated that the parallel composition of the  $C_i$  – i.e. the (modular) implementation – has the same language as N; in the restricted setting of [Chu87a] [Chu87b], this is the same as having isomorphic reachability graphs. Clearly, this isomorphism is very strict and not a necessary requirement for an implementation to be correct (see section 3.2.1). On the other hand, language equivalence is too weak in general, since it ignores which choices are possible during a run, and in particular it ignores deadlocks as will be shown in section 3.2.1.

A similar decomposition method is described in [KKT93]; only marked graphs with only output signals are considered. In contrast to [Chu87a], a component can generate several output signals, and different components can generate the same signal; this gives more flexibility, but the latter feature necessitates additional components for collecting occurrences of the same signal generated by different components.

[BW93] and [Wol97] use a decomposition approach like [Chu87a] to implement a modular asynchronous controller. Also, [KGJ96] use a decomposition approach for fork/join machines, which are a restricted form of FC STGs. After decomposition, the results are implemented as distributed burst mode circuits.

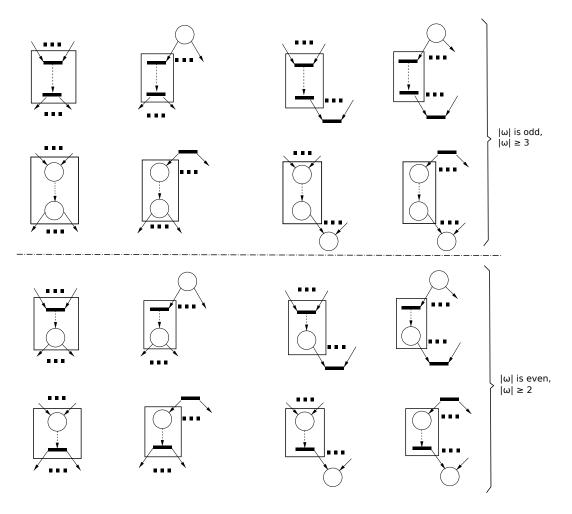

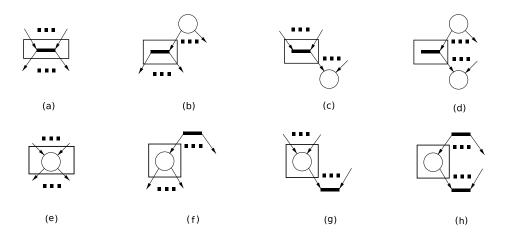

#### 3.2.1 Vogler-Wollowski algorithm

The decomposition method from Vogler-Wollowski [VW02] is based on [Chu87a]. In contrast to other methods, it can be applied without restriction to the graph theoretic structure of the given STG. It can even deal with arc weights greater than 1 and unsafe nets. It only restricts STG N to be deterministic and synthesizable. Also, the main difference between the algorithm [VW02] and others is the correctness proof. The algorithm [VW02] is proved to be correct and can be applied to labelled P/T nets which are more general than STGs. The following are the features of the algorithm [VW02]:

- The composition of the  $C_i$  is ensured to be free of what Ebergen calls computation interference [Ebe92] (see Fig. 3.7 for a computation interference example), where one component produces an output that is an unspecified input for another.

- Only behaviour where the environment behaves as specified by the original STG N is considered, i.e. the composition of the components might specify additional inputs, but these and any subsequent behaviour is ignored since they cannot occur if the implementation runs in an appropriate environment. The same is done e.g. in [Dil88] and [Ebe92], so both these features are not new but new in the context of STG decomposition.

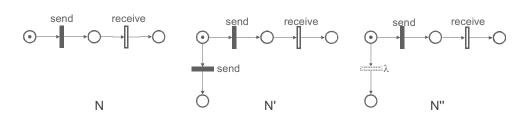

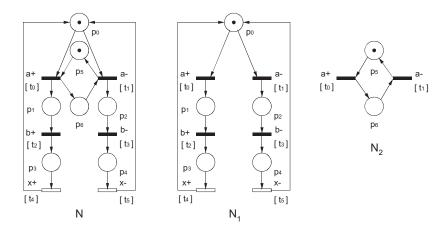

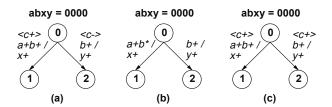

These features are achieved with a bisimulation-like correctness definition. Bisimulation is chosen instead of language equivalence, because bisimulation can distinguish between deterministic and non-deterministic STG. The STGs in Fig. 3.1 are language equivalent, i.e. they have the same language  $\{\lambda, send, send receive\}$ . But they are not bisimilar. N can simulate N' and N''. But N' cannot simulate N (N' can deadlock after send), also N'' cannot simulate N (N'' can deadlock after firing internal  $\lambda$ -transition).

Figure 3.1. Language equivalent STGs which are not bisimulation equivalent

For deterministic STGs, language equivalence and bisimulation coincide. N' and N'' in Fig. 3.1 are not deterministic STG; N' is not deterministic due to the dynamic auto conflict and N'' is not deterministic due to the internal  $\lambda$ -transition.

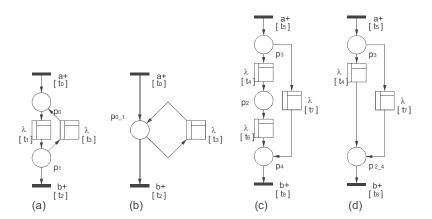

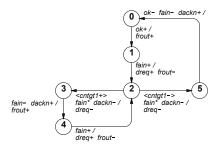

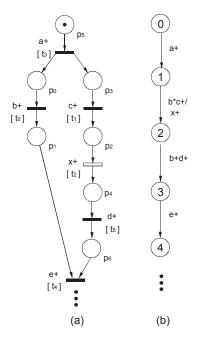

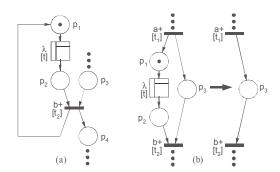

1. Before contracting a divining transition t, the *preconditions* should be checked for: that the pre and post arcs of t have weight 1, and that t forms no loop with any place. Fig. 3.2a shows an STG that violates the arc weight requirement:  $W(p_1,t)=2$ ; Fig. 3.2b shows an STG that violates the no loop requirement: t forms a loop with  $p_3$ . Hence, none of the two fulfil the preconditions for t-contraction.

It should also be checked whether the secure t-contraction requirement is fulfilled: either  $({}^{\bullet}t)^{\bullet} \subseteq \{t\}$  (either t has no preplaces or every preplace of

Figure 3.2. Violation of preconditions for t contraction

t has only t as its posttransition); or  $\bullet(t^{\bullet}) = \{t\}$  and  $\forall p \in t^{\bullet} : M_N(p) = 0$  (every postplace of t has only t as its pretransition and has no token at initial marking). A divining transition that violates this secure t-contraction requirement is a non-secure transition. Fig. 3.3 shows STGs that violate the no choice place in the pre place requirement:  $({}^{\bullet}t)^{\bullet} = \{t, t_2\} \nsubseteq \{t\}$ ; the one in Fig. 3.3a also violates the no meeting place in post place requirement:  $({}^{\bullet}t)^{\bullet} = \{t_1, t_2\} \neq \{t\}$ . This violation can cause a backfiring if t is contracted; after t is contracted, firing  $t_1$  will enable  $t_2$ . The one in Fig. 3.3b violates the post place requirement:  $\nexists p \in t^{\bullet}$ . After firing t in Fig. 3.3b, the net is dead. But, if t is contracted, the net is never dead. The one in Fig. 3.3c violates the no marking in post place requirement:  $M_N(p_2) = 1$ . This violation can cause a dead net to become alive. After contracting t in Fig. 3.3c,  $t_2$  is enabled. Hence, none of the STGs in Fig. 3.3 fulfills the secure t-contraction requirements.

Figure 3.3. Violations of secure t-contraction requirements

If there is a precondition for t-contraction or a secure t-contraction requirement that cannot be fulfilled, then backtracking is performed, i.e. the  $s_{edge}$ -label of t and every other  $t \in T_i$  labelled with s is restored; and s is considered as a relevant signal for  $C_i$ .

- 2. If all the above requirements are fulfilled, then a secure transition contraction (see definition 2.2.2) can be performed.

- 3. After contraction, it should be checked whether the secure t-contraction has

caused a dynamic auto conflict or not. If it caused a dynamic auto conflict, then backtracking should be done. Fig. 2.11c shows a case where backtracking becomes necessary; because after secure t-contraction of t labelled  $\lambda$  (Fig. 2.11b), we have  $t_2$  labelled with b+ and  $t_4$  labelled with b+ in a structural auto conflict which is also a dynamic auto conflict.

4. If there is a redundant place (see definition 2.1.18) after contraction, it should be removed together with its incident arcs.

Steps 1-4 are performed on all divining transitions in STG  $N_i$ . At the end, after changing transitions with label  $a \in Out_N, a \notin Out_i$  into input transitions, the component  $C_i$  is obtained.

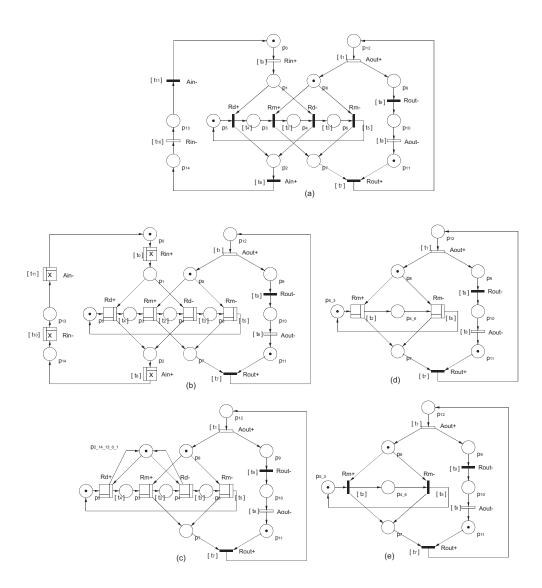

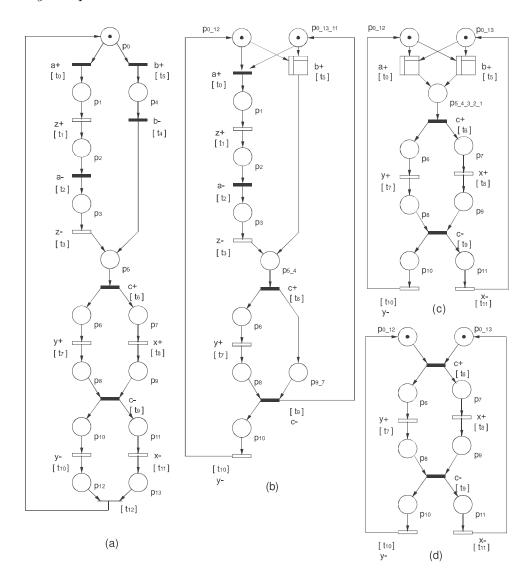

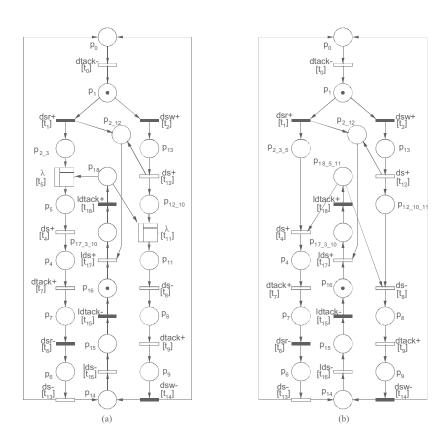

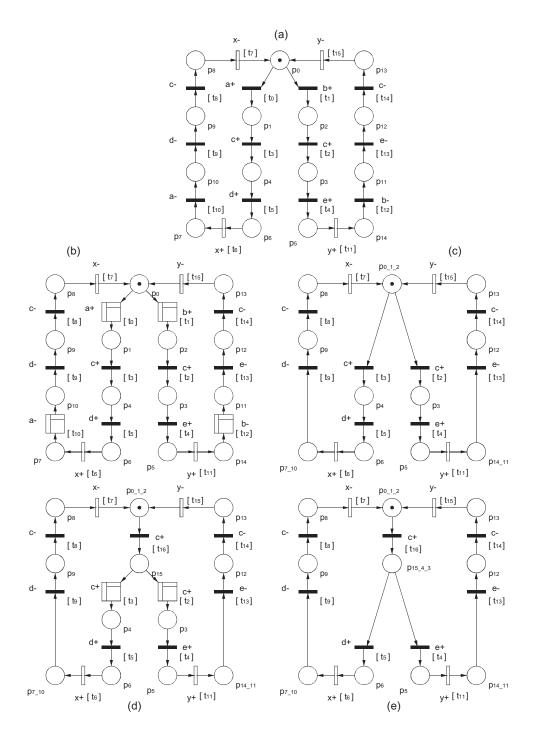

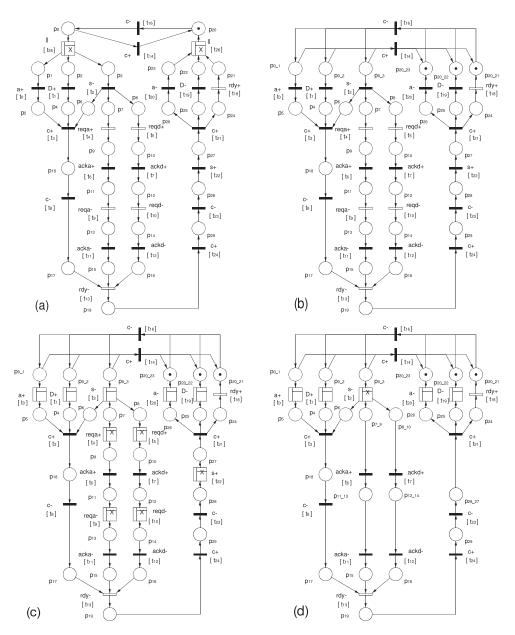

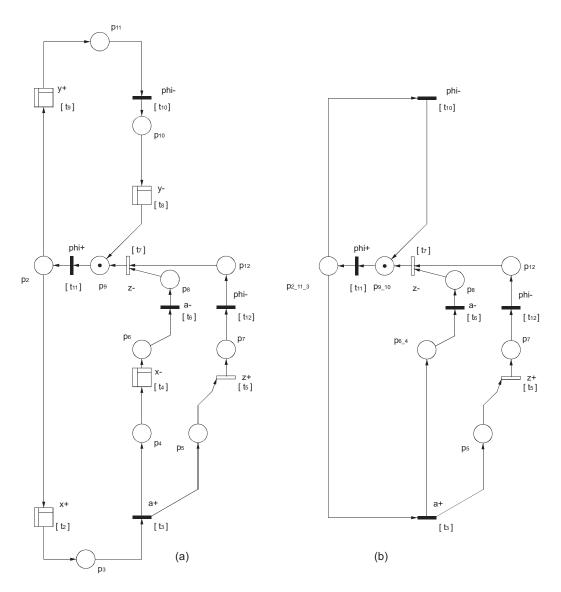

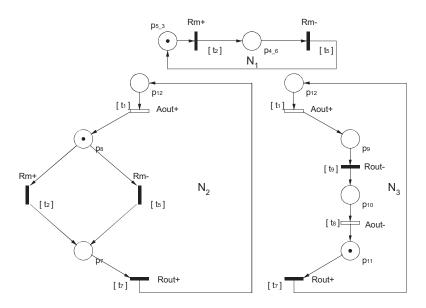

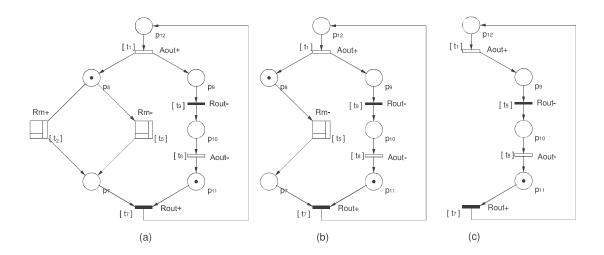

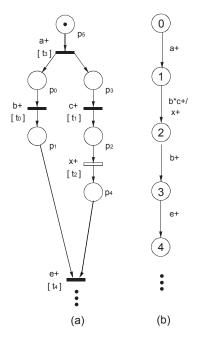

Secure transition contraction and redundant place deletion is the *admissible* operations for [VW02] method.

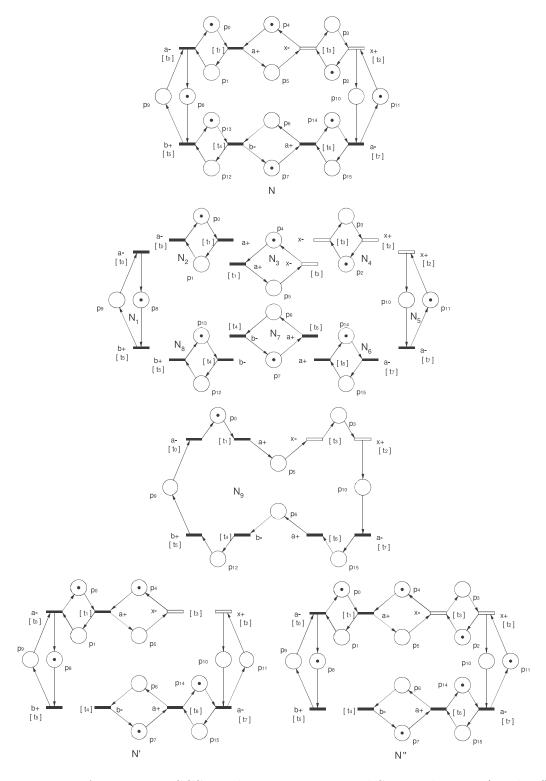

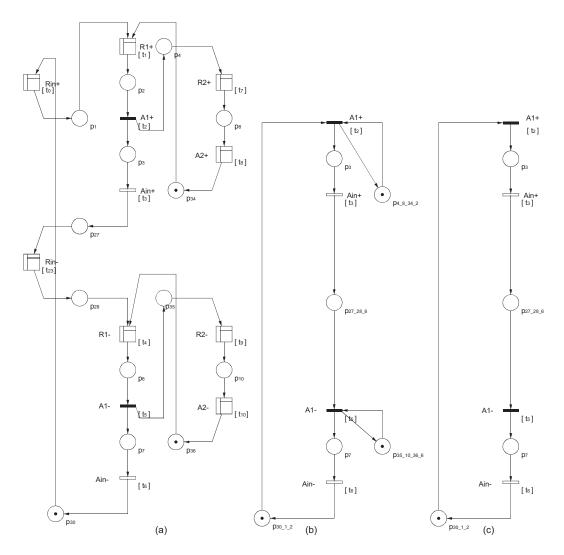

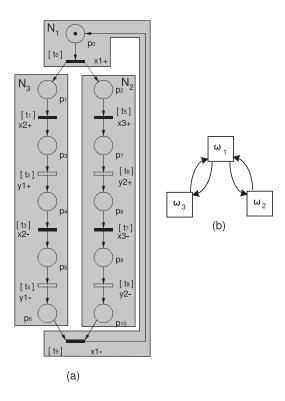

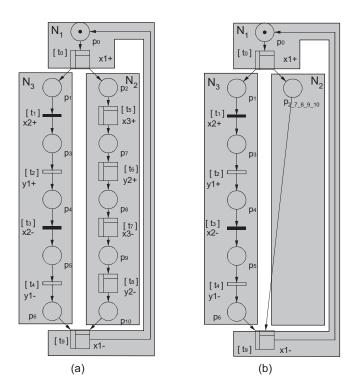

As an example, the environment STG N for the wechselpuffer example from Beister is taken (see Fig.3.4a). For the Aout-component, only transitions with signal Rout are relevant – transitions with label Aout are  $t_1$  and  $t_8$ ;  $t_7$  gives concession to  $t_1$ ,  $t_9$  to  $t_8$ ;  $t_7$  and  $t_9$  are labelled with Rout. After making a copy of N as initial Aout-component, all transitions with irrelevant signal label are silenced (see Fig.3.4b; the labels of the silenced transitions are kept for convenience). Note that trying to contract  $t_3$  or  $t_4$  at the beginning will cause backtracking, because they are non-secure transitions. After secure contraction of  $t_6$ ,  $t_{11}$ ,  $t_{10}$ , and  $t_0$  (see Fig.3.4c), the redundant place  $p_{2\_14\_13\_0\_1}$  is deleted. Now,  $t_3$  and  $t_4$  can be contracted securely (see Fig.3.4d). Further contraction of  $t_2$  or  $t_5$  is not possible, because they are non-secure transitions. Hence, backtracking should be done for both of them; i.e. Rm is added as relevant input signal. After backtracking, the end Aout-component is obtained (see Fig.3.4e).

The [VW02] algorithm has been proved to be correct according to the following definition 3.2.1.

- **3.2.1.** DEFINITION. A collection of deterministic components  $(C_i)_{i \in I}$  is a correct decomposition or a correct implementation of a deterministic STG N, if the parallel composition C of the  $C_i$  is defined,  $In_C \subseteq In_N$ ,  $Out_C \subseteq Out_N$  and there is a relation  $\mathcal{B}$  between the markings of N and those of C with the following properties.

- 1.  $(M_N, M_C) \in \mathcal{B}$

- 2. For all  $(M, M') \in \mathcal{B}$ , we have:

- (a) If  $a \in In_N$  and  $M[a\rangle\rangle M_1$ , then either  $a \in In_C$  and  $M'[a\rangle\rangle M'_1$  and  $(M_1, M'_1) \in \mathcal{B}$  for some  $M'_1$  or  $a \notin In_C$  and  $(M_1, M') \in \mathcal{B}$ .

- (b) If  $x \in Out_N$  and  $M[x\rangle\rangle M_1$ , then  $M'[x\rangle\rangle M'_1$  and  $(M_1, M'_1) \in \mathcal{B}$  for some  $M'_1$ .

Figure 3.4. Finding *Aout*-component for wechselpuffer example

- (c) If  $x \in Out_C$  and  $M'[x\rangle\rangle M'_1$ , then  $M[x\rangle\rangle M_1$  and  $(M_1, M'_1) \in \mathcal{B}$  for some  $M_1$ .

- (d) If  $x \in Out_i$  for some  $i \in I$  and  $M'|_{P_i}[x\rangle\rangle$ , then  $M'[x\rangle\rangle$  (no computation interference).

Here, and whenever a collection  $(C_i)_{i \in I}$  is encountered in the following,  $P_i$  stands for  $P_{C_i}$ ,  $Out_i$  for  $Out_{C_i}$  etc.

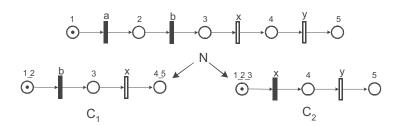

In the definition 3.2.1, C is allowed to have fewer input signals than N; the reasons are as follows: There might be some input signals that are not relevant for producing the right outputs; whereas N makes some assumptions on the environment regarding these inputs, C does not – hence, the environment might produce these signals any time, but they are ignored. Such irrelevant input signals are called *globally irrelevant* inputs.

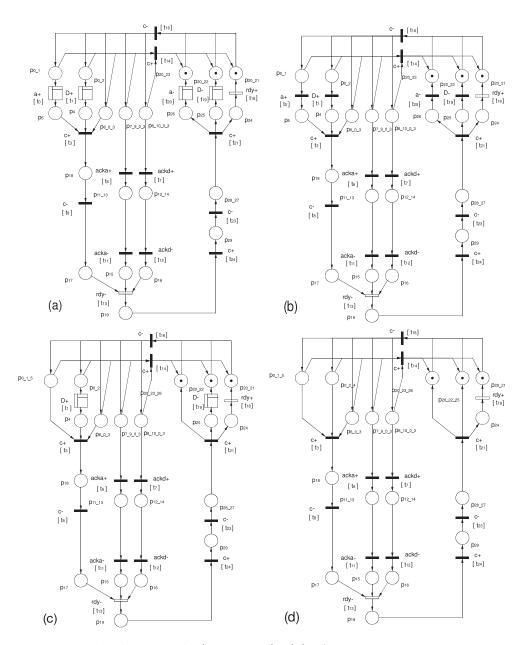

Figure 3.5. The globally irrelevant input a is not implemented in  $C_1$  and  $C_2$

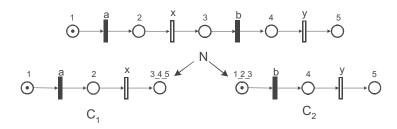

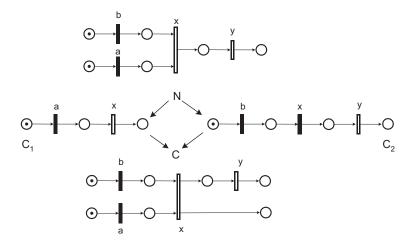

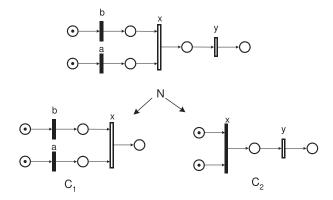

Fig. 3.5 shows a very simple example of an STG N and a decomposition into two components  $C_1$  and  $C_2$  that can be constructed by the [VW02] algorithm and have  $\mathcal{B} = \{(1, (1\_2, 1\_2\_3)), (2, (1\_2, 1\_2\_3)), (3, (3, 1\_2\_3)), (4, (4\_5, 4)), (5, (4\_5, 5))\}$  – here a marking of N or a component is identified with its single marked place; the marking of C is denoted by the marking of the components  $(M_1, M_2)$ .