## Formal Verification of Firmware-Based System-on-Chip Modules

## Formale Verifikation von firmwarebasierten System-on-Chip-Modulen

Vom Fachbereich Elektrotechnik und Informationstechnik der Technischen Universität Kaiserslautern zur Verleihung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) genehmigte Dissertation

> von M.Sc. Carlos Villarraga geboren in Ibague, Kolumbien

### D 386

Dekan: Vorsitzender der Prüfungskommission: Gutachter: Prof. Dr.-Ing. Hans D. Schotten

Prof. Dr. Gerhard Fohler Prof. Dr.-Ing. Dr. rer. nat. Wolfgang Kunz Prof. Dr. Rolf Drechsler

Tag der Einreichung: Tag der Disputation: 26. Oktober 20167. Dezember 2016

## Abstract

In current practices of system-on-chip (SoC) design a trend can be observed to integrate more and more low-level software components into the system hardware at different levels of granularity. The implementation of important control functions and communication structures is frequently shifted from the SoC's hardware into its firmware. As a result, the tight coupling of hardware and software at a low level of granularity raises substantial verification challenges since the conventional practice of verifying hardware and software independently is no longer sufficient. This calls for new methods for verification based on a joint analysis of hardware and software.

This thesis proposes hardware-dependent models of low-level software for performing formal verification. The proposed models are conceived to represent the software integrated with its hardware environment according to the current SoC design practices. Two hard-ware/software integration scenarios are addressed in this thesis, namely, speed-independent communication of the processor with its hardware periphery and cycle-accurate integration of firmware into an SoC module. For speed-independent hardware/software is proposed and an evaluated. For the case of cycle-accurate hardware/software integration, a model for hardware/software co-verification has been developed and experimentally evaluated by applying it to property checking.

## Acknowledgments

This thesis is the result of several years of intense and interesting research at the Electronic Design Automation group at the University of Kaiserslautern. Different persons have contributed to this work and I would like to thank them.

Firstly, I would like to express my sincere gratitude to Prof. Wolfgang Kunz for giving me the great opportunity to conduct this research under his supervision. I am truly indebted to him for his unflagging support and guidance during my research. I would also like to specially thank Prof. Dominik Stoffel for the valuable discussions and his guidance during the entire period of this research.

Many thanks to Prof. Rolf Drechsler for his interest in reviewing my thesis as well as for the important and helpful feedback. I also thank Prof. Gerhard Fohler for chairing my thesis committee.

I am very thankful to the German Academic Exchange Service (DAAD) for supporting and funding the first 3 and a half years of this research.

Special thanks go to Dr. Jörg Bormann for his collaboration and essential input at the beginning of my research.

Next, I would like to thank my colleagues Sacha Loitz, Binghao Bao, Oliver Marx and Christian Bartsch for the interesting discussions and fruitful collaborations. I am especially grateful with Bernard Schmidt, with who I closely worked while doing this research. The ideas of this thesis have been enriched during the nice and valuable discussions we had. I would like to thank Max Thalmaier for the time he spent proof-reading this thesis as well as Oliver Marx for helping me with the German summary.

Finally, I would like to thank Carmen Vicente-Fess, Matthias Legrom and Andreas Christmann for the good and kind support.

To my family

# Contents

| Abstract |                 |                                              |    |  |  |

|----------|-----------------|----------------------------------------------|----|--|--|

| Ac       | Acknowledgments |                                              |    |  |  |

| 1        | Intr            | oduction                                     | 1  |  |  |

|          | 1.1             | Firmware Integration in SoC Designs          | 2  |  |  |

|          |                 | 1.1.1 Speed-Independent Integration Scenario | 3  |  |  |

|          |                 | 1.1.2 Cycle-Accurate Integration Scenario    | 3  |  |  |

|          | 1.2             | State of the Art in SoC Formal Verification  | 4  |  |  |

|          |                 | 1.2.1 Formal Hardware Verification           | 6  |  |  |

|          |                 | 1.2.2 Formal Software Verification           | 8  |  |  |

|          | 1.3             | Motivation and Thesis Overview               | 10 |  |  |

|          | 1.4             | Publication List                             | 12 |  |  |

| 2        | Bacl            | kground                                      | 15 |  |  |

|          | 2.1             | The Boolean Satisfiability Problem           | 15 |  |  |

|          |                 | 2.1.1 The Satisfiability Problem             | 15 |  |  |

|          |                 | 2.1.2 SAT Solvers                            | 16 |  |  |

|          |                 | 2.1.3 Converting Circuits into CNF           | 19 |  |  |

|          | 2.2             | Verification Based on Bounded Models         | 19 |  |  |

|          | 2.3             | Symbolic Execution                           | 21 |  |  |

| 3        | Prog            | gram Netlists                                | 25 |  |  |

|          | 3.1             | Basic Idea                                   | 27 |  |  |

|          | 3.2             | Instruction Cells                            | 28 |  |  |

|          | 3.3             | Model Generation                             | 29 |  |  |

|          | 3.4             | Modeling Data Memory and Input/Output        | 31 |  |  |

|          | 3.5             | Modeling Interrupt-Driven Systems            | 34 |  |  |

#### Contents

| 4 | Effic                                         | cient Generation of Program Netlists                                                         | 35               |  |  |  |  |

|---|-----------------------------------------------|----------------------------------------------------------------------------------------------|------------------|--|--|--|--|

|   | 4.1                                           | Model Generation Using Incomplete CFGs                                                       | 36               |  |  |  |  |

|   | 4.2                                           | Computing Addresses Using SAT Techniques                                                     | 39               |  |  |  |  |

|   | 4.3                                           | Constant Propagation Using Instruction Set Simulation Techniques                             | 39               |  |  |  |  |

|   |                                               | 4.3.1 Simulating Undetermined Data and Control Flow                                          | 41               |  |  |  |  |

|   |                                               | 4.3.2 Computing Successors of Control Flow Instructions                                      | 41               |  |  |  |  |

|   | 4.4                                           | Tool                                                                                         | 42               |  |  |  |  |

|   | 4.5                                           | Experimental Results                                                                         | 44               |  |  |  |  |

| 5 | Equivalence Checking of HW-Dependent Software |                                                                                              |                  |  |  |  |  |

|   | 5.1                                           | Sequence-Based Input/Output Model of Low-Level Software                                      | 49               |  |  |  |  |

|   |                                               | 5.1.1 Abstract Time Modeling of Input/Output Software Operations                             | 51               |  |  |  |  |

|   |                                               | 5.1.2 Logic for Modeling Input/Output Sequences                                              | 53               |  |  |  |  |

|   | 5.2                                           | Software Miter                                                                               | 58               |  |  |  |  |

|   | 5.3                                           | Equivalence Checking Using SAT                                                               | 59               |  |  |  |  |

|   | 5.4                                           | Tool                                                                                         | 60               |  |  |  |  |

|   | 5.5                                           | Experimental Results                                                                         | 62               |  |  |  |  |

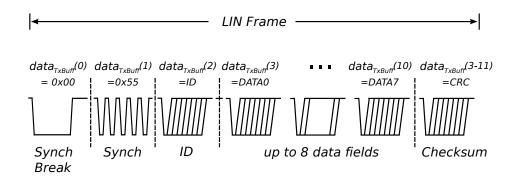

|   |                                               | 5.5.1 LIN Driver                                                                             | 62               |  |  |  |  |

|   |                                               | 5.5.2 Serial Synchronous Interface                                                           | 63               |  |  |  |  |

| 6 | Creat                                         |                                                                                              | 65               |  |  |  |  |

| 0 | 6.1                                           | le-Accurate HW/SW Co-Verification of Firmware-Based Designs<br>Joint Hardware/Firmware Model | <b>0</b> 5<br>67 |  |  |  |  |

|   | 6.2                                           | Timed Interface Model                                                                        | 69               |  |  |  |  |

|   | 0.2                                           | 6.2.1 Timed Interface Cells                                                                  | 69               |  |  |  |  |

|   |                                               |                                                                                              | 09<br>71         |  |  |  |  |

|   |                                               | 5                                                                                            |                  |  |  |  |  |

|   | ()                                            | 6.2.3 Timing of Software Input/Output Operations                                             | 74               |  |  |  |  |

|   | 6.3                                           |                                                                                              | 82               |  |  |  |  |

|   | 6.4                                           | Experimental Results                                                                         | 82               |  |  |  |  |

| 7 |                                               | mary and Future Work                                                                         | 87               |  |  |  |  |

|   | 7.1                                           | Summary                                                                                      | 87               |  |  |  |  |

|   | 7.2                                           | Future Work                                                                                  | 89               |  |  |  |  |

|   |                                               | 7.2.1 Perspectives in Formal Verification                                                    | 89               |  |  |  |  |

|   |                                               | 7.2.2 Perspectives in Test and Safety                                                        | 90               |  |  |  |  |

| 8 | Deu                                           | tsche Zusammenfassung                                                                        | 93               |  |  |  |  |

|   | 8.1                                           | Programmnetzliste                                                                            | 93               |  |  |  |  |

|   | 8.2                                           | Äquivalenzvergleich von hardwareabhängiger                                                   |                  |  |  |  |  |

|   |                                               | Software                                                                                     | 96               |  |  |  |  |

| 8.              | .3   | Zyklengenaue Hardware/Software            |     |  |  |  |

|-----------------|------|-------------------------------------------|-----|--|--|--|

|                 |      | Co-Verifikation                           | 97  |  |  |  |

| A P             | reli | minaries                                  | 99  |  |  |  |

| А               | .1   | Mathematical Background                   | 99  |  |  |  |

|                 |      | A.1.1 Sets                                | 99  |  |  |  |

|                 |      | A.1.2 Relations, Functions, and Sequences | 100 |  |  |  |

|                 |      | A.1.3 Graphs                              | 100 |  |  |  |

| А               | 2    | Graph Algorithms                          | 101 |  |  |  |

|                 |      | A.2.1 Breadth-First Search                | 101 |  |  |  |

|                 |      | A.2.2 Depth-First Search                  | 102 |  |  |  |

|                 |      | A.2.3 Topological Sorting                 | 103 |  |  |  |

| А               | 3    | Boolean Functions                         | 104 |  |  |  |

|                 |      | A.3.1 Characteristic Functions            | 105 |  |  |  |

| List of Figures |      |                                           |     |  |  |  |

| List of Tables  |      |                                           |     |  |  |  |

| Bibliography    |      |                                           |     |  |  |  |

Contents

# Chapter 1

## Introduction

*Embedded systems* play today an integral role in nearly every aspect of modern life. They are employed in safety-critical products such as medical devices, vehicles, and airplanes, in manufacturing and security systems, as well as in consumer products such as mobile devices and home appliances. Thanks to the advances in semiconductor industry, embedded systems are commonly implemented by means of *system-on-a-chips* (SoCs). An SoC integrates into a single chip different *intellectual property* (IP) cores like processors, memories, communication buses, and communication interfaces.

Continuous development of embedded systems technology is driven by the intense product competition in system features and capabilities caused by a more and more demanding society. To be competitive, new designs must exhibit increases in functionality, performance, and reliability and declines in features like power consumption and size. As a result of this and supported by the advances in silicon technology, an increasing number of IP cores can be integrated into a single SoC. Likewise, the subsystems inside an SoC are becoming more and more complex. In many cases, a single IP block can by itself be considered as an embedded system. Current microprocessors, for instance, integrate apart form processor cores: caches, memory controllers, and communication interfaces [BC11].

Besides the use of high-integrated silicon systems, shrinking time-to-market windows of the highly competitive global electronics market places additional pressure on design teams. Increasingly complex systems need to be developed in decreasing amounts of time. In response to this, different design strategies continuously emerge that allow designers to tackle the challenges in SoC markets. In particular, in recent years the programmability of SoCs has continuously grown. Because of its inherent flexibility and reconfigurability, software offers an attractive solution to SoC developers.

Software-based solutions allow also to obtain products that exhibit increased functionality to the users. Because of this fact, in automotive and aerospace industries, for example, mechanical systems get continuously replaced or combined with electric and software-based components. As a result of this, the number of software-implemented control units in cars

and airplanes keeps growing across the new generations of models.

These trends do not only allow for creating application embedded software with growing complexity, but also increase the complexity of software at lower design levels [EJ09].

On the one side, the firmware in embedded systems becomes more complex in order to manage the increasing number of integrated units in an embedded system. Furthermore, the growing functionality of these units contributes to the complexity increase. For instance, complex device drivers are required to control and communicate with highly configurable hardware peripherals available in current SoC architectures.

On the other side, changes in design practices for SoCs at lower design levels contribute also to the increased programmability of embedded systems. Different chip-wide control functions of an SoC are no longer implemented in register-transfer level (RTL) hardware, but as firmware running on service processors that are instantiated particularly for this purpose [ZES13, WPL<sup>+</sup>12, CJ09]. Among others, control functions include chip (or system) initialization, power management, and the control of infrastructures for test and system diagnosis. Similarly, implementation of communication structures is shifted more and more from hardware to the low-level software of the system. As an advantage, a firmware-based design of these functions permits quick product updates and late engineering changes to the designs because firmware is much easier to change than RTL hardware.

These trends have created new interest in techniques for formal firmware verification, not only among software developers but also in the hardware design community [KG14, Gru13, WCGP12, Kro07]. Because of the tight coupling between firmware and hardware, verification techniques as they have been developed for application-level software are not always appropriate. Techniques are required that help to analyze the mutual effects of hardware and firmware on each other.

Motivated by these observations, this thesis tackles the problem of performing formal firmware verification by following a combined hardware/software analysis. The next section of this introduction presents integration scenarios of firmware and hardware in current architectures for embedded systems. Then, Section 1.2 gives an overview of currently reported techniques for formal SoC verification. Finally, Section 1.3 presents the motivation of this thesis and summarizes the main contributions of it.

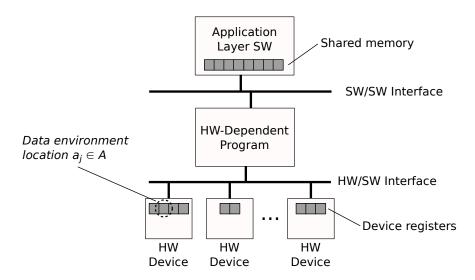

## **1.1** Firmware Integration in SoC Designs

In the context of this thesis the term *firmware* is employed to refer to the part of the software in an embedded system that directly interacts with the system's hardware. Because of this fact, firmware will also be referred to as *hardware-dependent* software in the sequel without extra notice.

Firmware interacts closely with its hardware environment and the timing behavior of hardware/software interactions depend on how firmware and hardware are integrated into the

system. In the following, two main firmware integration scenarios present in modern SoCs are described.

#### **1.1.1 Speed-Independent Integration Scenario**

The first scenario is found in traditional SoC design flows. Processor cores are integrated into the hardware system as components of a CPU bus. They usually communicate with the rest of the system in a *speed-independent* way using some bus protocol with handshake mechanisms in order to accommodate for different access latencies. There exists a number of standard buses (cf. [ARM99,IBM99]) that can be instantiated in the design so that processors can be easily integrated with different IP cores in an SoC.

Speed-independent communication is key since the execution time in pipelined processors, especially when advanced architectures based on out-of-order execution are employed, is difficult to predict. Similarly, caches have a difficult-to-predict timing behavior and provide another reason for speed-independent bus communication.

In this scenario, a fine-grained timing analysis of the software is not performed. Instead of that, techniques for worst-case-execution-time (WCET) analysis [WEE<sup>+</sup>08] are employed to ensure that the software, executed on its hardware platform, responds in the correct time limits.

#### 1.1.2 Cycle-Accurate Integration Scenario

Besides conventional design styles where firmware and hardware are integrated by employing CPU buses, there are also new design approaches for which a clock *cycle-accurate* analysis is required. This introduces a second scenario which is described in the following.

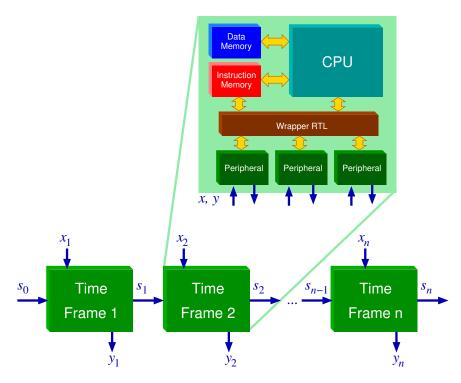

When designing SoCs it has become increasingly popular to replace dedicated RTL hardware components by a firmware-based design [ZES13, WPL<sup>+</sup>12, CJ09]. For this purpose, service processors in addition to the main processor are instantiated, implementing the sub-functions that were formerly performed by the hardware component. Commonly employed processors have a timing behavior that is fully predictable. For example, processors in the style of the Intel 8051 or the Xilinx PicoBlaze are popular in ASIC-based and FPGA-based design flows, respectively.

The firmware executed on its hardware platform implements a finite-state machine (FSM) that conceptionally behaves just like a pure RTL hardware design. However, the implemented control structure is not fixed in hardwired state transitions, but is embodied in firmware executed by the processor. Control-flow decisions occur in branch instructions and references to the hardware are explicit in load and store operations. The control of the surrounding hardware is not done in a speed-independent way but performed cycle-by-cycle by transactions generated by the firmware. This firmware-based design approach offers

advantages:

- 1. The design time is reduced and product updates can be made more easily by making changes in the firmware.

- 2. Especially for FPGAs, due to a well-optimized design of the processor, the resulting implementation may need less chip area when compared to a conventional implementation with standard RTL hardware.

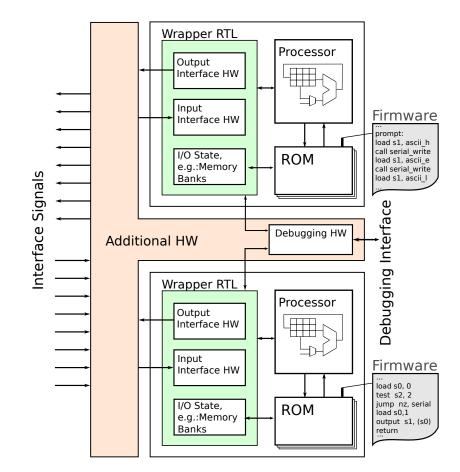

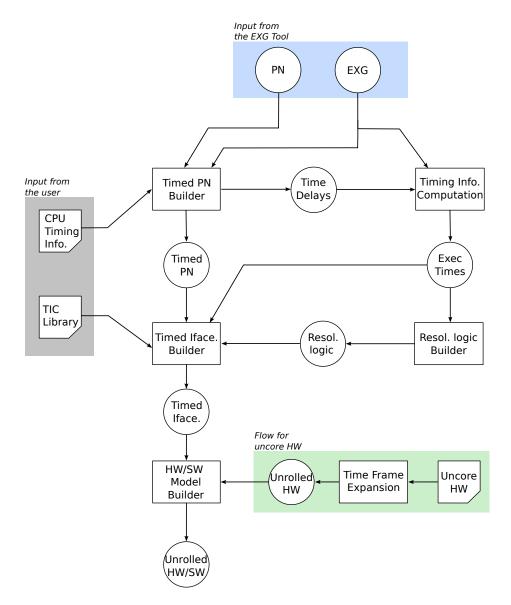

The software running on the instantiated cores is usually not meant to be visible to the users. It is provided as firmware with the design and may be loaded into a read-only memory. In many cases, the cores are not directly connected to the rest of the system using (standardized) communication interfaces like SoC buses but instead are embedded into the surrounding system using special interface hardware, sometimes called "wrapper RTL" [Xil11a, WCGP12]. Such design styles allow for a tight integration delivering high performance because the exact timing of the processor hardware and its software is known at design time. A firmware-based SoC module designed in this way is shown in Figure 1.1. The module consists of two processor cores tightly integrated with their firmware, wrapper RTL, and some additional hardware.

### **1.2** State of the Art in SoC Formal Verification

This thesis does not intend to extend the basic proving methodology for formal verification. It mainly leverages the state of the art in this field and focuses on how to integrate low-level software components (firmware) into the computational procedures needed for a combined hardware/software verification. Therefore, computational models and algorithms for low-level hardware-dependent software verification are in the particular interest of this thesis.

Formal methods for hardware verification and for software verification have been active research fields for decades. In the following overview, the focus is kept on (1) those techniques that help to the development of the intended research and on (2) those contributions that are related to the topics of this thesis.

First of all, this thesis is based only on fully automated proof techniques which have been successfully adopted and extended by the Electronic Design Automation (EDA) industry over the last decades. This precludes the use of sophisticated methodologies based on higher-order logic and theorem proving [Har09]. In spite of advances in automation of the proofs, these methodologies still require highly skilled verification engineers that guide the verification process interactively. This added manual effort makes less attractive the practical adoption of such methodologies.

Formal verification methods in general employ mathematical models for describing the *design under verification* (DUV) and the proof goal (the specification). From this description

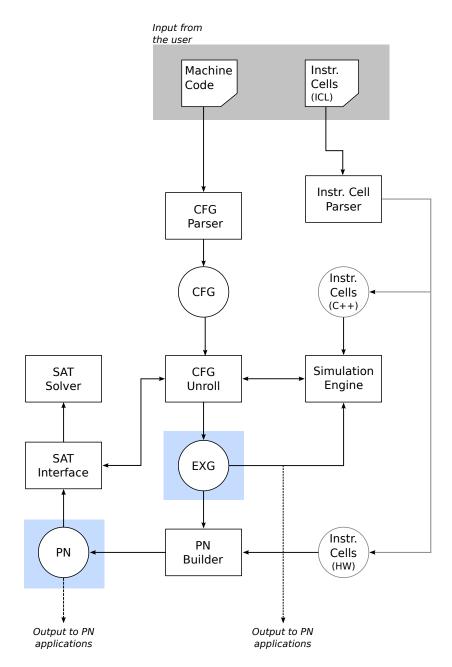

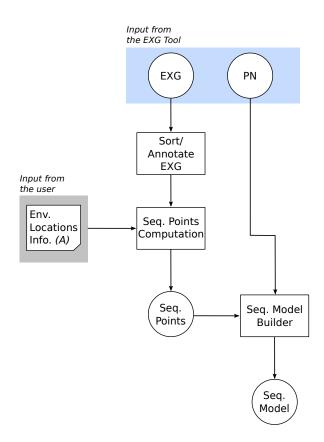

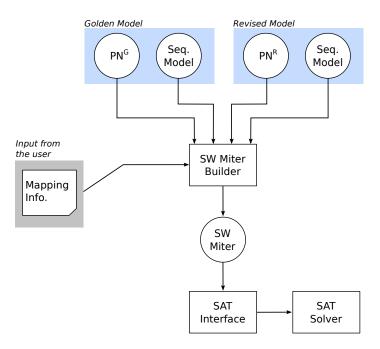

Figure 1.1: Firmware-based IP core

then a formal checker exhaustively inspects whether the proof goal holds or not for all possible input assignments. If the proof does not hold, then a counterexample (e.g., an input assignment for which the proof goal does not hold) is extracted and provided to the user so that the cause of the failure can be derived from it.

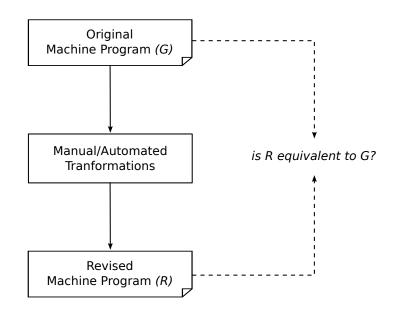

There are two main practical applications of formal verification methods, namely *property checking* and *equivalence checking*. In property checking, the DUV is proven to determine whether it complies with the intended behavior or not. So-called *properties* are used in the verification process to formalize the design specification. For its part, equivalence checking is used to prove whether two designs are functionally equivalent or not. The rest of this section gives more details on current reported formal verification techniques by property and equivalence checking for both hardware and software.

#### **1.2.1** Formal Hardware Verification

A possible classification of formal property checking techniques employed for hardware is to distinguish between a *bounded* and an *unbounded* paradigm. In the unbounded paradigm, techniques reason about behaviors of the system over infinite lengths of time. This paradigm is rooted in classical model checking [CE81] based on temporal logics. Numerous extensions to the basic scheme have been proposed to increase its computational power. Based on Binary Decisions Diagrams (BDDs) [Bry86], symbolic methods have been developed to traverse the state space [McM93, CBM89]. The state explosion problem is one of the biggest challenges in this area and is often addressed by automatic abstraction techniques such as [CGJ+03, GS97, JKSC05] that over-approximate the state space. This is related to the problem of finding invariants to identify appropriate state space approximations, e.g., [CHM<sup>+</sup>96, CNQ04]. Compositional techniques such as [CLM89] have been developed to handle large designs in a divide-and-conquer strategy.

In the bounded paradigm, always a *finite time interval* is considered when formulating a property to describe a piece of design behavior. Bounded Model Checking (BMC) [BCCZ99] and Interval Property Checking (IPC) [NTW<sup>+</sup>08] are representatives of this paradigm and have in common that the underlying computational model is obtained by unrolling finite state machines for a finite number of steps into an entirely combinational circuit model. This allows for mapping the property checking problem to the Boolean satisfiability problem (SAT) [BHvMW09]. Thereby, verification based on bounded models has benefited from the significant advances in SAT solving technology in the last decades [JLBRS12, KSMS11].

K-step induction [SSS00] can be used to extend verification based on bounded models for proving safety properties also over unbounded time windows. More recent research also explores property checking based on SAT with interpolants [McM03] and property directed techniques [Bra11] to efficiently capture adequate information about the state space. Also, in the bounded paradigm, invariants can play a key role in obtaining general proofs for relevant parts of the system behavior, e.g., [BC00, TNW<sup>+</sup>10]. The restrictions resulting from the bounded nature of the computational model have motivated sophisticated methodologies, such as [Cla07, BBM<sup>+</sup>07], to obtain a global correctness proof for the system.

While the unbounded paradigm is usually adequate to handle systems with no more than a few hundred state variables, the bounded approach is often successfully applied to designs with thousands of state variables. This makes it particularly attractive for industrial use. Current solutions have been able for instance to replace simulation of large hardware modules in industry [KGN<sup>+</sup>09].

Most of these techniques and their numerous extensions are tailored to be applied to pure hardware descriptions, i.e., they operate on Boolean networks and conventional finite state machine descriptions which are then converted into the required computational models such as those based on Kripke structures [Kri63]. Rooted in classical temporal logics such as CTL [CE81] and LTL [Pnu77], standardized property specification languages for hardware are available such as SystemVerilog Assertions (SVA) [Spe08] and Property Specification Language (PSL) [Acc04].

Equivalence Checking on its part has been widely adopted in industry and has completely replaced logic simulation at the gate level in modern SoC design flows. This success is based on two main facts:

First, design transformations performed by RTL synthesis tools normally preserve the state encoding of the implemented sequential circuit. This allows to reduce the general sequential equivalence problem to a pure combinational one. In practice, the problem is solved using a computational model called *miter* [Bra93] containing: the logic for the reference (golden) and the implemented (revised) circuits, mappings for the primary inputs and outputs as well as mappings between the latches of the designs [vEJ95]. As a result, no space traversals are required and therefore the required proofs become much easier.

Second, synthesis tools perform only local changes to the reference design. Hence, the main structure between the circuits being compared is kept. Equivalence checkers leverage this fact by identifying and pruning out internal equivalences (cut points) from the compared circuits [KK97, JMF95, Kun93].

Besides this, current solvers integrate several engines such as BDDs, SAT solvers, and Automatic Test Pattern Generation (ATPG) to achieve increased proof capabilities.

Due to these facts, current equivalence checkers scale up to verification of the whole SoC RTL hardware. For problems where changes in the state encoding are performed, the works of [vE00, SWWK04] have adapted the combinational approach achieving, to some extent, similar benefits.

#### **1.2.2 Formal Software Verification**

There is a large research body on methods for formal software verification. In the following, formal software verification techniques are classified into *hardware-independent* and *hardware-dependent* approaches. Although this thesis is focused on a hardware-dependent software view, methods also from hardware-independent techniques are useful and therefore are covered by this overview.

In hardware-independent software models, the software is often described by "simple programs" (cf. [JM09]) as some kind of (finite) state transition system that is processed by model checking and related techniques. Programs are typically given in high-level languages like C. Also here it is possible to distinguish between methods adopting an unbounded paradigm [BPR01, BHJM07, God05, HP00, Hol97] and a bounded paradigm [BH08, IYG<sup>+</sup>04, CKY03]. Differences between tools and methods result from the underlying proof methods (enumerative (stateful, stateless), symbolic) and the employed abstraction techniques (iterative abstraction-refinement based on localization reduction and/or predicate abstraction).

In [BPR01, BHJM07] properties of C programs are verified by performing a systematic predicate abstraction [CGJ<sup>+</sup>03] of the software. While performing a given proof, the abstraction gets refined until a valid answer is returned by the verification algorithm. Unbounded model checking is employed in these approaches for traversing the state space of the resulting finite-state model.

The tools of [IYG<sup>+</sup>04] and [CKY03] perform bounded model checking of C programs. In [IYG<sup>+</sup>04], the transition relation of a C program is obtained by performing optimizations such as basic-block extraction, one-hot encoding of program locations, and bit-width reductions by static range analysis. The obtained transition system is then syntactically unrolled following the approach of [BCCZ99]. Additionally, control flow information is provided to the SAT engine in order to improve scalability of the method. In [CKY03] a different approach is taken that unrolls the C program by unwinding its control flow graph. This combines benefits of conventional BMC with path-oriented techniques employed in symbolic execution.

*Symbolic execution* is a technique widely used for software verification and testing [Kin76]. Good overviews of this technique are given in [PV09] and [CS13]. Symbolic execution traces symbolically the individual execution paths of a program to explore the program behavior. With the goal of avoiding path explosion, techniques have been developed to prune as well as to merge execution paths. In the context of software testing, current approaches combine symbolic and concrete executions in order to obtain test suites with increased coverage [GKS05, CGP<sup>+</sup>06]. Also, different traversal algorithms have been proposed for improving path coverage [GKS05, SMA05].

In this thesis, some ideas from symbolic execution are borrowed to develop a computational model for software that can be integrated as a component into a hardware description. When examining the impact of software on the concrete hardware, as is required in firmware designs, the software must be examined at a hardware-dependent level. Literature on hardware-dependent low-level software verification and formal hardware/software co-verification is much sparser than the literature for hardware-independent software.

Previous work on low-level software verification includes [Sch10] which employs explicit unbounded model checking algorithms in order check assembly code against properties specified with computation tree logic.

Different approaches based on symbolic execution have been also proposed. The work of [CFF<sup>+</sup>06] performs equivalence checking of digital signal processing algorithms by employing symbolic execution together with SMT solving (using the theory of uninterpreted functions with equality). Similarly, in [AEF<sup>+</sup>05, AEO<sup>+</sup>08] symbolic execution has been successfully employed to perform microcode verification. In these approaches, due to the explicit enumeration of the individual program paths, as pointed out in [AEF+05], analyzing the reactive behavior of low-level embedded software with its hardware periphery becomes very complex. Unlike in many cases of hardware-independent verification, the analysis can no longer be localized to an individual path but the contribution of all possible execution paths must be considered simultaneously. This typically leads to restrictions on the hardware/software interfaces that can be modeled. The work of [CFF<sup>+</sup>06], for instance, restricts the formulation of comparing two assembly programs to programs with very similar control flow graphs (CFGs) that can communicate with the environment only at the beginning and at the end of the execution.  $[AEF^+05]$  restricts to programs that communicate with the environment only at specific exit points (no intermediate interactions with the environment are handled by the approach).

The tool of [CEP00] assumes the manual creation or the availability of an abstract automaton or petri-net model for hardware and software components. These models are disconnected from the actual implementation so that a significant amount of additional efforts would be needed to use such an approach in a standard design flow for firmware designs employing either ASICs or FPGAs.

In [HTV<sup>+</sup>13] it is proposed to model the combined hardware/software system in terms of C programs. The approach is based on manually extracting models for the hardware from virtual prototypes in C. This level of abstraction is appropriate for performing early verification of hardware/software systems during design exploration. However, for verifying the impact of the software on concrete implementations of hardware/software designs, the modeling task needs to be performed at a different level of abstraction. Otherwise, lifting such high-level models from the design would again require significant additional efforts for the verification.

[GKD06] and [EES04] are based on unrolling the programs by representing each program step as an instance of the processor's (RTL) hardware. These approaches allow for a tightly coupled view on both the hardware and the software, but lead to highly complex models that only allow for local examinations of the combined system behavior. In order to improve scalability, specific abstraction mechanisms have been proposed in [NWSK11]. However, a main drawback of the latest approach is that the required abstractions need to be provided by the verification engineer for each analyzed program.

In conclusion, there is a large number of formal techniques tailored for verification tasks in the hardware and in the software domain. Many of the basic algorithmic concepts reported in previous work have the potential to contribute to a verification environment for firmware designs in SoCs. However, there is a substantial lack of adequate models and compositional techniques that allow for a joint analysis of the hardware and software components at the appropriate levels of abstraction.

### **1.3** Motivation and Thesis Overview

Traditional techniques for formal software verification usually adopt a hardware-independent view when verifying software programs written in high-level languages such as C. This is reasonable for a wide range of applications where the main objective is to identify bugs that are specific to the software development process. However, in embedded system design, as a result of the trends described above, it is important to analyze the mutual effects of hardware and software on each other. Therefore, a hardware-dependent software view is needed where the behavior of the firmware is precisely described in terms of its effect on the underlying hardware.

In this thesis, the software is modeled by using program netlists. A program netlist (PN) is a combinational model that compactly represents the behavior of a low-level embedded program in terms of the hardware on which it executes. Following a path-oriented modeling approach, in a program netlist the software behavior is represented along execution paths. More specifically, the program's computation is implicitly represented in a compact and hardware-dependent way for all paths of execution. This is opposed to symbolic execution where the expressions for the state variables and the path conditions are explicitly generated for every simulated path. Like symbolic execution, the approach using program netlists is also based on the enumeration of execution paths. However, this is shifted to a preprocessing phase that neglects all of the program's computation that is not relevant to its control flow. No formulas representing the computation along the paths are generated. Instead, a program netlist includes additional logic which not only simplifies the model but also makes relevant control flow information explicit to the decision procedure (e.g., a SAT solver). This facilitates the reasoning on the model. When solving the actual verification task on the program netlist, the "intelligence" of a SAT solver is used to exploit the additional elements of the computational model to traverse the execution paths with their associated hardware-represented computation in an efficient way.

Chapter 3 details on the characteristics of the program netlist model and on its generation process. This includes modeling aspects such as efficient representation of the data traffic between software and data memory as well as the traffic between software and the surrounding environment. The developments presented in this chapter have been conducted jointly with the dissertation work of Dipl.-Ing. Bernard Schmidt.

Subsequently, in Chapter 4, it is presented how generation of program netlists can be efficiently implemented so that the method scales for practical designs. For that, simulation techniques are mixed with formal SAT-based analyses for finding reachability information of the firmware's control flow as well as for computing the set of memory addresses that are accessed by the software. This information turns out to be crucial for performing simplifications not only in the program netlist, but also in models derived from it.

One important characteristic of the program netlist is that it can be instantiated and combined with other models in order to solve different verification problems. Taking advantage of that, this thesis proposes how formal verification of firmware designs can be performed for the hardware/software integration scenarios described in Section 1.1.

In Chapter 5 an approach for formal verification by equivalence checking for speedindependent integration scenarios (cf. Section 1.1.1) is proposed. For this scenario, assuming the correct implementation of the CPU bus protocol (as can be verified by standard techniques of formal hardware verification [NTW<sup>+</sup>08]), it is possible to model the software in a timeabstract way. This is exploited in the program netlists of Chapter 3 by creating time-abstract descriptions. In this way, even for complex processor architectures compact models can be obtained.

It is important to note that even though the concrete timing, in terms of HW clock cycles, is abstracted away from the program netlist, the original ordering of the instructions during execution is preserved in the model. This characteristic of the program netlist is particularly important when analyzing the hardware/software interface of reactive programs. Reactive software communicates with the environment continuously at distinct time points and the ordering in which the exchange of information takes place is crucial for the functional correctness of the system behavior. For example, for the case of equivalence checking, as will be shown in Chapter 5, it needs to be proven that two different programs interact in the same way with the environment. Therefore, verification needs to consider not only the data values exchanged with the environment but also the ordering of the data exchange.

Apart from equivalence checking, also property checking for time-abstract scenarios using program netlists has been researched in [SVF<sup>+</sup>13b].

For firmware-based design approaches for which a clock cycle-accurate analysis is required (cf. Section 1.1.2) extensions to the program netlist are presented in Chapter 6 in order to perform verification by property checking.

For firmware-based design styles, verification is important because the hardware/software interface is usually custom-designed and, thus, error-prone. As pointed out in [WCGP12],

traditional verification approaches based on instruction set hardware/software co-simulation would never fully capture the entire hardware and firmware system behavior in one tool environment. Verifying the firmware in isolation, while possible, would require a hardware bus-functional model interface. This makes the simulation of such firmware-based IPs complicated and creates the need for an additional behavioral test bench [WCGP12]. Similarly, also a formal approach that verifies hardware and software in separation would require the tedious task of modeling the interface between them by a set of constraints.

Therefore, this thesis proposes a formal co-verification approach instead. The program netlists of Chapter 3 are very attractive for this purpose because they can be generated completely automatically. On the other hand, due to their abstract, non-cycle-accurate nature, they cannot be directly integrated into the RTL descriptions of the hardware and they do not allow for a cycle-accurate analysis. In Chapter 6, therefore extensions are presented to make program netlists cycle-accurate and show how to create a joint model for formal co-verification of hardware and firmware by property checking. The developments presented in Section 6.2.3 have been conducted jointly with the dissertation work of M.Sc. Michael Schwarz.

Chapter 2 details the techniques on which this research is based. Notations and basic definitions are given in Appendix A. Chapter 7 concludes this thesis summarizing the proposed approaches and the results obtained as well as describing the future uses of the computational models presented in this work.

## **1.4 Publication List**

Large parts of this thesis have been already published in the publications listed chronologically below:

- Bernard Schmidt, Carlos Villarraga, Jörg Bormann, Dominik Stoffel, Markus Wedler, and Wolfgang Kunz. A computational model for SAT-based verification of hardwaredependent low-level embedded system software. In *Proceedings of the 18th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pages 711–716, 2013

- Bernard Schmidt, Carlos Villarraga, Thomas Fehmel, Jörg Bormann, Markus Wedler, Minh Nguyen, Dominik Stoffel, and Wolfgang Kunz. A new formal verification approach for hardware-dependent embedded system software. *IPSJ Transactions on System LSI Design Methodology (Special Issue on ASPDAC-2013)*, 6:135–145, 2013

- Carlos Villarraga, Bernard Schmidt, Christian Bartsch, Jörg Bormann, Dominik Stoffel, and Wolfgang Kunz. An equivalence checker for hardware-dependent software. In 11. ACM-IEEE International Conference on Formal Methods and Models for Codesign (MEMOCODE), pages 119–128, 2013

- Christian Bartsch, Carlos Villarraga, Bernard Schmidt, Dominik Stoffel, and Wolfgang Kunz. Efficient SAT/simulation-based model generation for low-level embedded software. In 17. GI/ITG/GMM Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV), pages 147–157, 2014

- 5. Carlos Villarraga, Bernard Schmidt, Binghao Bao, Rakesh Raman, Christian Bartsch, Thomas Fehmel, Dominik Stoffel, and Wolfgang Kunz. Software in a hardware view: New models for HW-dependent software in SoC verification and test (invited paper). In *Proc. International Test Conference (ITC'14)*, 2014

- Binghao Bao, Carlos Villarraga, Bernard Schmidt, Dominik Stoffel, and Wolfgang Kunz. A new property language for the specification of hardware-dependent embedded system software. In *Proc. Forum on Specification And Design Languages (FDL)*, Munich, Germany, Oct 2014. (accepted for publication)

- Binghao Bao, Carlos Villarraga, Bernard Schmidt, Dominik Stoffel, and Wolfgang Kunz. A new property language for the specification of hardware-dependent embedded system software. In Frank Oppenheimer and Julio Luis Medina Pasaje, editors, *Languages, Design Methods, and Tools for Electronic System Design*, volume 361 of *Lecture Notes in Electrical Engineering*, pages 83–100. Springer International Publishing, 2016

- 8. Carlos Villarraga, Dominik Stoffel, and Wolfgang Kunz. *Formal System Verification*, chapter Software in a Hardware View: New Models for HW-dependent Software in SoC Verification. Springer (to appear), 2016

- Christian Bartsch, Niko Rödel, Carlos Villarraga, Dominik Stoffel Stoffel, and Wolfgang Kunz. A HW-dependent software model for cross-layer fault analysis in embedded systems. In *17th Latin-American Test Symposium (LATS)*, pages 153–158, April 2016

- 10. Oliver Marx, Carlos Villarraga, Dominik Stoffel, and Wolfgang Kunz. A computeralgebraic approach to formal verification of data-centric low-level software. In 14. ACM-IEEE International Conference on Formal Methods and Models for Codesign (MEMOCODE) (to appear), 2016

Chapter 1. Introduction

## Chapter 2

## Background

This chapter gives a short introduction into different verification techniques and algorithms used in this thesis. It is not the goal of this introduction to be comprehensive, its purpose is to recall the most important concepts and terminologies so that the reading of the subsequent chapters becomes easier for the reader. For a comprehensive discussion, the reader will be provided, in each section of this chapter, with the corresponding literature.

For an introduction to basic mathematical definitions and notations used in this thesis the reader is referred to the Appendix A.

## 2.1 The Boolean Satisfiability Problem

Many problems in the field of electronic design automation can be mapped to the Boolean satisfiability problem (SAT). In this thesis, verification problems for property and equivalence checking are reduced to instances of the SAT problem. Therefore, this section introduces the SAT problem and summarizes how this problem is currently solved in practice by current techniques. For a deeper treatment, readers are recommended the following reference [BHvMW09].

#### 2.1.1 The Satisfiability Problem

Given a Boolean formula  $f(x_1, \ldots, x_n)$ , the Boolean satisfiability problem poses the following question: is there an assignment to the variables  $x_1, \ldots, x_n$  under which f evaluates to true?. If the answer is 'yes', f is said to be satisfiable and the involved variable assignment is called a satisfying assignment. If the answer is 'no', i.e., if no such assignment exists, f is said to be unsatisfiable.

Due to efficiency reasons, Boolean formulas are usually represented in conjunctive normal form (CNF) for solving the SAT problem. A CNF formula is satisfied under a given assignment if each of the individual clauses composing it are satisfied. Furthermore, a single

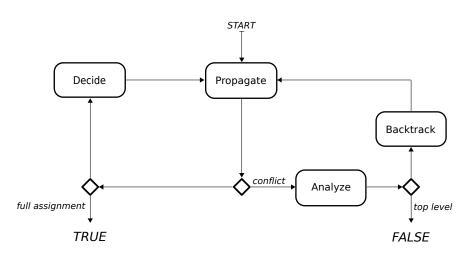

Figure 2.1: Basic structure of a conflict driven SAT solver

clause is satisfied if at least one of its literals evaluates to *true*. On the other hand, a CNF formula is unsatisfied under a given assignment if at least one of its clauses evaluates to *false*. A clause that evaluates to *false* is called a *violated* or a *conflicting* clause. A clause is violated if each of its literals evaluates to *false*.

If every clause of a CNF formula contains at maximum two literals, then the SAT problem can be solved in polynomial time [AB09]. However, for formulas not fulfilling this condition, as it happens with most real-life formulas, the SAT problem is NP-complete and therefore it can be solved in the worst-case in exponential time [Coo71]. Despite this fact, in the last couple of decades, there have been significant advances in developing efficient SAT solvers capable of solving large practical problems in reasonable amounts of time [JLBRS12].

#### 2.1.2 SAT Solvers

Modern SAT solvers work on the basis of the DPLL algorithm [DLL62, DP60]. Broadly speaking, for finding a satisfying assignment the DPLL algorithm assigns one by one the variables of a given CNF formula. Every time a variable gets assigned, the formula is updated by evaluating the logical implications of the assignment. If after an assignment all clauses are satisfied then the algorithm finishes returning *true*. However, if one or more clauses are violated then the algorithm corrects the bad assignment by backtracking. Backtracking moves back to the last assignment and reverts it. Since the algorithm moves back to the last assignment this kind of backtracking is referred to as *chronological backtracking*. After backtracking, the variable that has been wrongly assigned is assigned with the opposite truth value and the algorithm continues. If it happens that clauses are violated for both possible truth assignments then the algorithm backtracks again and repeats. The DPLL returns *false* in case that all variable assignments have been exhausted without success.

In the last decades, the basic DPLL algorithm has been improved to the point that current

SAT solvers are capable of solving problems having millions of variables in practical amounts of time [JLBRS12]. However, there are still problems for which modern SAT solvers run in exponential time. Typical cases are problems containing arithmetic units such as multipliers.

Figure 2.1 presents the core structure of a modern SAT solver. It is composed of one main loop with two branches inside it. The branch on the right is executed when conflicts are produced. On the other side, the left branch is executed when assignments cause no conflicts. Modern SAT solvers implement the engines *Propagate*, *Decide*, *Analyze* and *Backtrack* adopting a number of techniques which have become standard during the last decades. In [KSMS11] an experimental evaluation demonstrates the effectiveness of these techniques. In the following a brief description is given:

- Analyze performs a diagnosis of the reason for a conflict based on the variable assignment and the logical implications which activate the conflict [MSS99]. As a result of the diagnosis a so-called *conflict clause* is generated. A conflict clause represents a more concise variable assignment which also activates the conflict. [ES03b] performs further improvements by eliminating redundant literals from the conflict clause. Conflict clauses are added to the CNF formula by *Analyze*. Adding conflict clauses to the CNF is referred to as *learning*. Learning prevents the solver of repeating wrong assignments. In practice, learning has shown to increase importantly the performance of the solver [KSMS11]. Furthermore, from a conflict clause it can be also derived the level to which the solver needs to backtrack. If the backtracking level corresponds to the so-called *top level*, the solver finishes returning *false*.

- *Decide* is responsible for selecting and assigning variables. This process is critical for the performance of a solver [KSMS11]. In [MMZ<sup>+</sup>01] a selection heuristic based on literal activities is proposed. This strategy favors selection and assignment of literals which try to satisfy first clauses related to the most recent conflicts. Low computational overhead is added to the solver since only literals related to current conflict clauses need to be updated. In [ES03b] overhead is further reduced by associating activities to variables. A possible problem with this approach is that the solver can get stuck in deep search regions without a solution. Techniques based on restarts have been proposed in [Bie08, ES03b] to counter effectively this problem.

- *Propagate* is called to evaluate all logical implications due to a variable assignment. The overall performance of the solver depends largely on the efficiency of the *Propagate* engine since a SAT solver spends most of its run time propagating implications [KSMS11]. In [MMZ<sup>+</sup>01] a technique based on watching literals by means of pointers is proposed. More specifically for every clause only two literals which are not assigned to *false* are watched. This reduces importantly the bookkeeping of the propagation process since assignments to literals that are not being watched are not

updated. Furthermore, the state of a clause is only updated if the two pointers coincide, i.e. if the clause becomes unit.

• *Backtrack* goes back to the level estimated by *Analyze*. Technically, backtracking is done until the level at which the conflict clause becomes unit. This kind of backtracking is known as *non-chronological backtracking* [MSS99]. Non-chronological backtracking outperforms chronological backtracking as in practice conflicts are caused by assignments performed many levels before and not by the previous assignment. During backtracking, the solver reverts all intermediate assignments and their corresponding implications. For this, the solver benefits from the fact that only non-false literals are tracked and therefore there is no necessity to relocate pointers while backtracking.

SAT solvers integrating these engines are referred to as *conflict-driven clause learning* (CDCL) solvers. State-of-the-art CDCL solvers incorporate different additional techniques such as pre-processing of CNF formulas [JHB12] and rapid restarts [BA15] to increase the overall performance. With these improvements, CDCL solvers can currently handle instances (derived from real-world problems) containing up to tens of millions of variables and clauses [HS15, JLBRS12].

SAT solvers return by default only a single satisfying assignment for CNF formulas that result satisfiable. There are problems however where the set of all satisfying assignments is required. This problem is known as the *All-solutions SAT problem* (All-SAT) [BHvMW09]. In [McM02], an approach based on so-called *blocking clauses* is proposed. It adds incrementally blocking clauses to the clause set of a given problem to avoid getting satisfying assignments that were already found. All-SAT solvers [GSY04, YSTM14] are commonly built on the top of CDCL solvers and employ incremental techniques (cf. next section) to improve performance.

#### **Incremental SAT**

Many problems in formal verification require to solve a sequence of related SAT problems [Sht01, ES03a, CLM<sup>+</sup>10]. Instead of solving each problem independently, incremental SAT solving seeks to propagate useful knowledge collected across the proofs [Hoo93]. In this way, a given proof in the sequence can benefit from information that has been previously learned. A secondary advantage is that the clause set that is shared among the SAT problems does not need to be parsed over and over again. There are a number of incremental SAT solvers such as the ones presented in [Bie08] and [ES03b] that implement efficiently this idea.

After solving a given instance of the SAT problem, an incremental SAT solver allows solving a new SAT problem by adding clauses to the former instance. For solving the new problem, the solver keeps conflict clauses that have been learned in the previous proof(s). These learned conflict clauses then may help to avoid conflicts when solving the new problem.

In practice, mechanisms need to be included that allow a SAT solver to be further called independently of the last performed proof. For this, so-called *assumptions* are used to represent special clauses that do not belong to the general SAT problem. For unsatisfiable instances, implications due to assumptions can be discarded so that the state of the solver, containing among others conflict clauses, can be further used for future calls without the need of a restart.

#### 2.1.3 Converting Circuits into CNF

A combinational circuit can be encoded by a CNF formula using the procedure presented in [Tse68]. For a given circuit, this procedure does not represent directly the output of the circuit. Instead of that, it represents a function that evaluates to *true* only for assignments that are consistent with the circuit (i.e. it represents the characteristic function of the circuit). This ensures that the obtained CNF preserves the satisfiability with respect to the circuit functionality.

For encoding a given circuit, the procedure represents each gate in a (multi-level) combinational circuit as a CNF containing a fixed set of clauses. During the conversion, new extra variables are used to represent the valid assignments of the gate. The resulting CNF is obtained by conjuncting the CNFs of all gates. As a result, the final formula is linear in the size of the circuit.

### 2.2 Verification Based on Bounded Models

Verification based on bounded models examines the validity of a property  $\varphi_l(\pi_l)$  for a set of finite paths  $\pi_l = (s_0, s_1, \dots, s_l)$  in a finite-state transition system, where l is the length of the paths. In general, the paths may also have different lengths within a finite interval of length l. These finite paths all begin in a specific set of starting states and all end in a specific set of ending states, where each state is characterized by appropriate Boolean state predicates. In order to formulate the verification problem we consider:

- T(s, s'): the characteristic function of the transition relation of the finite state system.

- $ispath(\pi_l) = \bigwedge_{i=1}^{l} T(s_{i-1}, s_i)$ : a Boolean predicate obtained by unrolling the transition relation into l time frames.  $ispath(\pi_l)$  is true if  $\pi_l$  is a valid path, i.e., the characterized state sequences can actually be traversed in the concrete transition system.

- $X_C(s_0)$ : a Boolean state predicate of C that imposes the starting state(s) of  $\pi_l$ .

In Bounded Model Checking [BCCZ99], C corresponds typically to the set of initial states (I) of the transition system. In Interval Property Checking [NTW<sup>+</sup>08],  $X_C(s_0)$  does

not constrain the proof to a specific set of reachable starting states. It corresponds to a predicate characterizing an invariant (W) that may only rule out unreachable states at  $s_0$ . In the most simple case, the Interval Property Checker may choose  $X_W(s_0) = true$ , i.e., W is the set of all possible states.

Checking the property  $\varphi_l(\pi_l)$  is then reduced to a tautology check of the formula  $X_C(s_0) \wedge ispath(\pi_l) \implies \varphi_l(\pi_l)$ . In other words, for all paths described by  $X_C(s_0) \wedge ispath(\pi_l)$  the property  $\phi_l(\pi_l)$  holds. Formulations have been proposed for cases where there is a loop in the examined interval [BCCZ99].

The required tautology check can be computed by finding a satisfying assignment for the formula  $X_C(s_0) \wedge ispath(\pi_l) \wedge \neg \varphi_l(\pi_l)$ . If  $\varphi_l(\pi_l)$  is violated, then there exists a counterexample containing a sequence of states for which the property fails. It should be noted that the sequential verification problem is reduced to checking an entirely Boolean formula. The validity of the property can simply be checked by SAT solving. The computational complexity for the resulting check, in practice, is significantly lower than the computations that would result from applying a generic model checker to the same finite-state transition system.

In verification based on bounded models, properties are expressed in linear temporal logic (LTL) [Pnu77]. The most common application is to check *safety properties* of the form Gp. Where G is the *always* temporal modal operator specifying that the formula p holds along every state on the interval l. In Interval Property Checking properties commonly describe cause-effect operations, written as  $Gp = G(a \implies c)$ , that should be performed by the transition system. Where a and c correspond respectively to LTL formulas describing the condition that triggers a given operation (assumption part) and the output sequence that has to be produced by the system (commitment part). In practice, standardized property specification languages such as SVA [Spe08], PSL [Acc04], and ITL [One] are available to ease the specification task.

Different optimizations to the basic proving method have been proposed. Techniques to include additional constraints to the problem are used in order to reduce verification runtime [Sht01, Sht02]. Reductions by exploiting design symmetries [BJW04] have been shown to be effective for verifying regular designs such as memories, processors, and arbiters. Motivated by the observation that a property is commonly not influenced by the whole design, optimizations based on cone-of-influence reduction are presented in [BCRZ99]. Broadly speaking, this optimization performs a structural analysis in order to prune out all the logic that does not belong to the transitive fanin of the properties. As a result, the memory footprint required for the proofs can be reduced.

### 2.3 Symbolic Execution

Symbolic execution is a technique widely used in software verification and testing [Kin76]. A good overview of this technique in the context of software testing is presented in [CS13]. Symbolic execution allows to explore the software behavior for big input spaces which are impractical to cover with techniques based on concrete execution, such as random testing [CH00, CS04, PE05]. On the other hand, compared to other static analysis tools [BPS00, CS05], symbolic execution has the ability to produce a *valid* concrete input together with an execution trace when a problem is discovered (i.e., no false negatives are produced).

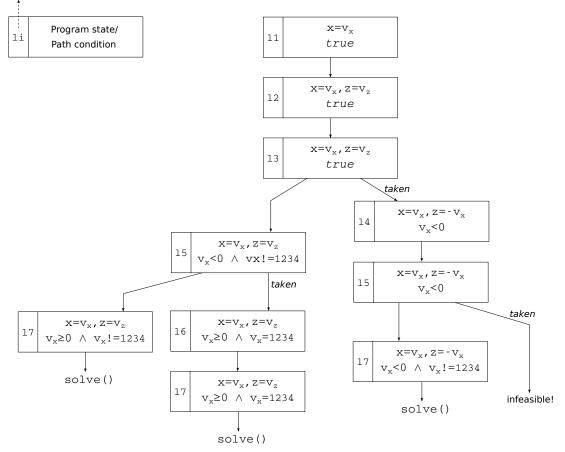

Symbolic execution analyzes the behavior of a given program by exploring systematically its execution paths. It employs symbolic variables to represent the program inputs and describes the software behavior as symbolic formulas in terms of these input variables. At branching points, the path exploration splits to examine each possible execution path. During the exploration, conditions (typically assertions) are checked by feeding a decision procedure (e.g. an SMT solver) with formulas for each check. This task is accomplished by a *symbolic execution engine* (often called *symbolic executor*). Figure 2.2 presents an example (taken from [CDE08]) for a simple C program.

During the analysis, the symbolic execution engine keeps internal record of the program state, the program location (i.e., the program counter) and of the so-called *path conditions*. The program state and the path conditions are expressed in terms of the symbolic inputs. For sequential programs, the program state is composed of the program variables. For a simulated path, the path condition is set to *true* when the path is activated. Furthermore, the formula for the path condition corresponds to the conjunction of all branch conditions along the path.

The execution paths can be represented in an execution tree as shown at the bottom of Figure 2.2. Only those paths that can be activated are represented in the graph. A node in the execution tree represents the execution of a program statement which is identified by its program location. Graph edges correspond to transitions between the statements. Each node is associated with its program state and path condition. At the beginning of the simulation, the path condition is set to *true*, since the first program statement is always executed. When encountering a branch, one of the branches is selected by the execution engine, and the corresponding branching condition is conjoined to the path condition.

In order to tackle the path explosion problem techniques for path pruning and merging are available. Path pruning ensures that only feasible paths are explored in the analysis. This is achieved by making solver calls to check whether the path conditions of new explored branches can be satisfied or not. In Figure 2.2 the path along the two consecutive "taken" branches is infeasible since the corresponding branching conditions are contradictory. With path merging the simulation of (different) divergent paths is joined whenever these paths converge again in the execution. In this way, the exploration does not produce a tree but a

```

11:

int bad_abs(int x){

12:

int z;

13 :

if(x < 0)

14 :

z = -x;

15 :

if(x = 1234)

16 :

z = -x;

17:

assert(x \ge 0);

18:

return z;}

```

Figure 2.2: Symbolic execution example

assert (x >= 0);  $\rightarrow$  if (x >= 0) { assert false; abort(); }

Figure 2.3: Instrumenting assertions in symbolic execution

DAG.

Symbolic execution is commonly used to check assertion violations as well as generic errors such as dangling pointers, buffer overflows, and divisions by zero. For that, the code of the analyzed program is instrumented with assertions. Assertions are typically treated as conditions in order to create explicit error paths. Figure 2.3 presents one example. In this way, the problem of checking assertions is mapped to reachability.

### Chapter 2. Background

## Chapter 3

## **Program Netlists**

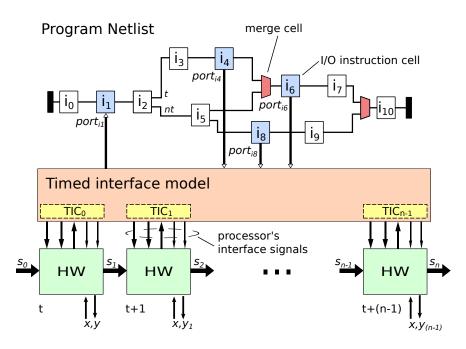

This chapter presents a computational model for hardware-dependent low-level software called program netlist. A program netlist represents the behavior of a low-level embedded program in terms of the hardware structures on which it executes. It has been developed for representing programs that are *reactive* to the hardware, i.e., communication may happen not only at the start and at the end of the program execution but also continuously during run-time.

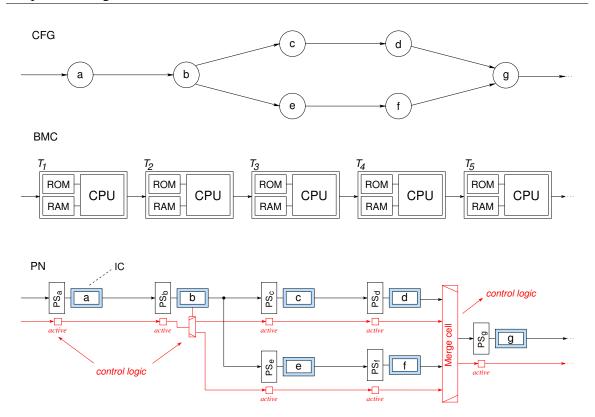

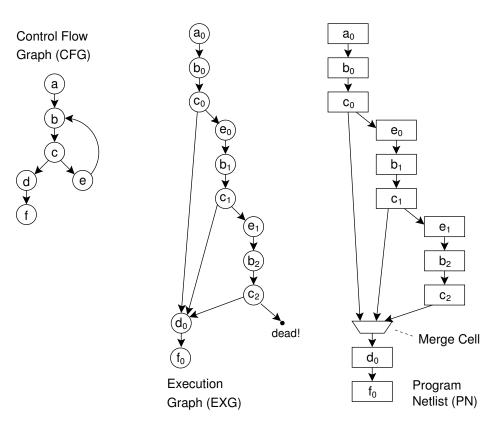

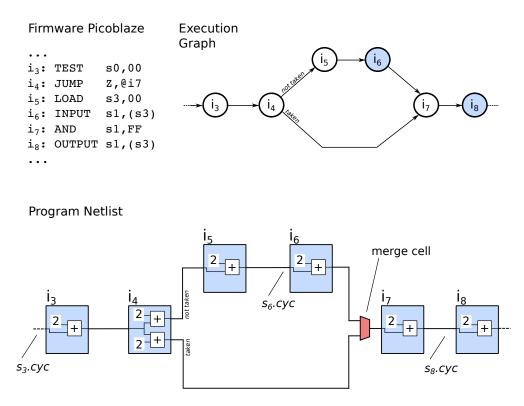

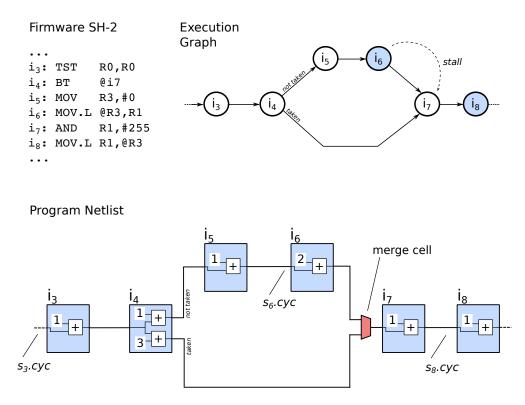

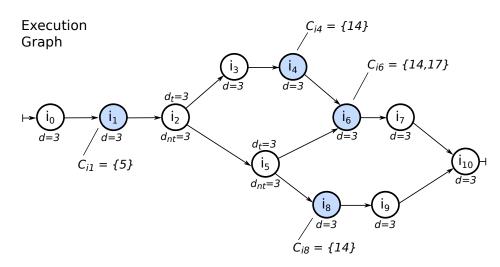

A straightforward approach for verification of hardware-dependent software could be to model the software as binary code stored in a ROM which is connected to the processor hardware. As a result, a hardware model for the entire system is obtained which is represented by its transition relation, T, in the usual way. Verification could be based on Bounded Model Checking [BCC<sup>+</sup>99] by unrolling this transition relation for a finite number of time steps. For instance, the maximum number of clock cycles along the longest execution path of the program could be chosen for the unrolling. Figure 3.1 presents an example. In order to keep the discussion simple it is assumed that the CPU requires one clock cycle to execute each instruction.

Such a hardware-style BMC approach is attractive for hardware-dependent software verification since the behavior of the software can be represented by hardware structures at the desired level of detail. However, the approach will yield a complex computational model representing the entire processor hardware multiple times, once in each *i*-th time step. Only very small designs and only short time windows can be examined with such an approach.

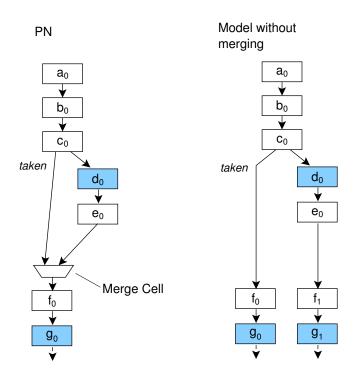

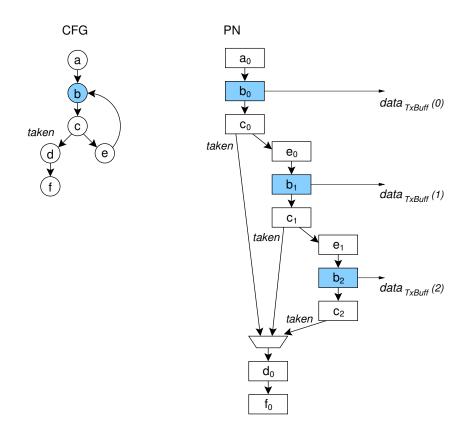

Let us examine what would happen if a SAT solver is used to reason on such a model when performing a given proof. Consider the piece of control flow graph (CFG) and the BMC unrolling shown in the top and in the middle of Figure 3.1. The nodes in the CFG represent individual instructions of the machine code. Each  $T_i$  in the model describes all software behaviors that could occur in the *i*-th time step. In time step 1 instruction *a* is executed. No other instruction can be executed at this point in time. This means that the system can be modeled under the constraint that this particular instruction is performed. This

Figure 3.1: HW-style BMC unrolling against program netlist approach

fact can be exploited to drastically simplify the transition relation  $T_1$ . The same process can be followed to model the system at time point 2. (Only instruction *b* can be executed at that time point.) Now consider time point 3. At this time point, instruction *c* or instruction *e* can be executed.  $T_3$  can still be simplified but it now needs to model both of these instructions. Hence, fewer simplifications to the transition logic can be performed. It is realized that in more complex control flow graphs with numerous branches and loops the simplification can only benefit from such constraints during a fairly small number of steps in the initial parts of a program. At later time points, there will be many possibilities what instructions can be performed. Therefore, when unrolling the transition relation, the individual  $T_i$  will have to model (almost) the entire hardware system, since no (or only few) constraints can be identified. If a SAT solver has to enumerate the search space to prove some property on this model it will obviously suffer from the sheer complexity of this model.

Moreover, there is an additional problem for the SAT solver making the situation even worse. When backtracking through the search space the solver makes assignments to the variables of this model that mix situations occurring in different runs of the program. For example, if instruction c is performed at time 3 it is not possible that instruction f is performed at time 4. If the SAT solver makes assumptions in its branching decisions relating to instruction c at time 3 and instruction f at time 4 it will enter the non-solution area of the search space. It may take a large number of backtracks until this is discovered.

In conclusion, a SAT solver needs to deduce from scratch the possible execution paths of the program via clause learning, backtracking, and similar concepts. This is because the model lacks an explicit view on execution paths. Since the program's control flow is represented only implicitly by the unrolled hardware, reasoning on the program will require a high computational effort. It is then apparent that such a model, even if it was small, is computationally inefficient and would require excessive computational resources.

### 3.1 Basic Idea

The program netlist approach is related to the BMC approach illustrated above, however, key obstacles to scalability are removed. The basic idea is the following. The unrolling of the processor with its instruction and data memory (ROM and RAM respectively) is not done clock cycle by clock cycle, replicating the full transition function for every time frame, but rather *instruction by instruction* (cf. the model on the bottom part of Figure 3.1). At branching points in the software, the unrolled logic is duplicated, modeling each execution branch separately. This instruction-wise unrolling along execution paths allows for a significant reduction in the amount of logic that needs to be replicated: Since the actual instruction in every unrolled logic block is known and fixed, many constants exist that can be propagated in order to simplify the logic block so that all circuitry that is not needed for modeling the instruction behavior is removed.

In fact, this analysis can be moved to a pre-processing step before unrolling (Section 3.3 details on this analysis). As a result of it, information about reachable execution paths of the software is directly encoded into the control logic of the program netlist (cf. logic blocks on the bottom of Figure 3.1). These specific control structures make execution paths and the program's control flow visible to the verification engine.

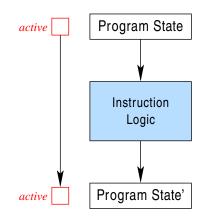

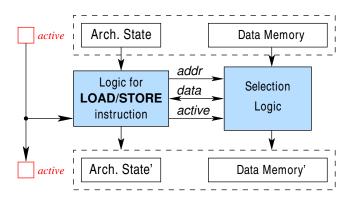

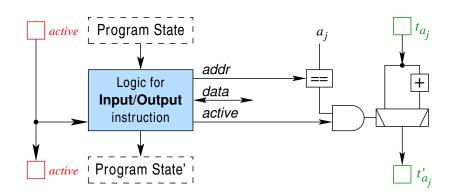

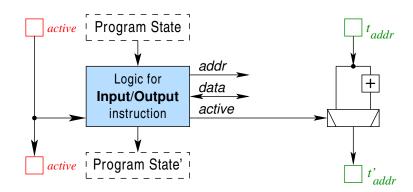

For a given instruction set architecture and machine program, the behavior of the processor can be precisely modeled for each individual instruction of the program. A logic block that models atomically the effects of an individual instruction on a set of state variables is called an *instruction cell* (IC). The set of state variables that the cell modifies depends on the type of instruction and includes registers from the general-purpose register file, status bits, and flags as well as memory locations associated with data variables of the program and input/output registers. (The memory model is described in Section 3.4.) These state variables constitute the *program state* (PS) of the programmable hardware/software system. The subset of these state variables which are internal to the processor are referred to as the *architectural state* (AS) variables.

Connecting instruction cells together and duplicating paths at branches is, by itself, not sufficient for efficiency because the resulting model can become of exponential size in the number of branches. Instead of building a *tree* of instructions, a netlist that has the structure of a directed acyclic graph (DAG) is created. As will be shown next, so-called *merge cells*,

Figure 3.2: Instruction Cell for instruction without branching

as the one placed at the fanin of instruction cell g on Figure 3.1, are used for recombining paths in the program netlist in order to avoid exponential growth of the model.

### **3.2 Instruction Cells**

Instruction cells are the building blocks of the *program netlist*, i.e., the unrolling of the processor's behavior under the control of the program. Instruction cells are parameterized with registers, operation modes, and similar objects so that they can be optimized during model generation, in particular by constant propagation. This leads to compact combinational circuit models.

Instruction cells can be described at different levels of abstractions depending on the level of detail that is required by the given verification tasks. In this work, manually-written abstract instruction cells are used to capture behavior according to the programming model at the instruction set architecture (ISA) level. Instruction cells can be also created for modeling the concrete behavior of the RTL implementation of a specific processor architecture.

Figure 3.2 and Figure 3.3 show examples of instruction cells with and without branching. Combinational logic circuitry changes the program state including architecture registers and variables in the data memory. Instruction cells are connected together at the Program State interfaces (cf. program netlist on Figure 3.1). A connection between two instruction cells indicates a possible transition from a CFG instruction to the next one.

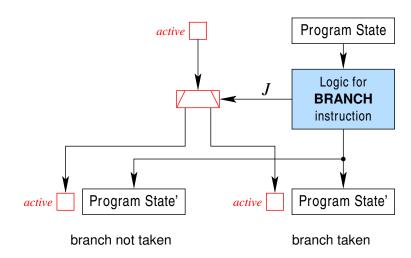

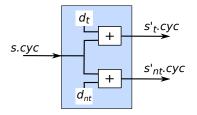

Additionally, an instruction cell models the *control flow* of the program using a special state variable called *active*. In the program netlist, all instructions lying on an actual program execution path have their *active* flag set. A BRANCH instruction as shown in Figure 3.3 produces two possible program states, one for the branch taken and one for the branch not taken. The *active* flag is distributed into the branch selected by the program, as controlled by the instruction logic (signal *J* in Figure 3.3).

Figure 3.3: Instruction Cell for BRANCH instruction

Modeling the control flow in this way is crucial to the performance of SAT-based reasoning on the program netlist as it makes execution paths explicit to the SAT solver. By asserting or de-asserting the *active* signal, whole paths or path segments spanning many time frames can be taken into or out of consideration simultaneously. This gives significant performance improvements over an implicit, unguided enumeration of execution paths as in the straightforward approach discussed above.

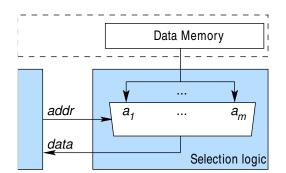

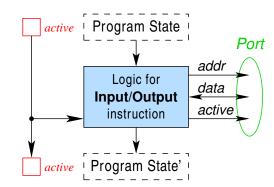

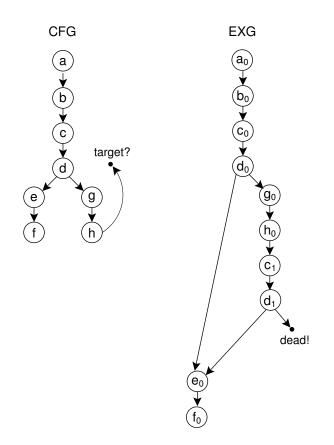

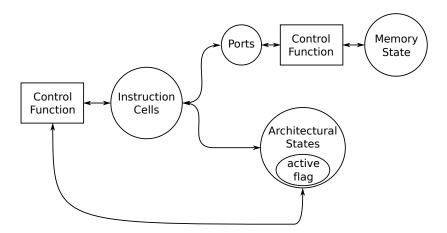

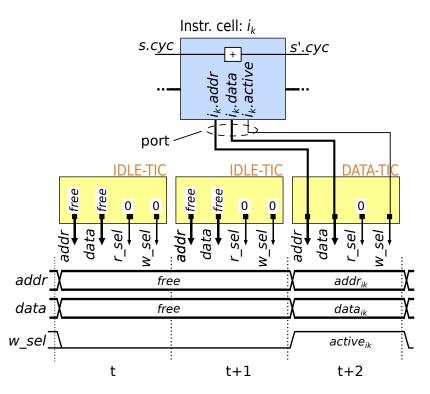

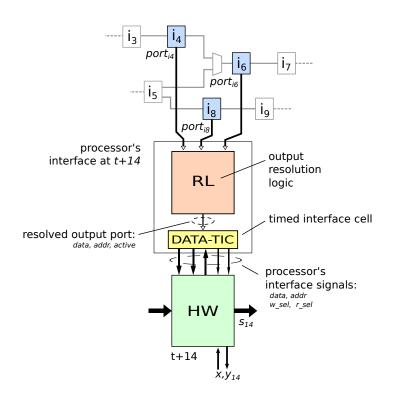

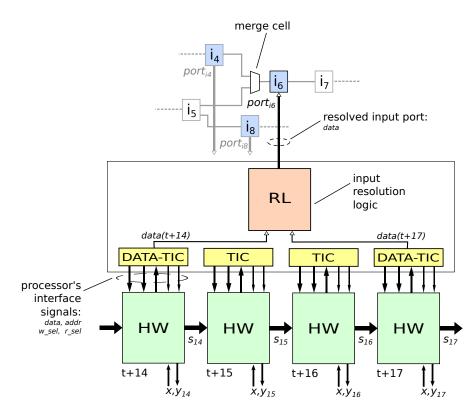

## **3.3 Model Generation**