## Timing Performance Analysis of the Deterministic Ethernet Enhancements Time-Sensitive Networking (TSN) for Use in the Industrial Communication

Zeitliche Leistungsanalyse der deterministischen Ethernet Erweiterungen Time-Sensitive Networking (TSN) für die Verwendung in der industriellen Kommunikation

vom

Fachbereich Elektrotechnik und Informationstechnik

der Technischen Universität Kaiserslautern

zur Verleihung des akademischen Grades eines

## Doktors der Ingenieurwissenschaften (Dr.-Ing.)

Genehmigte Dissertation von

**Dipl.-Ing. Seifeddine Nsaibi** geboren in Tunis, Tunesien

D 386

Tag der mündlichen Prüfung 20.05.2020

Dekan des Fachbereichs: Prof. Dr.-Ing. Ralph Urbansky

Promotionskommission

Vorsitzender: Prof. Dr.-Ing. Norbert Wehn

Berichterstattende: Prof. Dr.-Ing. Hans D. Schotten

Prof. Dr.-Ing. Ludwig Leurs

## Erklärung

| I | ch | erk  | läre, |

|---|----|------|-------|

|   |    | CIIN | ıaıc, |

dass ich die vorliegende Dissertation selbst angefertigt habe und alle von mir benutzten Hilfsmittel angegeben habe,

dass ich die Dissertation oder Teile hiervon noch nicht als Prüfungsarbeit für eine staatliche oder wissenschaftliche Prüfung eingereicht habe,

dass ich nicht die gleiche oder eine andere Abhandlung bei einem anderen Fachbereich oder einer anderen Universität als Dissertation eingereicht habe.

| (Ort, Datum) | (Seifeddine Nsaibi) |

|--------------|---------------------|

## **Publications**

I have authored or co-authored the following publications:

## **Journal Papers**

- Seifeddine Nsaibi, Ludwig Leurs; "Time Sensitive Networking Leistungsversteigerung von Industrial Ethernet"; atp edition, pp. 54-61, October 2016

- Seifeddine Nsaibi, Ludwig Leurs; "Abbildung von TDMA-basierten Industrial Ethernet Protokollen auf TSN am Beispiel von Sercos III"; Springer (122-135) Kommunikation und Bildverarbeitung in der Automation; December 2017

- Seifeddine Nsaibi, Ajitesh Mishra; "Experimental Evaluation of TSN performance"; Industrial Ethernet Book, pp. 33-36; Issue 106 ISSN1470-5745, Mai 2018

### **Conference Papers**

- Seifeddine Nsaibi, Ludwig Leurs; "Chancen und Grenzen der Leistungssteigerung von Industrial-Ethernet Systemen bei der Verwendung von Ethernet Time Sensitive Networking"; AUTOMATION Secure & Reliable in the digital world; Baden-Baden Germany, June 2016

- Seifeddine Nsaibi, Ludwig Leurs; "Ableitung von zukünftigen Steuerungsarchitekturen aus der Kombination von Gigabit- und TSN-Ethernet"; VDE Congress 2016 Internet of Things; Mannheim Germany, November 2016

- Seifeddine Nsaibi, Ludwig Leurs; "Abbildung von TDMA-basierten Industrial Ethernet Protokollen auf TSN am Beispiel von Sercos III"; KommA 2016 – Jahreskolloquium Kommunikation in der Automation; Lemgo Germany, November 2016

- Seifeddine Nsaibi; "Gegenüberstellung der deterministischen Kommunikationsmechanismen von TSN: Netzwerkplanung und Telegrammunterbrechung"; AUTOMATION 2017 Technology Networks Processes; Baden-Baden Germany, June 2017

- Seifeddine Nsaibi, Ludwig Leurs, Hans D. Schotten; "Formal- and Simulation-based Timing Analysis of Industrial-Ethernet Sercos III over TSN"; IEEE/ACM DS-RT; The 21<sup>st</sup> IEEE International Symposium on Distributed Simulation and Real-Time Applications; Rom Italy, October 2017

- Seifeddine Nsaibi, Ludwig Leurs; Hans D. Schotten; "Worst-Case Timing Analysis of Integrating TSN in the Field-Level"; KommA 2017 – Jahreskolloquium Kommunikation in der Automation; Magdeburg Germany, November 2017

#### **Technical Reports**

- Seifeddine Nsaibi; "Sercos III over TSN"; Bosch Networks and Bus Systems; Renningen Germany; April 2017

- Seifeddine Nsaibi; "It's about Time An experimental Evaluation of TSN for integration in the industrial- and automotive fields"; Bosch PhD Conference; Bosch Corporate Research – Renningen Germany; October 2017

- Seifeddine Nsaibi; "TSN Missing Functionalities in the Field-level of the Automation industry"; 2<sup>nd</sup> German IEEE Meet-Up; Stuttgart Germany; February 2017

- Seifeddine Nsaibi; "Worst-Case Timing Analysis of Integrating TSN in the Field-level"; Industrial-Ethernet Workshop; Erbach Germany, December 2017;

# **Contents**

| <b>ERKL</b>       | LÄRUNG                                        | <u></u>  |

|-------------------|-----------------------------------------------|----------|

|                   |                                               |          |

| <u>PUBL</u>       | LICATIONS                                     | 3        |

|                   |                                               |          |

| CONT              | TENTS                                         | 4        |

|                   |                                               |          |

| <u>ACKN</u>       | NOWLEDGEMENT                                  | 8        |

|                   |                                               |          |

| <u>ABST</u>       | TRACT                                         | <u>9</u> |

|                   |                                               |          |

| LIST (            | OF ABBREVIATIONS                              | 13       |

|                   |                                               |          |

| <u>1 IN</u>       | NTRODUCTION                                   | 15       |

|                   |                                               |          |

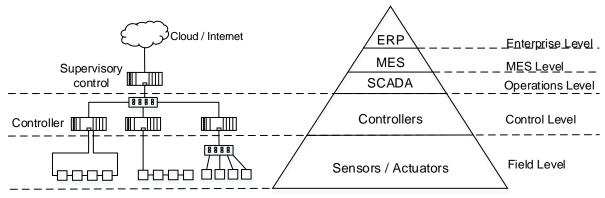

| 1.1               | DETERMINISTIC NETWORKING                      | 15       |

| 1.1.1             |                                               |          |

| 1.1.2             | 2 OSI Model                                   | 19       |

| 1.1.3             |                                               |          |

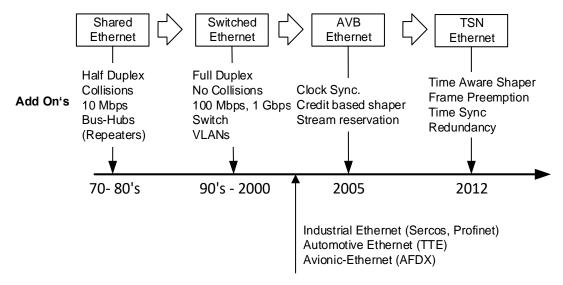

| 1.2               | ETHERNET                                      | 21       |

| 1.2.1             | L IEEE ETHERNET EVOLUTION                     | 22       |

| 1.2.2             | 2 ETHERNET FRAME FORMAT                       | 24       |

| 1.2.3             | REAL-TIME ETHERNET                            | 25       |

| 1.3               | PROBLEM STATEMENT AND THESIS CONTRIBUTION     | 26       |

| 1.3.1             | L SCIENTIFIC GAPS                             | 26       |

| 1.3.2             | 2 Related Works                               | 27       |

| 1.3.3             | 3 CONTRIBUTIONS                               | 28       |

| 1.4               | ANALYSIS APPROACHES                           |          |

| 1.4.1             |                                               |          |

| 1.4.2             |                                               |          |

| 1.4.3             | B EXPERIMENTAL ANALYSIS APPROACH (TEST SETUP) | 30       |

|                   |                                               |          |

| <u>2</u> <u>B</u> | BACKGROUND AND STATE OF THE ART               | 32       |

|                   |                                               |          |

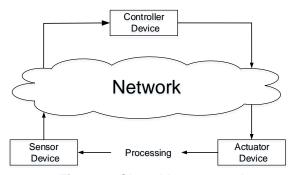

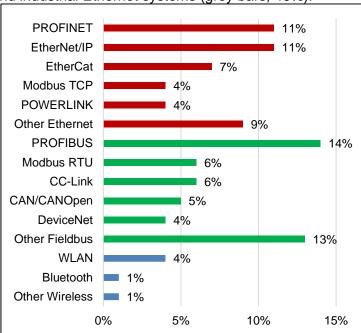

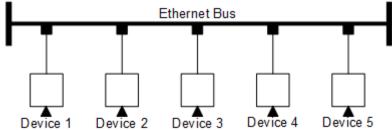

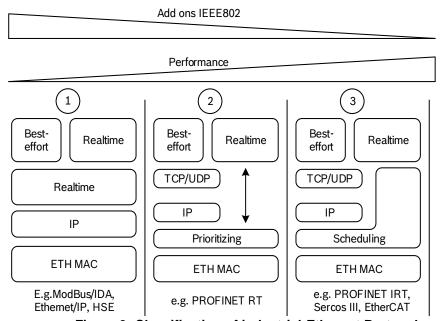

| 2.1               | INDUSTRIAL-ETHERNET                           | 32       |

| 2.1.1             | L REAL-TIME CLASSES                           | 32       |

| 2.1.2             |                                               |          |

| 2.1.3             | 3 Industrial-Ethernet Protocols               | 37       |

| 2.1.4             |                                               |          |

|                   |                                               |          |

| 2.2.1             |                                               |          |

| 2.2.2             |                                               |          |

| 2.2.3             |                                               |          |

|                   |                                               |          |

| 2.3.1             |                                               |          |

| 2.3.2             | 2 Traffic Modeling                            | 50       |

| B EVALUATION METRICS                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

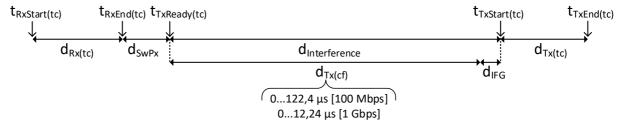

| FLOW TIMING MODEL                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 FORMAL COMPUTATION                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SURVEYS                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

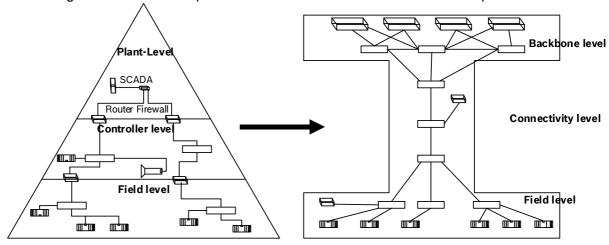

| I FROM AUTOMATION PYRAMID TO AUTOMATION PILLAR         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2 COMMUNICATION FEATURES VS. DELAY PARAMETERS          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B DELAY PARAMETERS                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

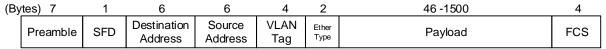

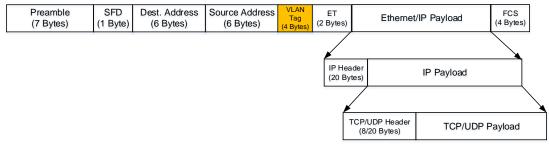

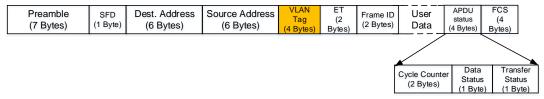

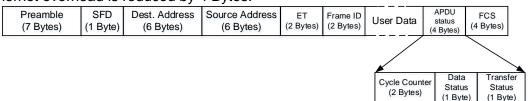

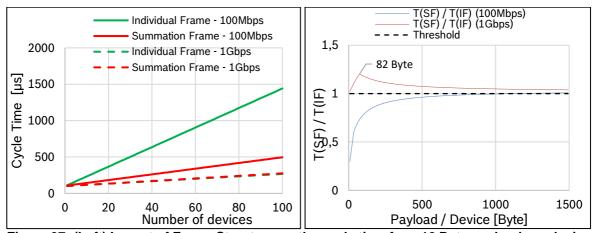

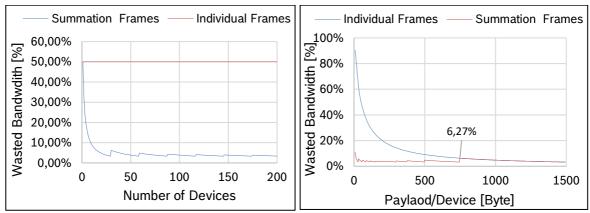

| 1 IMPACT OF FRAME STRUCTURE ON TIMING BEHAVIOR         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ORMAL AND SIMULATIVE TIMING-ANALYSIS OF IEEE 802.1 TSN | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Introduction                                           | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2 Key Performance Indicators                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

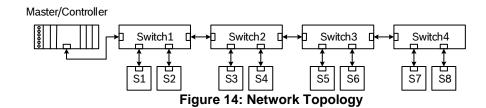

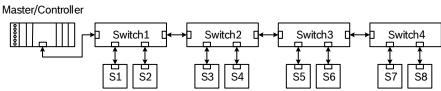

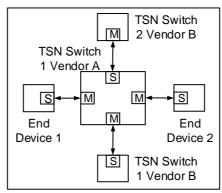

| Network Design                                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

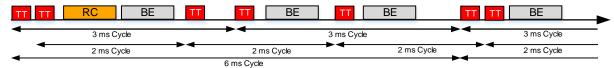

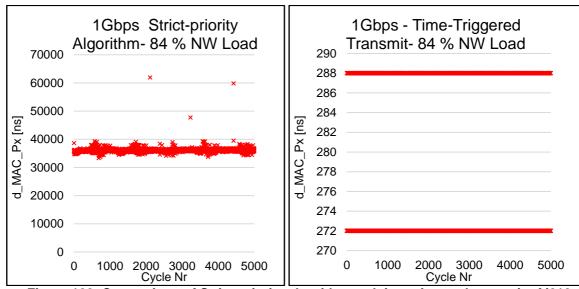

| IEEE802.1Q - Non-Preemptive Strict-Priority Algorithm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

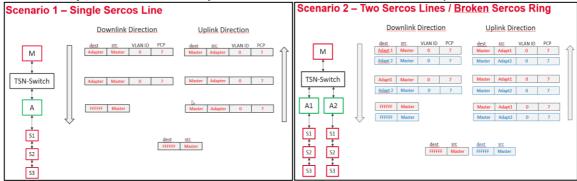

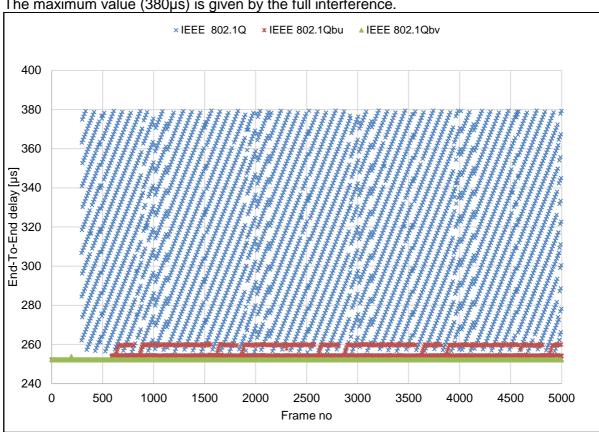

| 3 Scenario 2                                           | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ·                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ,                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ,                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SUMMARY                                                | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NDUSTRIAL-ETHERNET PROTOCOLS OVER TSN                  | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTRODUCTION                                           | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| · · · · · · · · · · · · · · · · · · ·                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5 SUMMARY                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

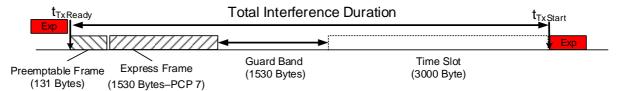

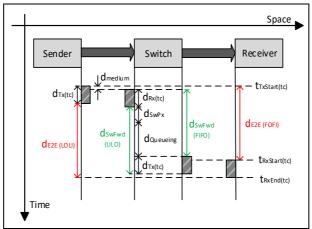

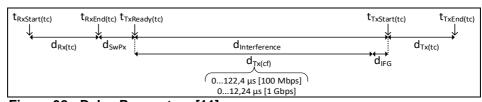

| 15 L231 L231 L231 L231 L231                            | FLOW TIMING MODEL FORMAL COMPUTATION  SURVEYS  FROM AUTOMATION PYRAMID TO AUTOMATION PILLAR  COMMUNICATION FEATURES VS. DELAY PARAMETERS  DELAY PARAMETERS  IMPACT OF FRAME STRUCTURE ON TIMING BEHAVIOR.  ORMAL AND SIMULATIVE TIMING-ANALYSIS OF IEEE 802.1 TSN  INTRODUCTION.  CONTRIBUTIONS  KEY PERFORMANCE INDICATORS.  NETWORK DESIGN  TRAFFICS CONFIGURATION  IEEE802.1Q — Non-PREEMPTIVE STRICT-PRIORITY ALGORITHM  FORMAL FLOW ANALYSIS  SCENARIO 1  SCENARIO 2  SCENARIO 3  SCENARIO 4  SUMMARY  IEEE802.1QBU — PREEMPTIVE STRICT-PRIORITY ALGORITHM  FORMAL FLOW ANALYSIS  INTERFERENCE WITH PREEMPTABLE TRAFFIC (133 BYTE)  INTERFERENCE WITH PREEMPTABLE TRAFFIC (131 BYTE)  INTERFERENCE WITH EXPRESS- AND PREEMPTABLE-TRAFFICS  IEEE802.1QBV — TIME-AWARE SHAPER  FORMAL FLOW ANALYSIS  SCENARIO 1  SCENARIO 2  SUMMARY  SCENARIO 1  SCENARIO 2  SUMMARY  EVALUATION OF TRANSMISSION SELECTION ALGORITHMS  MAPPING TSN TO THE DETERMINISTIC INDUSTRIAL APPLICATIONS  SUMMARY  NOUSTRIAL-ETHERNET PROTOCOLS OVER TSN.  INTRODUCTION.  NETWORK DESCRIPTION.  CONTRIBUTIONS  ETHERNET/IP.  FORMAL TIMING ANALYSIS  TIMING ANALYSIS WITH FRAME-PREEMPTION (IEEE802.1QBU). |

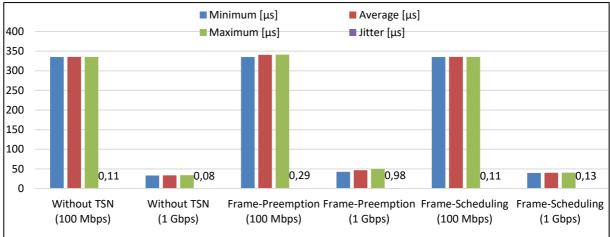

| 4.3.1        | FORMAL TIMING ANALYSIS                               | 95  |

|--------------|------------------------------------------------------|-----|

| 4.3.2        | TIMING ANALYSIS WITH GIGABIT-ETHERNET                | 96  |

| 4.3.3        | TIMING ANALYSIS WITH FRAME-PREEMPTION (IEEE802.1QBU) | 97  |

| 4.3.4        | TIMING ANALYSIS WITH FRAME-SCHEDULING (IEEE802.1QBV) | 98  |

| 4.3.5        | Summary                                              | 98  |

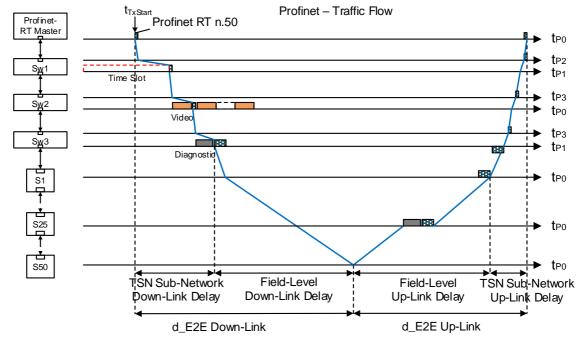

| 4.4          | PROFINET IRT                                         | 99  |

| 4.4.1        | FORMAL TIMING ANALYSIS                               | 99  |

| 4.4.2        | TIMING ANALYSIS WITH GIGABIT-ETHERNET                | 100 |

| 4.4.3        | TIMING ANALYSIS WITH FRAME-PREEMPTION (IEEE802.1QBU) | 100 |

| 4.4.4        | TIMING ANALYSIS WITH FRAME-SCHEDULING (IEEE802.1QBV) | 101 |

| 4.4.5        | Summary                                              | 102 |

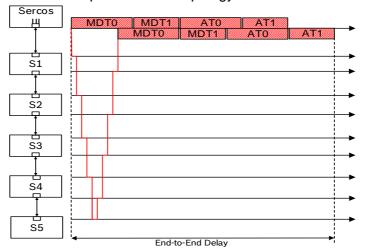

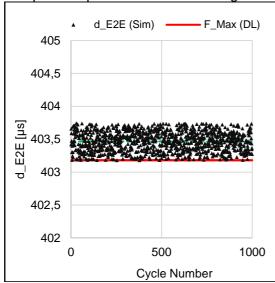

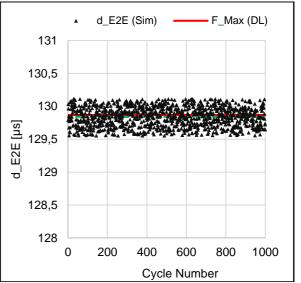

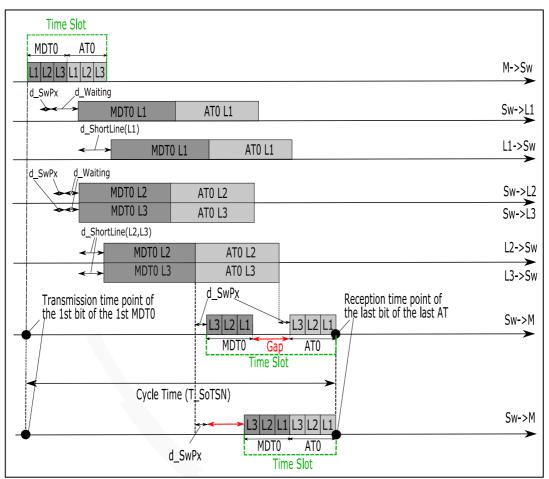

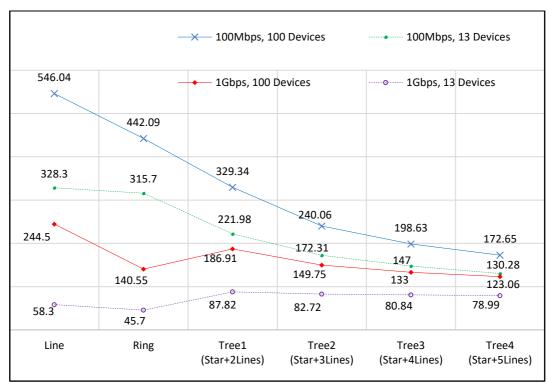

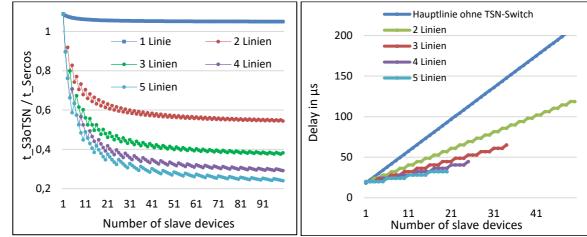

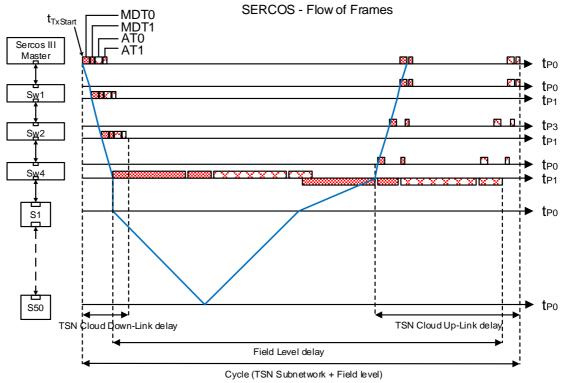

| 4.5          | SERCOS III                                           | 102 |

| 4.5.1        | FORMAL TIMING ANALYSIS                               | 102 |

| 4.5.2        | TIMING ANALYSIS WITH GIGABIT-ETHERNET                | 104 |

| 4.5.3        | TIMING ANALYSIS WITH FRAME-PREEMPTION (IEEE802.1QBU) | 104 |

| 4.5.4        | TIMING ANALYSIS WITH FRAME-SCHEDULING (IEEE802.1QBV) | 105 |

| 4.5.5        | Summary                                              | 106 |

| 4.5.6        | CHALLENGES AND BENEFITS OF INTEGRATING TSN IN SERCOS | 106 |

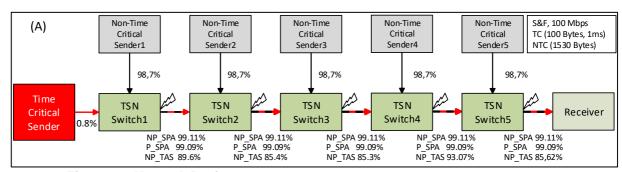

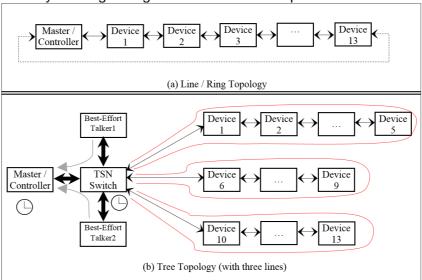

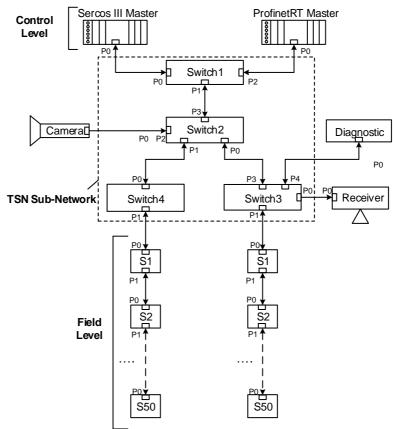

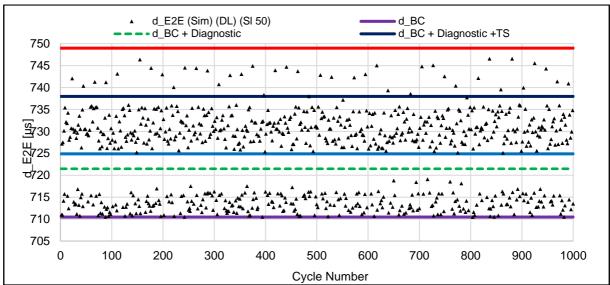

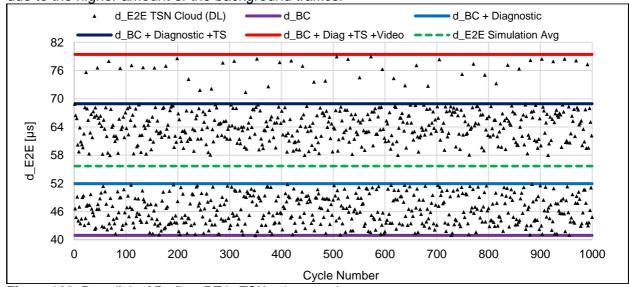

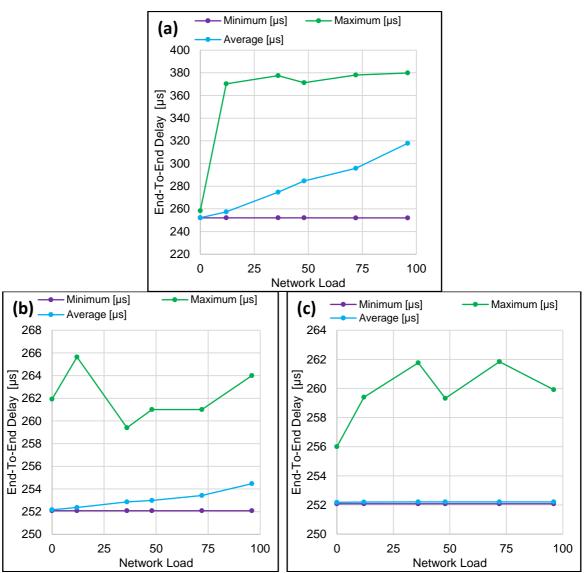

| 4.6          | CONVERGED NETWORK                                    | 113 |

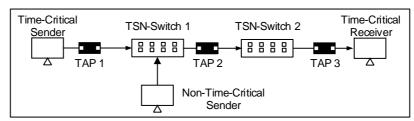

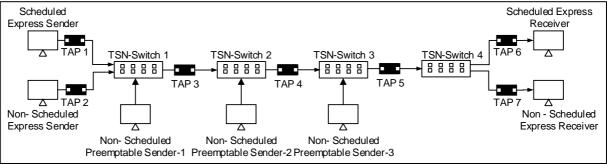

| 4.6.1        | NETWORK DESCRIPTION                                  | 113 |

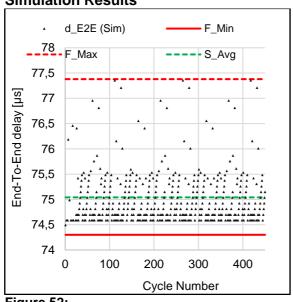

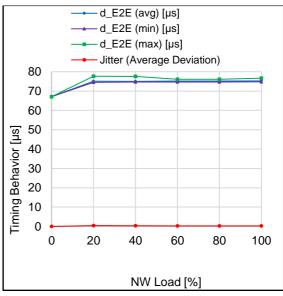

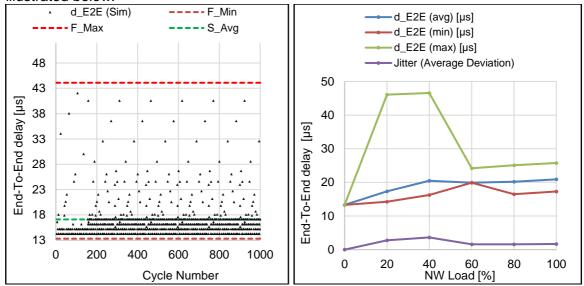

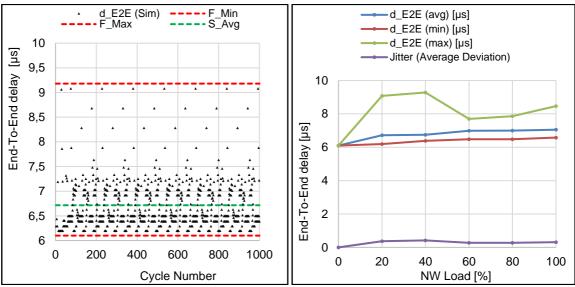

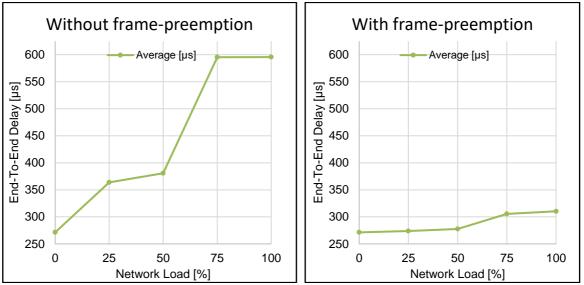

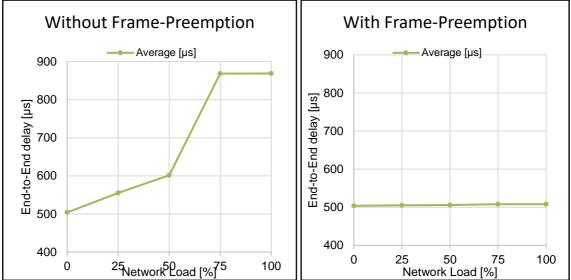

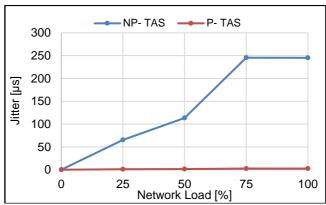

| 4.6.2        | SIMULATION RESULTS                                   | 115 |

| 4.6.3        | Conclusion                                           | 118 |

| 5 E          | XPERIMENTAL EVALUATION OF TSN-PROTOTYPES             | 120 |

|              |                                                      | -   |

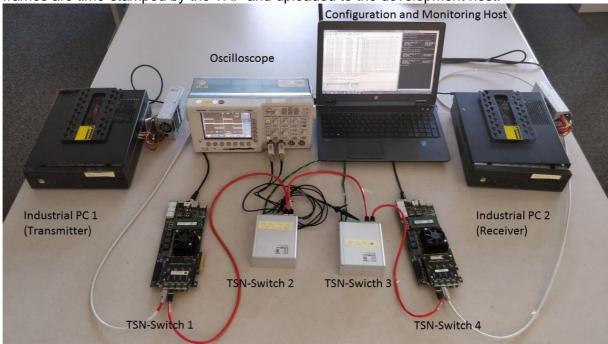

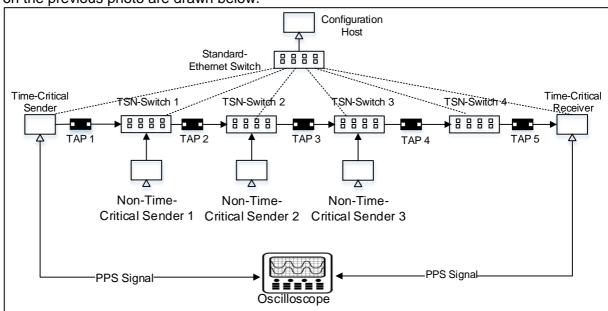

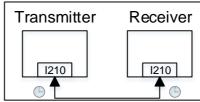

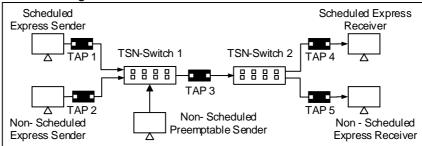

| 5.1          | TEST SETUP DESCRIPTION                               | 120 |

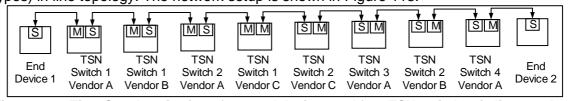

| 5.1.1        | TSN Test setup                                       | 122 |

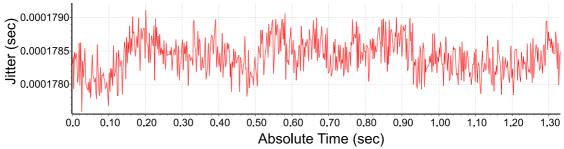

| 5.2          | TIME SYNCHRONIZATION                                 |     |

| 5.2.1        |                                                      |     |

| 5.2.2        |                                                      |     |

| 5.3          | INTEL® I210 EVALUATION                               |     |

| 5.3.1        |                                                      |     |

| 5.3.2        |                                                      |     |

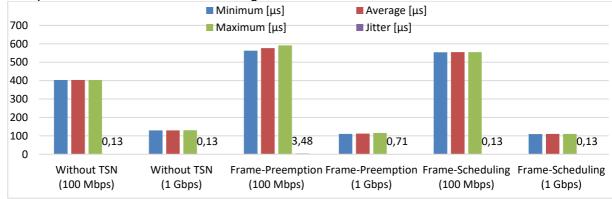

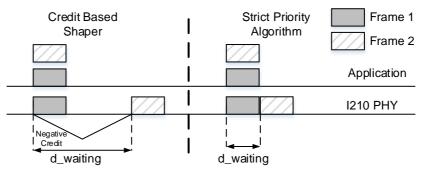

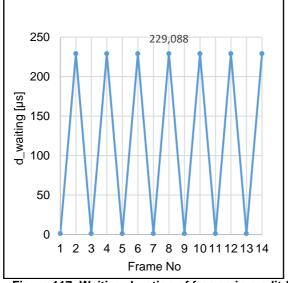

| 5.4          | TRAFFIC SHAPING                                      |     |

| 5.4.1        |                                                      |     |

| 5.4.2        |                                                      |     |

| 5.4.3        |                                                      |     |

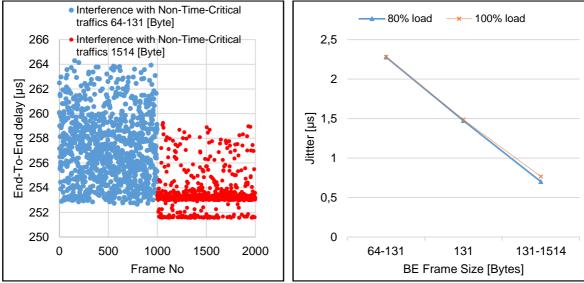

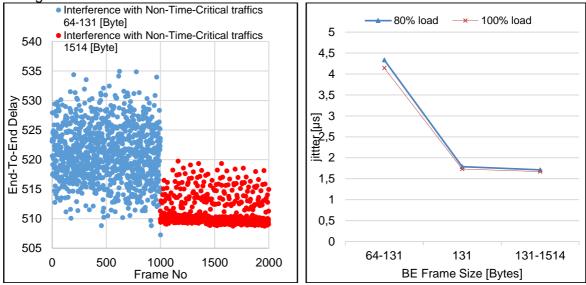

| 5.4.4        | IMPACT OF THE BACKGROUND FRAMES SIZES ON JITTER      | 153 |

| <u>6 C</u>   | ONCLUSION AND OUTLOOK                                | 157 |

|              |                                                      |     |

| 6.1          | OVERVIEW AND CONTRIBUTIONS                           | 157 |

|              | OUTLOOK                                              |     |

|              |                                                      |     |

| <u>BIBLI</u> | OGRAPHY                                              | 160 |

| LICT 4       | OF FIGURES                                           | 164 |

| LIST (       | UF FIGURES                                           | 164 |

|              |                                                      |     |

| LIST (       | OF TABLES                                            | 168 |

## **Acknowledgement**

This thesis is written during my time as a PhD student at Bosch Rexroth AG in Lohr am Main. I thank God for guiding me through my life and I offer this PhD to my parents Amor and Saliha my dear Khawla, Alaeddine and Khalil.

My deep gratitude goes to Prof. Dr.-Ing. Hans D. Schotten for supervising my thesis and many fruitful discussions. His early advice and his pragmatic mentoring style helped me during my research and contributed on my career path.

A big thank to Prof. Dr.-Ing. Ludwig Leurs, who took on my supervision at Bosch Rexroth AG. I will not forget his willingness to contribute and extend my technical know-how nor our technical discussions.

My appreciation also extents to my Bosch department (DC-AE/EAS) for the financial support to extend the research results.

Last but not least I thank my former students: Adarsh Nayak, Ajitesh Mishra, Kamran Khadir Mohammed and Karima Saif Khandaker for the unforgettably successful brainstorming and the close cooperation that made it possible to publish our research results in multiple journals, workshops and conferences. Many thanks!

Lohr am Main, Dezember 2018

Seifeddine Nsaibi

## **Abstract**

Ethernet has become an established communication technology in industrial automation. This was possible thanks to the tremendous technological advances and enhancements of Ethernet such as increasing the link-speed, integrating the full-duplex transmission and the use of switches. However these enhancements were still not enough for certain high deterministic industrial applications such as motion control, which requires cycle time below one millisecond and jitter or delay deviation below one microsecond. To meet these high timing requirements, machine and plant manufacturers had to extend the standard Ethernet with real-time capability. As a result, vendor-specific and non-IEEE standard-compliant "Industrial Ethernet" (IE) solutions have emerged.

The IEEE Time-Sensitive Networking (TSN) Task Group specifies new IEEE-conformant functionalities and mechanisms to enable the determinism missing from Ethernet. Standard-compliant systems are very attractive to the industry because they guarantee investment security and sustainable solutions. TSN is considered therefore to be an opportunity to increase the performance of established Industrial-Ethernet systems and to move forward to Industry 4.0, which require standard mechanisms.

The challenge remains, however, for the Industrial Ethernet organizations to combine their protocols with the TSN standards without running the risk of creating incompatible technologies. TSN specifies 9 standards and enhancements that handle multiple communication aspects. In this thesis, the evaluation of the use of TSN in industrial real-time communication is restricted to four deterministic standards: IEEE802.1AS-Rev, IEEE802.1Qbu IEEE802.3br and IEEE802.1Qbv. The specification of these TSN substandards was finished at an early research stage of the thesis and hardware prototypes were available.

Integrating TSN into the Industrial-Ethernet protocols is considered a substantial strategical challenge for the industry. The benefits, limits and risks are too complex to estimate without a thorough investigation. The large number of Standard enhancements makes it hard to select the required/appropriate functionalities.

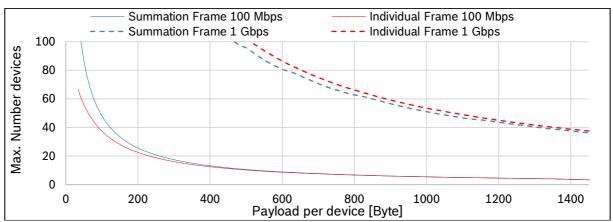

In order to cover all real-time classes in the automation [9], four established Industrial-Ethernet protocols have been selected for evaluation and combination with TSN as well as other performance relevant communication features.

#### The **objectives** of this thesis are to

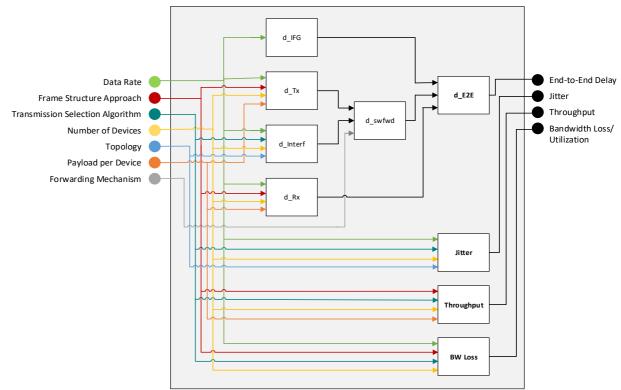

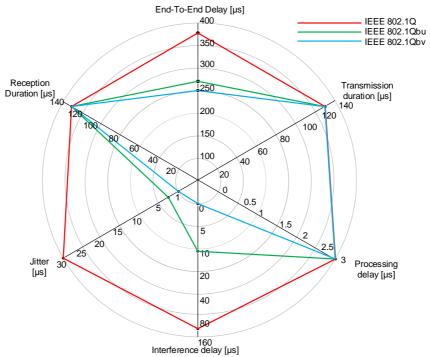

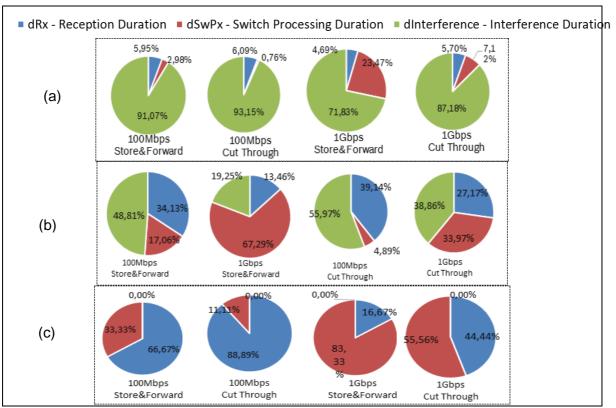

- (1) Provide theoretical, simulation and experimental evaluation-methodologies for the timing performance analysis of the deterministic TSN-standards mentioned above. Multiple test-plans are specified to evaluate the performance and compatibility of early version TSN-prototypes from different providers.

- (2) Investigate multiple approaches and deduce migration strategies to integrate these features into the established Industrial-Ethernet protocols: Sercos III, Profinet IRT, Profinet RT and Ethernet/IP. A scenario of coexistence of time-critical traffic with other traffic in a TSN-network proves that the timing performance for highly deterministic applications, e.g. motion-control, can only be guaranteed by the TSN scheduling algorithm IEEE802.1Qbv.

Based on a **requirements** survey of highly deterministic industrial applications, multiple network scenarios and experiments are presented. The results are summarized into two case studies. The **first case study** shows that TSN alone is not enough to meet these requirements. The **second case study** investigates the benefits of additional mechanisms (Gigabit linkspeed, minimum cycle time modeling, frame forwarding mechanisms, frame structure, topology migration, etc.) in combination with the TSN features.

An **implementation prototype** of the proposed system and a **simulation case study** are used for the evaluation of the approach. The prototype is used for the evaluation and validation of the simulation model. Due to given scalability constraints of the prototype (no cut-through functionalities, limited number of TSN-prototypes, etc...), a realistic simulation model, using the network simulation tool OMNEST / OMNeT++, is conducted.

The obtained **evaluation results** show that a minimum cycle time  $\leq 1$  ms and a maximum jitter  $\leq 1$  µs can be achieved with the presented approaches.

## Zusammenfassung

Ethernet hat sich erfolgreich als Kommunikationstechnologie in der industriellen Automatisierung etabliert. Dies war dank der enormen technologischen Fortschritte und Verbesserungen des Ethernets möglich, z. B. Mehrfache Erhöhung der Datenrate, Einführung der Vollduplex-Übertragung sowie die Verwendung von Switches für die komplette Vermeidung von Kollisionen. Dennoch waren diese Features nicht ausreichend für bestimmte hoch deterministische industrielle Anwendungen, z. B. für die Bewegungssteuerung, die Zykluszeiten unter einer Millisekunde und Jitter bzw. Verzögerungsabweichungen unter einer Mikrosekunde erfordert. Um diesen hohen zeitlichen Anforderungen gerecht zu werden, mussten die Maschinen- und Anlagenhersteller das Standard-Ethernet um die harte Echtzeitfähigkeit erweitern. Infolgedessen sind herstellerspezifische und nicht IEEE-Standardkompatible "Industrial Ethernet" -Lösungen (IE) entstanden. Dies wiederspricht sich mit dem Industrie 4.0 Konzept, welches ein einheitliches Kommunikationsstandard bevorzugt.

Die TSN-Taskgruppe IEEE Time-Sensitive Networking spezifiziert neue IEEE-konforme Funktionen und Mechanismen, um den fehlenden Determinismus von Ethernet zu ermöglichen. Standardkonforme Systeme sind für die Industrie sehr attraktiv, da sie Investitionssicherheit und nachhaltige Lösungen garantieren. Daher wird TSN als eine Gelegenheit betrachtet, die Leistung der etablierten Industrial-Ethernet-Systeme zu steigern und zu Industrie 4.0 überzugehen, die Standardmechanismen erfordert. Die Herausforderung für die Industrial Ethernet-Organisationen besteht jedoch weiterhin darin, ihre Protokolle mit den TSN-Standards zu kombinieren, ohne dass dabei ein Technologiebruch entsteht. TSN spezifiziert 9 Sub-Standards, die mehrere Kommunikationsaspekte handhaben.

Um die Verwendung von TSN in der industriellen Echtzeitkommunikation zu bewerten, ist der Fokus dieser Arbeit auf die vier deterministischen TSN Sub-Standards: IEEE802.1AS-Rev, IEEE802.1Qbu IEEE802.3br und IEEE802.1Qbv.

Diese Sub-Standards wurden im Laufe dieser Dissertation teilweise fertig spezifiziert und als Hardware-Prototypen zur Verfügung gestellt.

Eine Integrationsstrategie von TSN in die Industrial-Ethernet-Protokolle gilt als eine große Herausforderung für die Industrial-Ethernet-Organisationen. Die Vorteile, Grenzen und Risiken sind zu komplex, um sie ohne eingehende Untersuchung abzuschätzen. Die große Anzahl von Standards-Erweiterungen erschwert die Auswahl der erforderlichen / geeigneten Funktionen. Um alle Echtzeitklassen [9] in der Automatisierung abzudecken, wurden vier etablierte Industrial-Ethernet-Protokolle mit unterschiedlichen Leistungsmerkmalen für die Bewertung und Kombination mit TSN sowie andere Kommunikationsfunktionen ausgewählt, die die Leistungsdaten beeinflussen.

Die Ziele dieser Arbeit sind:

- (1) Bereitstellung einer experimentellen Evaluierungsmethode für die Timing-Performance-Analyse der oben genannten deterministischen TSN-Standards. Es werden mehrere Testpläne angegeben, um die Leistung und Kompatibilität von TSN-Prototypen früherer Versionen verschiedener Anbieter zu bewerten.

- (2) Untersuchung verschiedener Ansätze sowie die Ableitung von Migrationsstrategien, um diese Funktionen in die etablierten Industrial-Ethernet-Protokolle in TSN zu integrieren: Sercos III, Profinet IRT, Profinet RT und Ethernet / IP. Ein Szenario der Koexistenz zeitkritischer Verkehr mit anderen Verkehrsträgern in einer TSN-Cloud beweist, dass die Zeitsteuerungsleistungen für Steuerungsdaten nur durch den TSN-Scheduling-Algorithmus IEEE802.1Qbv garantiert werden können.

Basierend auf einer Anforderungsübersicht über deterministische industrielle Anwendungen werden mehrere Netzwerkszenarien und Experimente vorgestellt. Die Ergebnisse werden in