# Property-Driven Design A new approach for hardware design

Vom Fachbereich Elektrotechnik und Informationstechnik der Technische Universität Kaiserslautern zur Verleihung des akademischen Grades

# Doktor der Ingenieurswissenschaften (Dr.-Ing.)

genehmigte Dissertation von

### **Tobias Ludwig**

geboren in Merzig, Deutschland

#### D 386

Datum der mündlichen Prüfung: 16.07.21

Dekan des Fachbereichs: Prof. Dr.-Ing. Ralph Urbansky

Vorsitzender der Prüfungskommission: Prof. Dipl.-Ing. Dr. Gehard Fohler

Gutachter: Prof. Dr.-Ing. Wolfgang Kunz

Prof. Dr.-Ing. Ulrich Heinkel

# Acknowledgments

This thesis is the result of several years of research carried out while I have been part of the "electronic design automation group" at the University of Kaiserslautern. This work benefits from the close collaboration of our group during this period. Furthermore I'd like to thank all my student and research assistants that contributed to my work within the recent years.

Most important, I would like to thank my supervisors, Prof. Wolfgang Kunz and Prof. Dominik Stoffel, who have made my research possible. Thank you for all the good advice, many hours in the seminar room and the possibilities I had during my time as a PhD. I am really glad that I had the chance to work with you.

Specifically, I would like to mention: Joakim Urdahl for supporting me as a colleague, mentor and friend; Nawras Altaleb, Ibrahim Alkoudsi, Lucas Deutschmann, Alex Wezel and Paulius Morkunas for their major code contributions; Michael Schwarz for the reviews, as colleague and friend.

Many thanks also to Prof. Ulrich Heinkel for his in-depth analysis in the review of this thesis and to Prof. Gerhard Fohler for chairing the examination procedures.

To all my friends that where always ready to support me and listen to my ideas and dreams. A special thanks goes to Frank and Joachim for following along the same path with me since school and to Lea for always supporting me.

To my parents who made this entire journey possible with their endless support during all these years.

To everyone that made my time in Kaiserslautern cheerful.

Kaiserslautern, 30.12. 2020 Tobias Ludwig

# Contents

| Acknowledgments |      |                                                 |  |    |

|-----------------|------|-------------------------------------------------|--|----|

| 1               | Intr | roduction                                       |  | 7  |

| 2               | Bac  | ckground                                        |  | 11 |

|                 | 2.1  | Electronic System Level                         |  | 11 |

|                 |      | 2.1.1 Modeling Systems                          |  | 12 |

|                 |      | 2.1.2 SystemC                                   |  | 14 |

|                 |      | 2.1.3 Design Flows                              |  | 16 |

|                 |      | 2.1.4 Semantic gap                              |  | 17 |

|                 | 2.2  | Model Checking                                  |  | 19 |

|                 |      | 2.2.1 Sequential model                          |  | 19 |

|                 |      | 2.2.2 Linear Temporal Logic                     |  | 22 |

|                 |      | 2.2.3 IPC                                       |  | 23 |

|                 | 2.3  | Complete Interval Property Checking             |  | 25 |

|                 |      | 2.3.1 Terminology                               |  | 25 |

|                 |      | 2.3.2 Completeness Criterion                    |  | 27 |

|                 |      | 2.3.3 Completeness Check                        |  | 28 |

|                 |      | 2.3.4 Case Split Test                           |  | 29 |

|                 |      | 2.3.5 Successor Test                            |  | 30 |

|                 |      | 2.3.6 Determination Test                        |  | 31 |

|                 |      | 2.3.7 Reset Test                                |  | 32 |

|                 | 2.4  | Satisfiability Modulo Theories                  |  | 32 |

|                 | 2.5  | $S^2QED$                                        |  | 34 |

|                 | 2.6  | Publication List                                |  | 35 |

|                 | 2.7  | Related work                                    |  | 36 |

| 3               | Pro  | operty Driven Development                       |  | 39 |

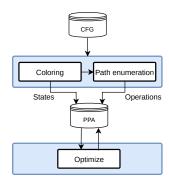

| 4               | Pat  | th Predicate Abstraction                        |  | 43 |

| -               | 4.1  | PPA for graphs                                  |  | 44 |

|                 | 4.2  | PPA for FSM                                     |  |    |

|                 | 4.3  | Compositional PPA                               |  | 49 |

|                 | 1.0  | 4.3.1 Communication schemes in digital hardware |  |    |

|                 |      | 4.3.2 Modeling Communication                    |  |    |

|                 |      | 4.3.3 Synchronization and wait-stuttering       |  |    |

|                 |      | 4.3.4 Model checking on the abstract system     |  |    |

# Chapter 1

# Introduction

Today, the Register Transfer Level (RTL) is still the central anchor point in most methodologies for designing the hardware of a System-on-Chip (SoC) or Embedded System. After decades of evolutionary progress, industrial design environments for hardware have reached a high level of sophistication. Yet — despite all the progress related to design at the Electronic System Level (ESL) with new system-level languages and design environments integrating virtual prototypes and advanced verification techniques — the actual conceptual process of RTL design based on languages like VHDL and Verilog has not much changed over the last decades.

Although High-Level Synthesis (HLS) has evolved to be applicable in certain domains, such as implementations of signal processing algorithms, the bulk of RTL designs in industry is still created manually, starting from informal specifications such as natural language descriptions, conceptual diagrams of finite state machines (FSMs), timing diagrams, flow charts et cetera. In almost all practical settings, RTL descriptions are the reference point for verification. Even in HLS-based flows, usually, the RTL description remains the "golden model" for sign-off. System-level models, on the other hand, are usually considered "prototypes" employed for early assessments of functional and non-functional design goals. The extent to which these prototypes really reflect the characteristics of the final RTL implementation, however, is often difficult to determine. In fact, this disconnection between System Level and RTL implementation is one of the main risk factors in today's industrial design flows.

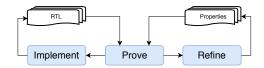

In the scope of this thesis, we work towards a new approach for RTL design, starting from a system-level description. The proposed methodology is based on a manual design process and does not impose any restrictions on designers w.r.t. the developed implementations. However, new tool support is provided, based on formal techniques for verification and abstraction, ensuring that both the hardware IP and the verification IP are developed in a systematic and compositional manner. The most important benefit of the proposed method is that a formally well-defined relationship is established between the RTL description and the system-level model used as the starting point for our method. This aspect is key. It allows us to safely deviate from today's design practices and to move towards employing abstract system models as *golden* design models.

The proposed approach called "Property First Hardware Design" or "Property-Driven Hardware Design (PDD)" takes inspiration from software engineering and widely used practices in software development like "Test First Development" or "Test-Driven Development"

opment (TDD)"" [1]. The TDD paradigm deviates from the classical V-model for software development and is based on the conviction that the actual software development process is positively affected by creating software tests *prior* to writing the actual program code. Such gray-box tests have shown to lead to higher fault coverage when compared to the classical white-box tests of the V-model.

Transferring this idea to the hardware domain suggests a methodology that integrates verification steps early and systematically into the design process. The role of software tests in TDD can be assumed in hardware design by properties or assertions formulated in property languages like the Property Specification Language (PSL) or System Verilog Assertions (SVA). A distinct feature of our methodology – and under this aspect the analogy with the software domain is no longer valid – is the systematic creation of properties for which abstract descriptions are automatically generated from the design's system-level model. Adapting this to the special needs of RTL hardware design and running modern formal verification techniques in the background of our design environment results in a systematic and intuitive design procedure (without restricting the designer's freedom). Finally, this allows for formal statements about the functional correctness of the obtained RTL implementation.

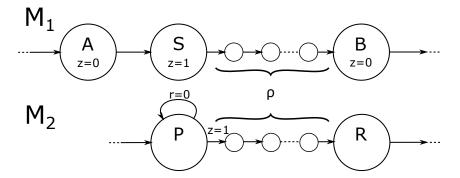

There is a key attribute to the methodology that is formally guaranteed by the specific way the properties are initially generated and later refined: when all created properties are proven on the developed design it can be concluded with mathematical rigor that the RTL design represents a correct refinement of the system-level description from which the properties were generated. This is ensured by a well-defined formal relationship established between the abstract model and its concrete implementation, called Path Predicate Abstraction (PPA) [2]. Conversely, this means that after successfully completing the design process the system-level model represents a formally sound abstraction of the implementation.

Establishing system-level models as PPAs of RTL designs can change the role of system-level models fundamentally: rather than being "prototypes" and having only a loosely defined relationship with the implementation they may now be trusted as "design models", just like RTL design models are trusted to be sound abstractions of the underlying gate level (by merit of formal equivalence checking). Based on Path Predicate Abstraction (PPA), the theoretical framework we provide establishes a formal link between the abstract system model and the concrete RTL design. In our methodology, the semantics of the system model is defined by compositional PPA.

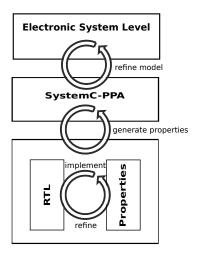

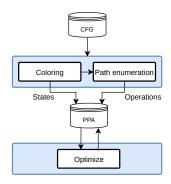

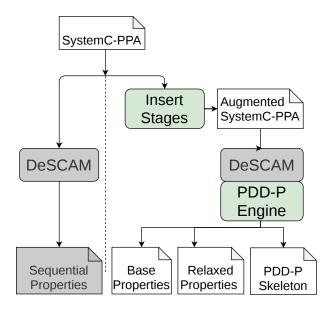

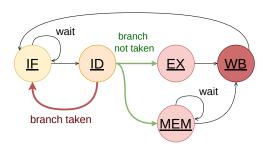

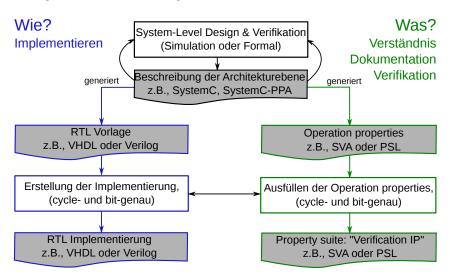

We show how this can be used in a realistic design methodology based on standard languages. This is subject of Chap. 3. We introduce a subset of SystemC called SystemC-PPA for describing system-level models and present the PDD flow in which abstract property descriptions are automatically generated from SystemC-PPA and subsequently refined during the design process. A major contribution of this work is the open-source tool DeSCAM that reads the SystemC-PPA description and automatically generates the properties. In Chap. 5 we introduce the tool and describe how the properties are generated correct-by-construction. A challenging task is to implement a *pipelined* design from an abstract model. We develop a special methodology for this problem in Chap. 6. It helps the designer to ensure a sound implementation and to solve possible hazards.

In Chap. 7 we report on case studies conducted for several industrial and open-source designs. Our experimental results show that fully verified RTL designs can be created by

PDD as formally well-defined refinements of system-level descriptions. All design steps are based on standard languages and only employ state-of-the-art formal property checking, as it is commercially available. The manual effort for design and verification is reduced substantially.

# Chapter 2

# Background

This section presents general background and notations that are relevant for the understanding of later chapters. Sec 2.1 elaborates on the Electronic System Level. We introduce formal techniques in Sec 2.2 and Sec 2.3, that are used to bridge the semantic gap and enable a new hardware design methodology, as presented in Chap. 3. Finally, Sec. 2.4 briefly reviews SMT solving (SMT = Satisfiability Modulo Theories) which is a class of decision procedures that are the basis for code optimizations in our hardware design flow.

# 2.1 Electronic System Level

The complexity of today's circuits poses great challenges for design and verification productivity, in particular at the *Register-Transfer Level* (RTL). Technology enhancements allow us to implement more complex designs. However, the current design and verification methodologies do not scale with the growing design complexity. This is mainly due to the lack of new abstraction levels above the RTL, preventing an increased productivity. The *Electronic System Level* (ESL) aims to establish a new abstraction level above the RTL. In contrast to RTL and lower abstraction levels (gate level, switch level, transistor level etc.) the ESL, as of today, is not clearly defined. To date, there is no common, agreed definition of the ESL.

Modeling systems at the ESL before actually implementing them pursues the goal of reducing time to market by arriving at a feasible system architecture faster. [3] describe ESL design goals as follows: "The utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner, while meeting necessary constraints."

An ESL model captures the desired functionality abstractly, more or less independent of the implementation. The designer chooses the required amount of detail depending on the system-level behavior and functionality that is modeled. We call any model that is more abstract than an (RTL) implementation an ESL model. An ESL model may describe a simple model of a bus system or an abstract model of a System-on-Chip (SoC). The model of the bus aims to model a correct arbitration and routing of messages by ensuring a correct implementation of the protocol. The model of the SoC is designed to test firmware and inter-module communication. The main difference between these

models is not only the scope of the model, it's more in the modeled amount of detail. The model of the SoC abstracts anything that is not required to develop the firmware. For example, the bus connecting the components of the SoC does not model the bit- and timing-accurate protocols and implements only the routing of the messages. The bus and the SoC model focus on different aspects and describe the functionality on different abstraction levels. It is the task of the designer to choose the appropriate abstraction level for his purpose.

We describe in Sec 2.1.1 how systems are modeled at the ESL and introduce the core concepts of system-level modeling, such as transaction-level modeling. In practice, the C++ library SystemC is is the most common way of modeling the ESL. We cover the core ideas of SystemC briefly in Sec. 2.1.2. For design exploration and virtual prototyping, ESL modeling is already widely adopted in the industry. Sec. 2.1.3 provides an overview of ESL design methodologies currently used in industrial practice. The ESL is, however, barely used as the golden design model for the hardware design process. This is due to a semantic gap, as explained in Sec. 2.1.4.

### 2.1.1 Modeling Systems

In this section, we explain how systems are modeled at the ESL. As opposed to the RTL, ESL models may exist at various levels of abstraction, even for the same design. Depending on the application domain, the understanding of what is specified by the system level, may vary. In order to have a common understanding, in the context of this work, we provide a definition of our understanding of the system level.

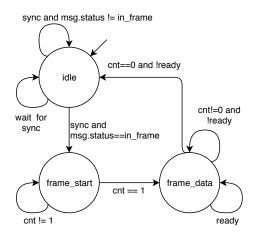

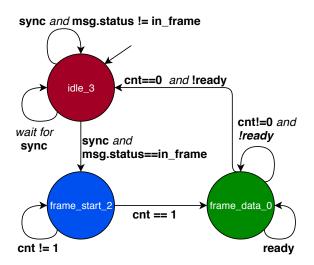

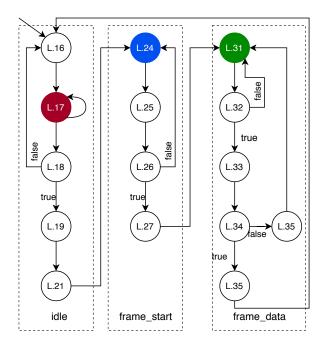

**Definition 1.** (System-level model). A system-level model is composed of modules that communicate with each other. The model may be executable, i.e., it may be simulated in order to analyze its behavior. Communication is modeled on the transaction level as blocking message passing. The behavior is described as a time-abstract, word-level description and the behavior of each module is described as an FSM. The finite state machines of the modules send each other messages based on synchronization events. The outputs are defined as a function of the current state and inputs. The behavior of the entire system level is defined by an FSM that results from an asynchronous composition of the individual FSMs (cf. Def. 23). □

As mentioned in Def. 1, the behavior of each module is described in terms of a *Finite State Machine* (FSM). The asynchronous composition of the FSM allows for a modeling of all interleavings of messages being passed between the modules, and ensures capturing the full behavior of the system-level model. Due to the untimed behavior of the system-level model, each module is allowed to run at its own speed, in the context of system-level modeling this is also called temporal decoupling. In order to exchange a message between two modules they need to synchronize through a handshake. In the executable model this handshake is implemented with events.

The system-level model, as defined in Def 1, is also referred as transaction-level model and constructing executable models at the transaction level is denoted as Transaction-level Modeling (TLM). This term was coined in the early 2000s by the Electronic Design Automation (EDA) companies. TLM aims to model the communication components of

the system, especially the bus systems. The core idea of TLM is to separate communication from computation [4].

For example, consider modeling a synchronous bus system at the RTL. This is done by modeling the different signals (e.g., clock, control, address or data) and the respective time behavior of the signals, as defined by the bus protocol. As a consequence, the RTL model is cycle-accurate and bit-accurate. The transaction-level model abstracts from implementation details such as how control and data are represented by logic signals and how these signals are timed according to the specified bus protocol. It instead models the bus communication in terms of abstract data transfers called *transactions*.

As noted, the core idea of TLM is to separate communication and computation. The bus is abstracted to a so called *Channel*, i.e., a single module specifying the routing and arbitration between communicating components. In contrast to the RTL, the time and pin-accurate protocol is abstracted and sending and receiving is modeled by a distinct event-based handshaking. This results in a vast increase of simulation speed compared to the RTL model.

In TLM, the computational part responsible for data processing can be described without the micro-architecture of an RTL model. Instead, the behavior of the component is described by an algorithm, analogous to a software function. This data processing model is called an *algorithmic model*.

The term TLM is misleading, because, as opposed to the RTL, the transaction level does not describe a distinct level of abstraction. The abstraction of the RTL has a clear semantics. It describes the desired behavior by means of register-transfers. The transaction level lacks this clear semantics. For example, the communication can be modeled time- and pin abstract and the computation pin- and cycle-accurate, and vice versa. This results in different possible model abstractions with different semantics. In practice, every model that is more abstract than the RTL is considered to be a transaction-level model and time behavior is modeled at various accuracy levels. Hence, the notion of a "level" does not fully apply and TLM is considered more a modeling technique. In TLM, the level of abstraction is dependent on the use case.

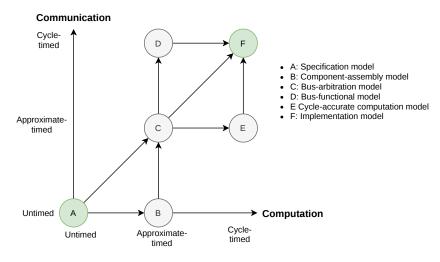

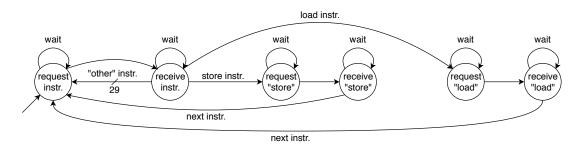

Figure 2.1: Abstracting time in TLM [4]

Fig. 2.1 shows different levels of abstraction when modeling time in TLM: Untimed,

Approximately-timed, and Cycle-timed. An untimed model describes the behavior without any notion of time, whereas approximate-timed adds an estimated timing behavior without the need to completely match with the real time behavior. The cycle-timed model exhibits the exact timing behavior. We may describe computation and communication with different notions of time. The untimed model is denoted as the *Specification Model* and the cycle-timed is denoted as the implementation. The other models result from combining different abstraction levels. For example, "E"in Fig. 2.1 is a model with a cycle-accurate timing behavior for computation, i.e., all the clock events are simulated, combined with approximately timed communication behavior.

According to Def. 1, we only consider the specification model when we talk about system-level models. The definition also states that a system-level model has to be executable. The industry standard for executable system-level designs is SystemC [5]. The next section gives an overview on SystemC.

### 2.1.2 SystemC

In this section we briefly introduce the core concepts of SystemC. As mentioned in Sec. 2.1.1, we consider system models described at different levels of abstraction. SystemC is a software library implemented in C++ and allows to model any desired level of detail as mentioned in Sec. 2.1. In the scope of this work, we are focusing on untimed system-level models. We discuss only the relevant components for modeling on this abstraction level. For a more detailed introduction on SystemC we would like to refer to [6] or [7].

The development of SystemC started in the late 90s, with preliminary efforts from both, academia and EDA companies (e.g., SpeC [8] and Handel-C[9]). In 1999 the Open SystemC Initiative (OSCI) formed and started coordinating the development of SystemC. Due to the participation of major EDA and semiconductor companies in the initiative, SystemC quickly became the dominant language for describing system-level models. Version 1.0 of SystemC was released in 2000 and it primarily rebuilt the functionalities of RTL languages, to allow for fast RTL simulation by native execution rather than by a simulation engine that interprets VHDL or Verilog like, e.g., ModelSim™ [10]. A SystemC model is compiled together with a process scheduler and a simulation engine into an executable simulation program for the host computer. Executing native code delivers higher simulation performance compared to an interpreting simulator, and it also allows employing standard software debugging technology. Over time, SystemC has been continuously extended with transaction-level features [4, 11] and version 2.0 was standardized by the IEEE [12] in 2005. The new version provides features that allow to abstract from certain implementation details (e.g., timing) resulting in faster simulation models.

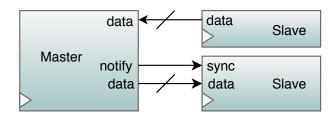

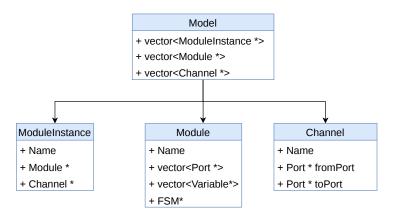

Figure 2.2: Structure of a SystemC TLM model

In SystemC, a C++ class hierarchy models the structural composition of modules and their behavior into a system of concurrent processes. The SystemC library provides a

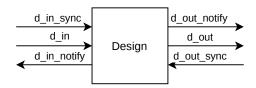

scheduler for simulating the concurrent execution of the processes. Fig. 2.2 provides an overview of the structure of a SystemC model. The structure of the model is defined by instantiating objects of the module class. The designer may add input / output ports by instantiating a port object within the class. The modules can exchange messages between each other by connecting the ports through channels. Channels are an object structure specifically designed to connect ports and to specify a communication protocol.

For example, let us consider a channel implementing communication through a FIFO buffer (FIFO =  $First\ In\ - First\ Out$ ). A port connected to this channel can write (read) a value to the FIFO, if and only if the FIFO is not full (empty). Otherwise, the execution of the module is blocked (resp. has to wait) until the FIFO is free.

The behavior (i.e., the FSM) of each module is specified by providing methods to the module class. By using SystemC-specific macros within the constructor the method is linked to the scheduler. When the binary is executed, the scheduler calls the methods upon events and thereby models the behavior of the modules and the overall system. Methods may alter state variables of the class or assign values to output ports. A method that is registered to the scheduler is called a process. There are different types of processes in SystemC, which differ semantically in the concepts they intend to model. In this scope we are only going to use a *thread* process, that specifies the desired behavior within an infinite while(true) loop.

The provided scheduler implements an event-driven simulation algorithm, concurrently executing the processes, in order to model asynchronous behavior. The correct asynchronous execution of the processes is ensured by the simulation algorithm. The core idea of the scheduler is the following: At the start of the program all threads are marked as "pending" for execution. The scheduler randomly chooses a thread that is marked as pending and executes it until it is blocked by a communication request. In this case, the thread is marked as "suspended" until the desired event occurs. Returning to the example of the FIFO, a thread that writes to the FIFO is blocked, if the FIFO is full. The thread is suspended until a notification from the FIFO is received. Upon notification, the suspended thread is marked as "ready" for execution. After the scheduler executed every thread marked as pending, all threads marked as ready are then again marked as pending. The simulation continues until the simulation is stopped by the user or there is no more thread marked as pending.

In practice, suspending threads is used to enforce a specific execution order of threads. However, we assume an untimed asynchronous behavior and each thread may run at it's own speed. The threads only need to synchronize, if they want to exchange a message. From a simulation point of view, the thread keeps the priority, i.e., it keeps executing, until it communicates. Every communication results in an event based handshaking with the communication partner and gives other threads the possibility to execute. For untimed processes the execution order results from the handshaking of the processes. Hence, every process may run at its own speed. In case of an approximate or cycle-accurate timing model the execution order depends additionally on some notion of time. Processes may execute after a specific number of clock ticks (as in hardware). Here, the progress of time is modeled by events and a process is suspended until the desired number of cycles has passed. However, because we are only interested in untimed models, we always consider blocking behavior as related to communication.

In Chap. 3 we provide a basic example of a System C module. Later on, Sec. 4.4 intro-

duces SystemC-PPA, a subset of SystemC, used to efficiently model a system according to Def. 1. In the following section we are going to explain how SystemC is used in industrial practice.

#### 2.1.3 Design Flows

In this section, we explain how the ESL and the language SystemC is currently used in industrial design flows. There are two main use cases for ESL models: *High Level Synthesis* (HLS) and *Virtual Prototyping* (VP). Furthermore, we will talk about the current limitations of these flows, which are mostly related to the *semantic gap*.

#### Virtual Prototyping

In virtual prototyping the designer models the desired behavior of the system, e.g., an SoC. There are two dominating use cases for virtual prototyping. By providing an early prototype of the hardware, the respective software development can start before the actual hardware is implemented. However, because the prototype is not used as a golden reference in the following hardware design process, the hardware model is rarely functionally sound w.r.t. the resulting RTL implementation.

A second use case of a virtual prototype is design exploration. Here, different architecture types, bus protocols and implementations of algorithms are explored and evaluated. The goal is to estimate the resulting performance, throughput and power consumption of the hardware design. Furthermore, within design exploration the task of partitioning is performed. The designer decides which part of the functionality is implemented in hardware and which part is implemented as software. The benefit of virtual prototyping, compared to RTL, is that it allows for quick architectural changes.

#### High Level Synthesis (HLS)

Synthesis, in the domain of digital hardware, is, in the understanding of most people, the process of translating an RTL model into a functionally equivalent gate-level model or, respectively a gate-level model into a corresponding transistor-level model. With the upcoming of the ESL and SystemC, noticeable effort has been put towards synthesizing RTL from ESL descriptions. As of today, HLS is mostly used in the context of digital signal processing in complex ASIC and FPGA designs. As described above, a core concept of TLM is the separation of computation and communication. HLS synthesis tools are strong in synthesizing the algorithmic descriptions into a digital design.

The algorithms are described and tested at the ESL. Most synthesis tools accept a description as a function in a C style language. The function has to have a deterministic and stateless behavior. The result must be a function of the provided parameters only, not of the internal state. Such a function cannot describe an FSM. Using HLS in a top-down design flow has two benefits: First, it allows for a very abstract, algorithmic description without the need to worry about micro-architectural decisions (e.g., pipelining) or timing. Second, the immensely increased simulation speed at the ESL allows for a more thorough verification of the implemented algorithms compared to RTL simulation.

Besides functional design goals HLS tools are able to consider also non-functional design goals such as timing, area and performance. In order to meet these goals, various

optimization strategies (e.g., loop unrolling, pipelining, rescheduling) can be applied. The resulting RTL description behaves equivalently with respect to the I/O behavior of the algorithm function. It is possible to use equivalence checking techniques to prove equivalence between the algorithm and the resulting RTL implementation.

However, these tools are less suited for synthesizing state machines. When synthesizing algorithms it is always possible to match up the I/O signals of the ESL and the RTL models and thereby establish a sound relationship. This is, however, not possible for FSMs and communication protocols. In this case, the RTL timing as well as the logic signals are abstracted away at the ESL. A refinement step is required, specifying how the abstract objects of the ESL are related to the generated RTL. This problem is called semantic gap, which is discussed in more detail in Sec. 2.1.4.

To date, there is no commercially available technique to establish a sound relationship between a TLM SystemC model and an RTL model. Within the scope of this work we will use a technique, as presented in [13, 2] that allows to build such a sound relationship for communication protocols and FSMs. In Chap. 4 we will discuss the theory of Path Predicate Abstraction, as introduced in [13], that provides the means for building such a relationship. In Chap. 3 we will show how this relationship can be established in practice.

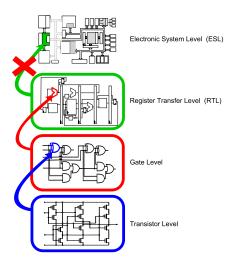

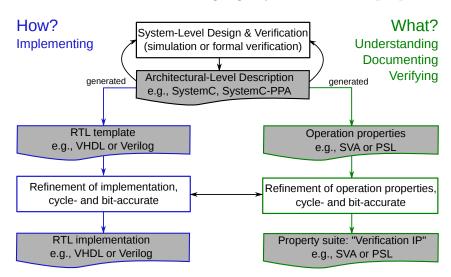

#### 2.1.4 Semantic gap

This section discusses the problem of the semantic gap between ESL and RTL in more detail. In Fig. 2.3 the relationships between the different abstraction levels are illustrated. A new abstraction level is established only, if it has a well defined (i.e., sound) relationship with lower abstraction levels. If this is the case, the new abstraction level can be used for design and verification. Otherwise, the abstract model lacks clear semantics w.r.t. the physical circuit. The core idea of sound abstraction levels is that verification results of a sub-circuit, obtained at a lower abstraction level, should not need to be verified again at a higher abstraction levels. Let's assume that there exists a verified transistor implementation of an AND gate. At the gate level it is now possible to use the more abstract AND gate for further design verification. There is no need to re-verify the transistor implementation of the AND gate at the gate level. If there exists confidence in the relationship between two abstraction levels then it is not necessary to use the lower level for design sign-off.

As shown in Fig. 2.3, the lowest considered level is the transistor level. The transistor level is simulated (e.g., with SPICE [14]), in order to build confidence that a transistor netlist realizes the intended functionality correctly. Such netlists may describe a Boolean operator (e.g., and or not) or a binary storage element (e.g., D-FlipFlop). At the gate level an abstract representation of the operators and storage elements is used (e.g., AND-gate or NOT-gate). There is no more need to model the behavior of the individual transistors. Here, the sound relationship results from an exhaustive simulation at the transistor level.

The gate level is a netlist describing the actual Boolean representation of the circuit or device. It consists of combinational blocks and storage elements in between. The gate level can be seen as a structural implementation of Boolean formulae. The level above the gate level is called the *Register Transfer Level* (RTL).

The RTL models the functional behavior of digital circuits. The main difference to the gate level is that it allows to describe behavioral models. It relates well to the theoretical

Figure 2.3: Abstraction levels for circuit descriptions

model of a *Finite State Machine* (FSM). An FSM models the behavior only in terms of output and register changes as functions of the input and state. The gate-level details, i.e., how the change is realized by a combinational circuit, is abstracted away, to a large extent.

In order to show that the RT level is sound w.r.t. the gate level a formal Equivalence Check (EC) is used. The EC ensures that a gate-level netlist correctly implements the desired functionality. This allows to abstract from gate-level details and use the more abstract RTL description. Due to these methods, it is possible to show that RT-, gate-and transistor-level behave equivalently for identical input sequences. We call this "the chain of trust", because designers trust the higher abstraction level to be suitable for design and verification.

However, EC techniques cannot be employed to establish a sound ESL model, because there is no notion of equivalence that can be easily applied in this context. This problem is referred to as the "semantic gap". As implied by the name, functional descriptions at high levels of abstraction do not have a well defined semantics w.r.t. the RTL and, as a result, to the physical circuits. However, the problem does not result from a lack of standardization of ESL descriptions. It is a theoretical problem of describing a sound relationship between the bit- and cycle-abstract ESL descriptions and the RTL.

A system engineer models large functional blocks as modules with event-driven communication. This allows modeling the overall behavior of the system without the need to worry about synchronization and details of any specific communication protocol. However, implementing such functionalities at the RT level requires an important refinement step. This refinement step forces the engineer to make major RT design decisions such as making area/performance trade-offs, selecting communication protocols, employing pipelining, etc. An automated synthesis, as described in Sec. 2.1.3, is in most cases not possible, or at least unwanted, because this takes away many of the RT design decisions.

A notion of equivalence, as defined for the RTL and gate level, does simply not apply in case of the ESL and the RTL. Nevertheless, a formal relationship between these levels is necessary to establish trust in the ESL and use it as the new abstraction level for design sign-off. In [13],[2] and [15, 16] a new formalism has been developed, specifically tailored

for the purpose of describing such a relationship and, thereby, of closing the semantic gap. This formalism is described in Chap. 4 and adapted in the scope of this work in order to fit a new top-down design flow called *Property-Driven Development* (PDD).

# 2.2 Model Checking

Model checking, also referred as property checking, aims to formally prove or disprove, with fully automatic methods, whether a digital design fulfills a specific property. The behavior of the design is formalized by a sequential model and the desired property is formalized with a temporal logic expression. The task of a model checker is to prove that the specified property holds on the design. As opposed to simulation, the proof mechanism is based on mathematical methods and the model checker does not apply stimuli and assert responses. Instead, the design model and the property together form a computational verification model and the result is computed by an algorithm.

Model checking allows to verify hardware (or software) with tools providing frontends for common hardware description languages (e.g., VHDL and Verilog) or common software programming languages. The properties are formulated in specific property languages such as *Property Specification Language* (PSL) [17] and *System Verilog Assertions* (SVA) [18].

First, we explain how digital circuits are formalized as sequential models by introducing two different automata formalisms: Finite State Machines and Kripke Models in Sec. 2.2.1. The desired properties are formulated by a specific form of temporal logic expression, as explained in Sec. 2.2.2. There are different model checking techniques, of which, within the scope of this work, interval property checking plays an important role. We explain the idea of this technique in Sec. 2.2.3.

### 2.2.1 Sequential model

In the following, we explain how the behavior of digital circuits can be formalized by formal, sequential models. Digital circuits are composed of storage elements and combinational blocks. The combinational behavior of the circuit can be described by Boolean formulas. However, storage elements cannot be represented by Boolean logic. Instead, various formalisms for automata are used, also known as state machines or transition systems.

These automata, represent the value of the storage elements by a state and are often visualized as a state transition graph (STG), a directed graph with a node for each state, with an edge for each transition, and with a labeling dependent on the specifics of the automaton formalism under consideration. The terminology used in graph theory also partly applies in the context of automata. The reachable states are states that are reachable by a path starting at the initial state. The sequential depth is the length of the longest cycle-free path from the initial state to any reachable state.

#### Finite State Machine

The digital behavior of an electronic circuit can be described by a discrete and deterministic *Finite State Machine* (FSM). In the scope of this work we are using *Mealy-type*

FSMs. Moore-type FSMs only differ in the definition of the output function  $\lambda$ , which for Moore-type FSMs is a function of only the set of states, i.e.,  $\lambda: S \mapsto Y$ .

**Definition 2** (Finite State Machine). A deterministic Finite State Machine (FSM) is a 6-tuple  $M = (S, I, X, Y, \delta, \lambda)$  with:

- a finite set of states S,

- a non-empty set of initial states  $I \subseteq S$ ,

- an input alphabet X (a finite set of input values),

- an output alphabet Y (a finite set of output values),

- a transition function  $\delta: S \times X \mapsto S$ ,

- and an output function  $\lambda: S \times X \mapsto Y$ .

Sequential circuit descriptions, e.g., RTL descriptions, can be interpreted as an FSM where the set of states, the input alphabet, and the output alphabet are encoded by vectors of Boolean values. The transition function,  $\delta$ , and the output function,  $\lambda$ , are realized in the circuitry as Boolean operations on these vectors.

**Definition 3** (Encoded FSM). An encoded FSM is an FSM,  $M = (S, I, X, Y, \delta, \lambda)$ , where:

- The state set S is an encoding over a vector V of Boolean variables referred to as state variables,  $V = \langle v_1, v_2, \dots, v_n \rangle$ .

- The input alphabet X is an encoding over a vector of Boolean variables referred to as inputs,  $X = \langle i_1, i_2, \dots, i_m \rangle$ .

- The output alphabet Y is an encoding over a vector of Boolean variables referred to as outputs,  $Y = \langle o_1, o_2, \dots, o_k \rangle$ .

- The transition function  $\delta = \langle \delta_1, \delta_2, \dots, \delta_n \rangle$  is a vector of Boolean functions, where  $\delta_j$  is a next-state function for the state variable  $v_j$ .

- The output function  $\lambda = \langle \lambda_1, \lambda_2, \dots, \lambda_k \rangle$  is a vector of Boolean functions, where  $\lambda_j$  is the output function for the output  $o_j$ .

It follows that for an encoded FSM each unique value of the state vector, input vector and output vector correspond, respectively, to a state, an input symbol and an output symbol. Note that an encoded FSM will have  $2^n$  states (and  $2^m$  input symbols and  $2^k$  output symbols). However, not all of these states are necessarily reachable from an initial state. Finding and representing the set of actually reachable states is one of the main concerns when applying formal methods.

#### Kripke Model

In this section we introduce Kripke models, an automaton formalism widely used in computer science. It is used, e.g., for defining temporal logic languages, as introduced in Sec. 2.2.2. In the scope of this work, it is also used in Chap. 4 to establish a sound relationship between ESL and RTL.

**Definition 4** (Kripke Model). A Kripke model is the quintuple K = (S, I, R, A, L) with:

- a finite set of states S,

- a non-empty set of initial states  $I \subseteq S$ ,

- a left-total transition relation  $R \subseteq S \times S$ ,

- a set of Boolean atomic formulas A,

- and a valuation function  $L: A \mapsto 2^S$ .

Note that no input or output is defined for a Kripke model. Instead, a valuation function (also referred to as a labeling function) is defined which gives each state a valuation (truth value) to the set of atomic formulas. In a state  $s \in S$  the atomic formula  $a \in A$  has the value true if  $s \in L(a)$  and the value false if not. Two Kripke models are sequentially equivalent if any of the initialized paths in one model produces a sequence of labels/valuations which can also be produced by an initialized path of the other, and vice versa.

A Kripke model can be derived from an FSM, and thereby also from an electronic circuit. Let  $M = (S_M, I_M, X_M, Y_M, \delta_M, \lambda_M)$  be a Mealy-type FSM. Then, a derived Kripke model K has the following state transition behavior.

- Set of states:  $S \subseteq S_M \times X_M \times Y_M$ :  $S = \{(s_M, x_M, y_M) | y_M = \lambda(s_M, x_M)\}$

- Set of initial states:  $I \subseteq I_M \times X_M \times Y_M$ :  $I = \{(s_M, x_M, y_M) \mid s_M \in I_M \land y_M = \lambda(s_M, x_M)\}$

- Transition relation:  $R = \{((s_M, x_M, y_M), (s'_M, x'_M, y'_M)) \mid s'_M = \delta_M(s_M, x_M) \land y'_M = \lambda_M(s_M, x_M)\}$

Note that the deterministic behavior of an FSM, due to the transition function  $\delta$ , is reflected in the Kripke model by the fact that every state,  $(s_M, x_M, y_M)$ , has only transitions to next states with a unique FSM state component  $s_M'$ ; however, it has transitions to all states with that FSM state component  $s_M'$ , i.e., with any input component  $x_M'$ .

The atomic formulas A and the labeling function L of the derived Kripke model need to be chosen such that the properties we would like to prove on the model can actually be formulated. In principle, all states, inputs and outputs of the original FSM can be distinguished by the labeling function of the Kripke model and thus can be reasoned over.

#### 2.2.2 Linear Temporal Logic

Temporal logic languages allow us to reason over logical properties for the sequential behavior of automata. In practice, standardized languages such *Property Specification Language* (PSL) [17] and *System Verilog Assertions* (SVA) [18] are used to formalize temporal logic. They provide an extended syntax for describing temporal logic expressions and they can be mapped to formal temporal logic languages, as presented here.

In this section, we introduce the language *Linear Temporal Logic* (LTL), as proposed in [19]. There are other forms of temporal logic such as Computation Tree Logic (CTL) [20] and CTL\* [13]. These languages and the according model checking techniques, however, are not required in the scope of this work.

LTL extends the set of Boolean logic operators by a set of temporal operators: X ("next"), G ("globally"), F ("finally"), U ("until"), W ("weak until"), R ("release"), to express logical properties quantified over time. LTL formulas describe a set of paths in the considered Kripke model. If an LTL formula is satisfied in all paths starting from a specific state, we may say that an LTL formula holds for this state.

**Definition 5** (LTL Syntax). The legal syntax of LTL is recursively defined by:

- 1. Every Boolean atomic formula,  $a \in A$  is an LTL formula,  $\phi$ .

- 2. If  $\phi_1$  and  $\phi_2$  are LTL formulas then:  $\neg \phi_1$ ,  $\phi_1 \lor \phi_2$ ,  $\mathsf{X}\phi_1$ ,  $\mathsf{G}\phi_1$ ,  $\mathsf{F}\phi_1$ ,  $(\phi_1 \mathsf{U} \phi_2)$ ,  $(\phi_1 \mathsf{W} \phi_2)$ ,  $(\phi_1 \mathsf{R} \phi_2)$  are also LTL formulas. ( $\land$ , true, false can be expressed using  $\neg$  and  $\lor$ .  $\square$

**Definition 6** (LTL Semantics). For a considered Kripke model, let  $\phi_1$ , and  $\phi_2$  be LTL formulas,  $\pi_i = (s_i, s_{i+1}, \ldots)$  be an infinite path from  $s_i$ ,  $\pi \models \phi$  mean that the LTL formula  $\phi$  is satisfied by the path  $\pi$ .

- $\pi_i \models a \iff s_i \in L(a)$

- $\pi_i \models \neg \phi_1 \Longleftrightarrow \pi_i \not\models \phi_1$

- $\pi_i \models \phi_1 \lor \phi_2 \iff (\pi_i \models \phi_1) \ or \ (\pi_i \models \phi_2)$

- $\pi_i \models \mathsf{X}\phi_1 \Longleftrightarrow \pi_{i+1} \models \phi_1$

- $\pi_i \models (\phi_1 \cup \phi_2) \iff$  there exists  $j \geq i$  such that  $\pi_j \models \phi_2$  and for all  $i \leq k < j$ ,  $\pi_k \models \phi_1$

- $\mathsf{F}\phi_1 \equiv \mathsf{true}\,\mathsf{U}\,\phi_1$

- $G\phi_1 \equiv \neg(F\neg\phi_1)$

- $(\phi_1 \mathsf{W} \, \phi_2) \equiv (\phi_1 \mathsf{U} \, \phi_2) \vee \mathsf{G} \phi_1$

- $\bullet \ (\phi_1 \mathsf{R} \, \phi_2) \equiv \phi_2 \, \mathsf{W} \, (\phi_2 \wedge \phi_1) \qquad \qquad \Box$

#### 2.2.3 IPC

In this section we introduce Interval Property Checking (IPC), as proposed in [21]. It is a SAT-based model checking technique, rooted in the industrial developments of the 1990s. With this model checking technique, it is possible to produce globally valid, unbounded proofs. It uses Kripke models as the sequential model and the desired property is formulated by a restricted form of LTL formulas (cf. Sec. 2.2.2) known as *interval properties*. An interval property describes behavior over a finite time interval and the temporal logic expression is formulated in form of an implication.

**Definition 7** (Interval Property). An interval property  $\phi$  is an LTL formula of the form  $G(A \to C)$  where both sub-formulas A and C, referred to as assumption and commitment, respectively, describe behavior over a finite time, i.e., the only temporal operator that may be used is the next operator, X.

We further refer to interval properties as operation properties, because in practice they are often used to specify "operations" of the model under consideration. We provide a formal introduction of operations in Sec. 4.2.

The computational model for IPC is related to *Bounded Model Checking* (BMC) [22]. In BMC properties are formulated from a specific starting state and are restricted to describe behavior over a bounded time interval. Here, the sequential model, can be mapped to Boolean logic by "unrolling" it over a finite time window. The inputs of the circuit are left as free input to the SAT problem.

However, in order to have an unbounded proof that is not restricted to a certain period of time, the unrolled model has to cover the entire reachable state space. This can be done by unrolling the model from the initial state with a period greater than or equal to the sequential depth of the circuit. This is, in most cases, not feasible due to the computational complexity of the SAT problem as well as the complexity of calculating the sequential depth in the first place. In a nutshell, BMC gives bounded proves for properties describing a finite time interval.

The computational model for IPC is, with one important exception, the same as for BMC. The difference is that in IPC no assumption is made about the starting state, i.e., the starting state is left as a free input in the SAT problem. In other words, IPC assumes a *symbolic initial state*. This is why the properties proven on this model are valid for an arbitrary concrete starting state. This is why IPC provides *unbounded proofs* for properties describing a finite time interval.

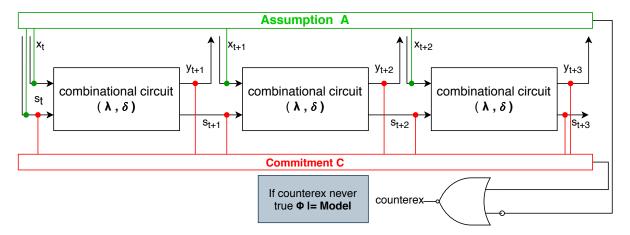

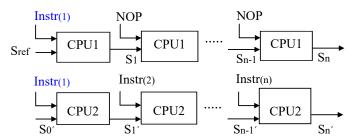

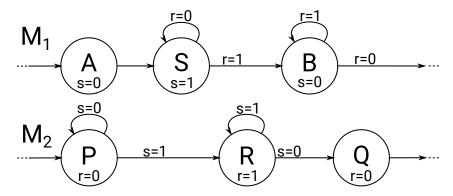

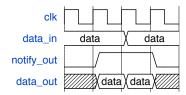

The proof computation for a property,  $\phi$ , is illustrated in Fig. 2.4. Property  $\phi$  expresses an interval property over the finite interval of three clock periods. It uses a nested *next* operator X at most three times.

The combinational logic is unrolled three times and the starting state,  $s_t$  and the input in each clock period,  $x_t$ ,  $x_{t+1}$ , and  $x_{t+2}$  are left as free input with respect to the assumption A. Every value that is not a contradiction to the assumption is considered to be a valid value for the input and the initial state. The property is disproved if any set of values fulfills the negation of the commitment C. This set is, then, a counterexample of the property. If no such counterexample exists, the property is valid for the model under consideration.

Due to the fact that the starting states are modeled as free inputs, all states are considered as possible starting states. This results in an over-approximation of the state

Figure 2.4: Proof computation for interval properties

space, because not all considered states are necessarily reachable in the design. This might result in "false negatives" or "spurious counterexamples". These are counterexamples starting from an unreachable state of the design. However, "false positives" are not possible, because the property is proven in all reachable and unreachable states. The term "positive" refers to a successful proof of a property and "negative" to an unsuccessful one that returned a counterexample. Therefore, the computational model of IPC is conservative.

The problem of false negatives is solved in IPC by proving strengthened invariants for the design. Either the counterexample is manually inspected and assertions are formulated for the design or automatic methods, e.g., as proposed in [23], are used.

If the properties are formulated such that they describe important "operations" of the design, false negatives can be avoided, to a large extend. An operation, in the context of digital hardware, describes sequences of register transfers with a common purpose. An operation could be, e.g., an instruction of a simple processor, or, the functionality triggering the protocol for the transmission of a message over a bus.

These operations tend to have sparse, manageable inter-dependencies. Note that the correct execution of a processor instruction is, in most cases, independent of previous behavior. Interdependencies between instructions can, for example, occur in pipelined designs if forwarding of datapath variables is required to resolve hazards. Here, the reachable values, at the time of the operation, are determined completely by previous operations.

A designer, usually, thinks about the behavior of design in terms of operations (e.g., an ADD instruction as one operation). The process of creating and proving the operation properties is, from an abstract point of view, closely related to the design process. Also, the verification engineer needs to identify the operations to create the properties. In that sense, the operation properties formalize and document the operations of the design. We consider IPC to be a white-box approach, because the process of creating the properties requires to reason on internal signals. This is in contrast to black-box approaches like simulation-based verification. Here, the verification engineer is not required to understand the internals of the design.

During the process of creating the properties an abstract engineering view of the design is formalized. Even for complex circuits, from our experience, the overall functionality

can be well understood in terms of operations. Formulating properties for important operations of the design is common practice in industry and well supported by prover technology tailored for this purpose such as in [21, 24, 25]. The high-quality of the verification results from the established validity of the individual operations.

# 2.3 Complete Interval Property Checking

In the context of simulation-based verification methods certain coverage metrics, such as code coverage and functional coverage, are used to measure which portion of the design is verified. These metrics, however, do not apply in the context of formal methods. Proving a formal property on a design shows that the property is valid for all possible input stimuli. A measurement, reflecting which portion of the design behavior is covered by the proven property, is still needed.

This chapter presents an absolute cover measure, that is a formal criterion for the *completeness* of a set of interval properties. It was first developed in [26, 27]; [28] later independently obtained a similar result. It is ensured that a set of properties fulfilling this criterion completely describes the output behavior of the design in terms of the design's input.

This chapter briefly summarizes Complete Interval Property Checking (C-IPC) in the terminology and notations of this thesis. For a more comprehensive and illustrated elaboration of this technique the reader may refer to [27]. The chapter is structured as follows: First we will introduce some important notions related to completeness. This formalization is required to introduce the path predicate abstraction in Chap. 4 — the main theoretical foundation for Property-Driven Development. In Sec. 2.3.2 the completeness criterion will be formally defined. Sec. 2.3.3 presents an algorithm to check the fulfillment of this criterion. In practice, this completeness check is computationally tractable even for large designs and it is commercially available [25].

# 2.3.1 Terminology

The behavior over a finite time interval is characterized by the notion of a *sequence* predicate.

**Definition 8** (Sequence Predicate). A sequence predicate is an LTL formula where the only temporal operator used is the next operator, X.

Note that the assumption A and the commitment C of an interval property are examples of sequence predicates. For ease of notation we also define a generalized next operator.

**Definition 9** (Generalized Next Operator). The generalized next operator denotes a finite nesting of the next operator, X. Let  $\phi$  be an LTL formula. The generalized next operator next<sub>k</sub> is defined by:  $\operatorname{next}_0(\phi) := \phi$ , and  $\operatorname{next}_i(\phi) := X(\operatorname{next}_{i-1}(\phi))$  when i > 0.

The completeness check is tightly coupled with the concept of describing the design behavior with *operations*, as described in Sec. 2.2.3. The basic idea is the following: A set of properties is considered complete if and only if every input sequence and every output

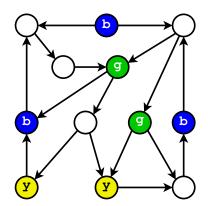

Figure 2.5: Example model to illustrate formalisms

sequence of the FSM under verification is fully described by a sequence of operations. For the following discussion, operations are formalized by means of interval properties augmented with a length.

**Definition 10** (Operation). An operation O is a set of finite path segments of length l in a Kripke model K characterized by the pair (P,l) of an interval property,  $P := G(A \to C)$ , with  $P \models K$ , and the operation length l. A path segment,  $(s_0, \ldots, s_l)$ , is element of O if and only if for any path  $\pi = (s_0, \ldots, s_l, \ldots)$  it holds that  $\pi \models A$ .

In other words, the pair (P, l) characterizes path segments with l transitions (between l+1 states). These segments are prefixes of one or more paths on which the assumption A (and, hence, the commitment C) holds. The pair (P, l) can be understood as the specification of an operation. From now on, when it is clear from the context whether the specification or the actual design behavior is meant, we may refer to both, (P, l) and O, as "operation".

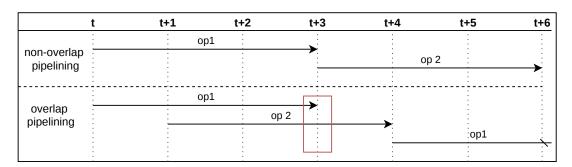

Practically, l specifies the length of the finite behavior of an operation. This means that it describes the number of transitions needed to check an assumption A and to produce an output sequence fulfilling the commitment C of the property. There are special cases where a shorter value for l is chosen. In pipelined designs, for example, the computed results are only visible at the outputs a number of cycles after the operation was issued. A new operation may already be in progress while the current operation is still computing a result. In this case, the length of l is chosen such that the start of the current operation, O, and the start of the new operations align. This is important when considering chains of operations, as explained below.

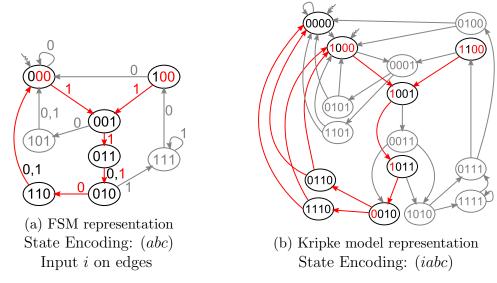

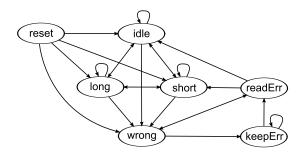

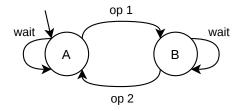

**Example (1)**: Fig. 2.5 shows an FSM and the corresponding Kripke model. We created an example operation (op, 5), such that inputs, outputs and FSM can be distinguished by the labeling of the Kripke model.

The operation is characterized by the property op and the length l=5 for the model of Fig. 2.5. Let op :=  $G(A \to C)$  where  $A := \neg b \land \neg c \land i \land \operatorname{next}_1(i) \land \operatorname{next}_2(i) \land \operatorname{next}_3(\neg i)$  and  $C := \operatorname{next}_1(\neg a \land \neg b \land c) \land \operatorname{next}_2(\neg a \land b \land c) \land \operatorname{next}_3(\neg a \land b \land \neg c) \land \operatorname{next}_4(a \land b \land \neg c)$ .

The path satisfying A are all paths with a prefix matching the states codes (1x00, 1xxx, 1xxx, 0xxx). The reader may verify by inspection of the Kripke model that the paths with prefix (1000, 1001, 1011, 0010) and the paths with prefix (1100, 1001, 1011, 0010) fulfill this condition. The reader may further verify by inspection of Fig. 2.5b that for these paths the commitment C, given by (xxxx, x001, x011, x010, x110), is fulfilled and, hence, the interval property op holds. The evaluation of the operation results in the following path segments. It shows the paths fulfilling A and having a prefix of length l = 5:

```

{(1000,1001,1011,0010,0110,0000), (1000,1001,1011,0010,0110,1000), (1000,1001,1011,0010,1110,1000), (1000,1001,1011,0010,0110,0000), (1100,1001,1011,0010,0110,0000), (1100,1001,1011,0010,1110,1000), (1100,1001,1011,0010,1110,1000)}

```

The completeness criterion relies on sequencing of a set of operations. Each operation has a set of states reachable at the beginning of the operation and a set of states reachable at the end of the operation. In order to fulfill the criterion, it is required that the end of an operation is the start of another. The set of reachable states at the end of an operation are therefore of special interest and are referred to as *important ending states*.

**Definition 11** (Important Ending State). The set of important ending states of an operation O of length l is the set of states  $\{s \mid \exists (s_0, s_1, \ldots, s_l) \in O : s = s_l\}.$

For example, in the operation (op, 5), the important ending states are the states 0000 and 1000. In other words, the set of important ending states of an operation is the set of states reachable at the end of the operation.

**Definition 12** (Important States). The important states of a set of operations are the union of all important ending states of all operations in the set.  $\Box$

In order to create a complete set of properties the verification engineer has to identify important modes of the system. The design behavior is partitioned into operations transitioning between these modes. Hence, the modes describe the important states of the design. In our methodology, the important states are specified in terms of an expression over the RTL state variables. Practically, macros / functions are created for each important state of the design. They are then refined by formulating logic expressions over the RTL state variables. The operation properties are then written by referring to these macros. The starting mode is specified in the assumption A and the ending mode in the commitment C of the property.

# 2.3.2 Completeness Criterion

A property set is considered to be complete if the properties describe the output sequences according to certain *determination requirements*. The determination requirements specify which output signals in the design need to be *determined* under which circumstances. An output signal is determined at a specific time point if and only if its value is described through the property set as a function of the inputs at current and/or earlier time points.

In addition to the outputs, state variables can also be declared as determined. If state variables are declared to be determined at the time of reference, these state variables may be used to express output signals. The expression for determining an output signal's value must be in terms of inputs and/or other determined values.

As an example, let us consider the determination requirement for a data bus with a valid flag "datavalid". If the flag is not set, the data of the bus is irrelevant. The determination requirement for the data signal, "data", is specified as "if (datavalid = true) then determined(data)", assuming that the valid flag has no determination requirements. The determination requirements thereby specify a set of time points for each property considered in the set for which the value of the data bus should be determined. It is defined as a pair  $(s, \sigma_s)$  for a signal s (i.e.,: data bus) and the condition  $\sigma_s$  defines when the signal s is to be determined. The determination requirement is fulfilled if the signal s is determined for any given time point characterized by  $\sigma_s$ .

**Definition 13** (Complete Property Set). A property set  $V = \{P_1, P_2, \dots, P_n\}$  is complete if any two finite state machines satisfying all properties in the set are sequentially equivalent in the signals specified in the determination requirements at the time points characterized by the guards of the determination requirements.

In the scope of this work the properties we consider reason about the labels of a Kripke model. The labeling is chosen such that they discriminate the signals of the RTL design. One way for choosing the labeling is that each RTL signal is represented by its own Boolean atomic formula, e.g., the aforementioned bus is represented by a set of atomic formulas, one for each of the state and data bits.

### 2.3.3 Completeness Check

The completeness of a property set is checked formally, by a proof by induction starting from the initial states. In practice, the initial states are defined by the possible states of the design when the reset signal is asserted. This algorithm has shown to be computationally feasible. The algorithm proves that starting from an initial state that any input sequence drives the design through a sequence of operations, each described by an operation property. The starting point of each operation "mode" is determined by the history of input sequences (i.e., the sequence from reset). The mode is described in terms of expressions over state variables of the system.

The base case of the inductive proof is the reset property which determines the state of the system a finite number of clock cycles after reset. The inductive step is constituted by the other properties of the property suite. It is then ensured that for any input sequence received in any ending state of a previous operation, an operation property exists which determines an ending state of the current operation. In order to ensure that an operation ends in a determined state it is checked whether the operation is a function of only inputs and its starting states.

The basic of idea of *Complete Interval Property Checking (C-IPC)* is implemented by a collection of four tests. These tests can be performed automatically on the set of operation properties. Note that the design is not taken into consideration and the tests are solely performed on the property suite. The user needs to specify:

• the input signals,

- what signals should be determined according to determination requirements,

- a sequencing of operations.

The sequencing is specified by a property graph G = (V, E) where the nodes  $V = \{P_i\}$  are the operation properties and the edges describe their potential sequencing. There is an edge  $(P_j, P_k) \in E$  if the operation specified by  $(P_k, l_k)$  can take place immediately after the operation specified by  $(P_j, l_j)$ . (This is the case if operation  $(P_k, l_k)$  starts in a state that is reached by operation  $(P_j, l_j)$ .) Note that, in principle, the property graph could be determined automatically from the set of operations.

In order to prove the completeness criterion of a set of properties, four checks are performed on the property graph G: a case split test, a successor test, a determination test and a reset test, all described below.

**Example (2)**: In order to practically demonstrate the idea of completeness, a complete set of properties is created for the model shown in Fig. 2.5. First, we need to specify the determination requirements. Here, we only list one requirement for the atomic formula c as (c, true), i.e., it is an unconditional requirement. Atomic formulas a and b are considered internal states and do not need to be determined.

We consider the set of operations:

$\{(long, 5), (short, 3), (idle, 1), (wrong, 4), (readErr, 1), (keepErr, 1), (reset, 0)\}$ The interval properties are defined by:

```

A_{\mathsf{long}} := \neg b \land \neg c \land i \land \mathsf{next}_1(i) \land \mathsf{next}_3(\neg i)

C_{\mathsf{long}} := \mathsf{next}_1(c) \land \mathsf{next}_2(c) \land \mathsf{next}_3(\neg c) \land \mathsf{next}_4(\neg c) \land \mathsf{next}_5(\neg b \land \neg c)

A_{\mathsf{short}} := \neg b \land \neg c \land i \land \mathsf{next}_1(\neg i)

C_{\mathsf{short}} := \mathsf{next}_1(c) \land \mathsf{next}_2(c) \land \mathsf{next}_3(\neg b \land \neg c)

A_{\mathsf{idle}} := \neg b \land \neg c \land \neg i

C_{\mathsf{idle}} := \mathsf{next}_1(\neg b \land \neg c)

A_{\mathsf{wrong}} := \neg b \land \neg c \land i \land \mathsf{next}_1(i) \land \mathsf{next}_3(i)

C_{\mathsf{wrong}} := \mathsf{next}_1(c) \land \mathsf{next}_2(c) \land \mathsf{next}_3(\neg c) \land \mathsf{next}_4(a \land b \land c)

A_{\mathsf{readErr}} := a \land b \land c \land \neg i

C_{\mathsf{readErr}} := \mathsf{next}_1(\neg b \land \neg c)

A_{\mathsf{keepErr}} := a \land b \land c \land i

C_{\mathsf{keepErr}} := \mathsf{next}_1(a \land b \land c)

A_{\mathsf{reset}} := \mathsf{reset}

C_{\mathsf{reset}} := \neg b \land \neg c

```

The example will be used to explain how the four individual tests for establishing completeness are applied and how they ensure the overall completeness of the property set. It will be continued for each test in each test's respective subsection.

# 2.3.4 Case Split Test

The case split test checks, for an arbitrary input sequence, that there exists a chain of operation properties such that the assumption of each property in the chain is fulfilled. In other words, for an arbitrary sequence of inputs there will be a deterministic sequence of operations.

This is ensured by checking that for every operation  $(P, l_P)$  the commitment  $C_P$  of P is covered by the disjunction of the assumptions  $\{A_{Q_j}\}$  of all successor properties  $Q_j$  after  $l_P$  transitions. This implies that, for every path starting in an important ending state of  $(P, l_P)$ , there exists an operation property  $Q_j$  whose assumption  $A_{Q_j}$  describes that path.

Let  $\{A_{Q_1}, A_{Q_2}, \ldots\}$  be the set of assumptions of the successor operations, then the case split test checks whether the implication  $C_P \to \operatorname{next}_{l_P}(A_{Q_1} \vee A_{Q_2} \vee \ldots)$  holds or fails. The assumptions  $A_{Q_i}$  of the property  $Q_i$  are shifted in time to the end of property P so that the first state of  $A_{Q_i}$  coincides with the last state of  $C_P$ .

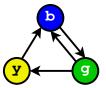

**Example (3)**: Fig. 2.6 shows the property graph as defined previously by the interval properties of our running example. Lets consider the case split test applied to operation (wrong, 4). By inspecting the property graph, the successors operations are identified as readErr and keepErr. The case split tests checks for wrong that the commitment  $C_{\text{wrong}}$  implies that either the assumption  $A_{\text{readErr}}$  or the assumption  $A_{\text{keepErr}}$  holds at the end of the operation, i.e.,  $\text{next}_1(c) \land \text{next}_2(c) \land \text{next}_3(\neg c) \land \text{next}_4(a \land b \land c) \Rightarrow \text{next}_4((a \land b \land c \land \neg i) \lor (a \land b \land c \land i))$ . Clearly, the case split test holds for (wrong, 4).

Figure 2.6: Property Graph

If the case split test succeeds (for all operations), this means that for every possible input trace of the system there exists a chain of operations that is executed. However, this chain may not be uniquely determined. Therefore, the following successor test is performed.

#### 2.3.5 Successor Test

The successor test ensures that the execution of an operation  $(Q, l_Q)$  is completely determined by its predecessor operations  $(P, l_P)$ .

Considering a pair  $(P,Q) \in G$  with a predecessor operation P and a successor operation Q. The test checks whether the assumption  $A_Q$  of Q depends only on inputs and signals determined by P. The problem is translated to a SAT instance by the following steps:

1. The set of signals mentioned in the properties P and Q is duplicated. If a symbol z' is marked with a tick then it belongs to the copy, otherwise to the original set. The first set of signals is used to describe executions of an operation  $(P, l_P)$  followed by operation  $(Q, l_Q)$ . The second set describes operation  $(P, l_P)$  followed by a different operation.

- 2. The same input sequence and the same values for determined state variables are applied to both executions.

- 3. The set of determination requirements  $D = \bigwedge d_i$  is expressed as a conjunction of the determination requirements  $d_i$ . Each  $d_i$  represents one requirement  $(s, \sigma_s)$  expressed as  $d_i = (\sigma_s \wedge \sigma'_s \Rightarrow s = s')$ . Intuitively, this expression states that whenever the guard of signal s is true in one of the executions the signal s must have the same value in both executions.

- 4. Let  $A'_P$ ,  $C'_P$  and  $A'_Q$  be the assumption and commitment of property P and the assumption of property Q, respectively, expressed in the copied signals. The successor test checks the following implication on the SAT instance (with the same input values in each time frame):

$$A_P \wedge C_P \wedge A'_P \wedge C'_P \wedge D \wedge \operatorname{next}_{l_P}(A_Q) \Rightarrow \operatorname{next}_{l_P}(A'_Q)$$

If the implication does hold, then the assumption  $A_Q$  uniquely determines for any input sequence applied after completion of operation  $(P, l_P)$  whether operation  $(Q, l_Q)$  will follow or not (hence the name, "successor test"). In the case that this implication does not hold, there exists an input sequence such that operation property P is executed and the assumption of operation property Q may or may not hold, depending on the other signals mentioned in the properties. This is the case if the assumption  $A_Q$  was written such that it depends on some state variables other than inputs and variables determined by P.

Example (4): For the pair (wrong, keepErr) of the example, the successor test is:

$$A_{\mathtt{wrong}} \wedge C_{\mathtt{wrong}} \wedge A'_{\mathtt{wrong}} \wedge C'_{\mathtt{wrong}} \wedge (c \Leftrightarrow c') \wedge \mathrm{next}_4(A_{\mathtt{keepErr}}) \to \mathrm{next}_4(A'_{\mathtt{keepErr}})$$

The commitment of wrong fully specifies the FSM at time point next<sub>4</sub>. Clearly, the formula holds for this example.

In order to demonstrate the successor test we modify wrong, such that next<sub>4</sub> specifies only states b and c. Now, we add a new successor property to the property graph with the an assumption including a = 0. In this case, the case split test for wrong still holds. Due to the fact that a is not determined at the end of wrong it is not possible to know whether the new property or one of the two original successor properties would trigger at next<sub>4</sub>. Hence, the successor test fails and correctly flags such a set of properties as incomplete.

With the successor test, we ensure that a unique chain of operations for every input trace exists. In the following, we introduce the *Determination Test* that shows that these operations determine the output signals as stated in the determination requirements.

#### 2.3.6 Determination Test

The determination test performs a check whether an operation  $(Q, l_Q)$  and its predecessor operation  $(P, l_P)$ , in turn, fulfills its respective determination requirements. The test creates a SAT instance that evaluates to true if a determination requirement is violated.

This means that a variable required to be determined by Q is actually not a function of the variables P and/or of inputs during the operation  $(Q, l_Q)$ .

As in the successor test, the set of signals is duplicated for both operations Q and P. This technique allows to describe two executions where Q is the successor of P and identical input sequences are applied. The state variables are assumed to be equal and are given the same values, in the time points specified by the guards. Let  $D_P$  and  $D_Q$  be the determination requirements of property P and Q, respectively.

The determination test checks the following implication on the SAT instance (with the same input sequences applied in both executions):

$$A_P \wedge C_P \wedge A'_P \wedge C'_P \wedge D_P \to \operatorname{next}_{l_P}(D_Q)$$

Disproving this implication means that there exists a sequence of input signals and/or signals mentioned in the operation properties such that signals that are supposed to be determined in Q may have different values in different executions of P.

**Example (5)**: In the provided example we only have a single, unconditional determination requirement — c should be determined at all times, i.e,  $D_P = (c \Leftrightarrow c')$ . In our rudimentary example the value of c is explicit at all "time points" of all operations. The determination test clearly holds for the set example.

In reality, the signals to be determined may be vectors whose values are expressed by functions dependent on input and/or other signals at earlier time points. In such cases the determination test will be non-trivial.  $\Box$

#### 2.3.7 Reset Test

The inductive proof is rooted at the reset state. The case split, successor and determination test form the inductive step of the proof with a hypothesis that states: Assuming that an operation  $(P, l_P) \in V$  uniquely determines its ending state, then an operation  $(Q, l_Q) \in V$  exists that uniquely determines the ending state as well as the output sequence of  $(Q, l_Q)$  solely from the ending state of  $(P, l_P)$  and from the input sequence applied during the operation  $(Q, l_Q)$ .

For the reset test, a special *reset property* is required to describe the state after reset. Here, the assumption contains only the reset condition and the test whether reset behaves deterministically and that it fulfills all determination requirements. The construction is similar to the other test. However, the reset property does not have any predecessor properties.

**Example (6)**: The reset operation (reset, 0) specifies the state after reset. It does not refer to the state before the reset condition. Hence, it guarantees that reset can be applied deterministically. Furthermore, the determination requirement is clearly fulfilled;  $C_{\text{reset}} := \neg b \land \neg c$  determines the value of c from the fulfillment of the reset condition until one of the successor operations determines its value (in the next clock cycle).

# 2.4 Satisfiability Modulo Theories

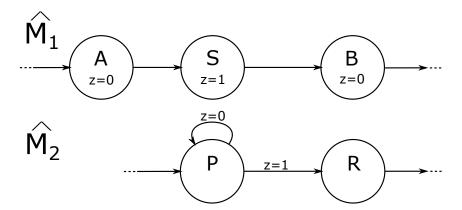

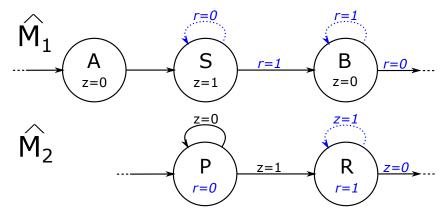

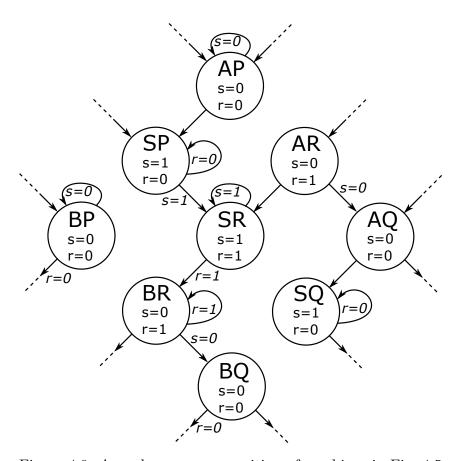

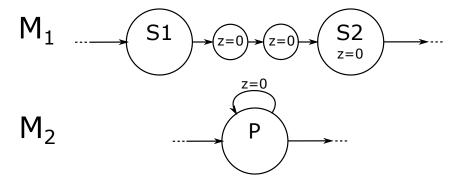

In the context of digital design Boolean formulas and their satisfiability are of special importance. For example, they are used to specify the logic of the circuit or to prove