# Application-Dependent Hardware/Software Cross-Layer Fault Analysis

**Christian Bartsch**

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

Fachbereich Elektro- und Informationstechnik Rheinland-Pfälzische Technische Universität Kaiserslautern-Landau Kaiserslautern

## Application-Dependent Hardware/Software Cross-Layer Fault Analysis

Vom Fachbereich Elektrotechnik und Informationstechnik der Rheinland-Pfälzische Technische Universität Kaiserslautern-Landau zur Verleihung des akademischen Grades

#### Doktor der Ingenieurswissenschaften (Dr.-Ing.)

genehmigte Dissertation

von

### **Christian Bartsch**

geboren in Moers, Deutschland

## D 386

| Dekan                               | : | Prof. Dr. rer. nat. Marco Rahm    |

|-------------------------------------|---|-----------------------------------|

| Vorsitzender der Prüfungskommission | : | Prof. DiplIng. Dr. Gerhard Fohler |

| Gutachter                           | : | Prof. DrIng. Wolfgang Kunz        |

|                                     |   | Prof. DrIng. Görschwin Fey        |

Tag der Einreichung

:

20.03.2023

Tag der Verteidigung

:

06.07.2023

*Application-Dependent Hardware/Software Cross-Layer Fault Analysis,* © 04.09.2023 by Christian Bartsch

## DANKSAGUNG

Diese Arbeit ist der "finale Schnitt" meiner mehrjährigen Forschung. In dieser Zeit gab es zwar auch Tiefen, zum Glück aber deutlich mehr Höhen. Vor allem dank der Kollegen, die für eine herausragend schöne Atmosphäre am EIS-Lehrstuhl sorgen, und den freundlichen Nachbarn vom Echtzeit-Lehrstuhl werde ich diese schöne Zeit in guter Erinnerung behalten.

Besonderen Dank gebühren Professor Wolfgang Kunz und Professor Dominik Stoffel, die mich jederzeit unterstützt und mir bei Herausforderungen zur Seite gestanden haben.

Vielen Dank auch an den Vorsitzenden der Prüfungskommission, Professor Gerhard Fohler, sowie an den Zweitgutachter, Professor Görschwin Fey, ohne deren Zeit und Mühen die Verteidigung nicht hätte stattfinden können.

Ursprünglich sollte der "Final Cut" bereits im Jahr 2001 mit dem Realschulabschluss stattfinden. Die Reise von diesem Punkt bis hier hin konnte ich nur deswegen schaffen, weil ich währenddessen eine Reihe von lieben Menschen in meinem Leben hatte. Diese möchte ich, wie es sich für einen finalen Schnitt gehört, in einem Abspann ehren; und damit diese Personen die gebührende Beachtung erhalten, kommt dieser Abspann hier an den Anfang.

Sophie und Wilhelm Altes

Birgit und Hans-Jürgen Bartsch

Peter Altes

Sebastian und Alexander Bartsch

Kristin Krüger

Die ganze Familie Altes

Marcel Tegtmeier, Michael Schröter und Stefanie

## DANKE

## ABSTRACT

Hardware devices fabricated with recent process technology are intrinsically more susceptible to faults than before. Resilience against hardware faults is, therefore, a major concern for safety-critical embedded systems and has been addressed in several standards. These standards demand a systematic and thorough safety evaluation, especially for the highest safety levels. However, any attempt to cover all faults for all theoretically possible scenarios that a system might be used in can easily lead to excessive costs. Instead, an applicationdependent approach should be taken: strategies for test and fault resilience must target only those faults that can actually have an effect in the situations in which the hardware is being used.

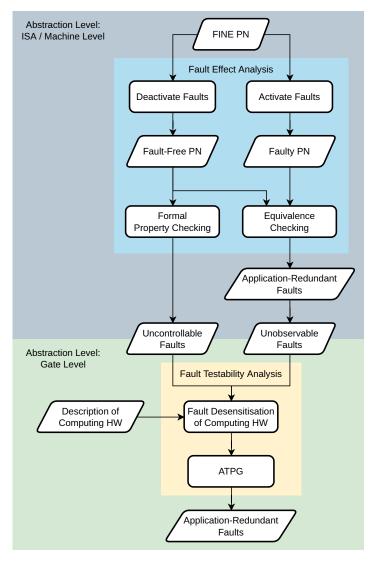

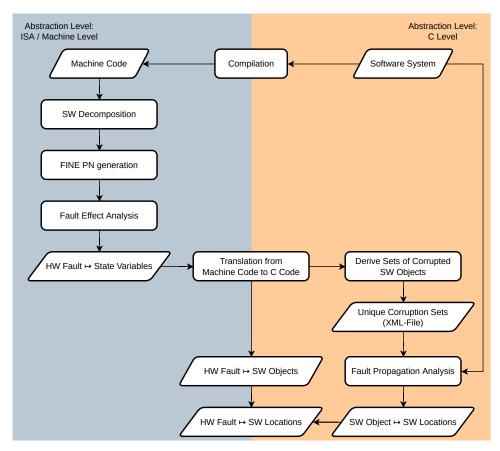

In order to provide the data for such safety evaluations, we propose *scalable* and *formal* methods to analyse the effects of hardware faults on hardware/software systems across three abstraction levels where we:

- perform a fault effect analysis at instruction set architecture level by employing fault injection into a hardware-dependent software model called *program netlist*,

- use the results from the program netlist analysis to perform a deductive analysis to determine "application-redundant" faults at the gate level by exploiting standard combinational test pattern generation,

- 3. use the results from the program netlist analysis to perform an inductive analysis to identify all faults of a given fault list that can have an effect on selected objects of the high-level software, such as specified safety functions, by employing Abstract Interpretation.

These methods aid in the certification process for the higher safety levels by (a) providing formal guarantees that certain faults can be ignored and (b) pointing to those faults which need to be detected in order to ensure product safety.

We consider transient and permanent faults corrupting data in programvisible hardware registers and model them using the single-event upset and stuck-at fault models, respectively.

Scalability of our approaches results from combining an analysis at the machine and hardware level with separate analyses on gate level and C level source code, as well as, exploiting certain properties that are characteristic for embedded systems software. We demonstrate the effectiveness and scalability of each method on industry-oriented software, including a software system with about 138 k lines of C code.

# TABLE OF CONTENTS

| 1 | Int                 | RODUCTION                                 | 1  |  |  |  |

|---|---------------------|-------------------------------------------|----|--|--|--|

|   | 1.1 Embedded System |                                           |    |  |  |  |

|   | 1.2                 | .2 SAFETY IN EMBEDDED SYSTEMS             |    |  |  |  |

|   | 1.3                 | 1.3 Motivation                            |    |  |  |  |

|   | 1.4                 | Overview and Scientific Contributions     | 5  |  |  |  |

| Р | UBLI                | CATIONS                                   | 9  |  |  |  |

| 2 | Вас                 | CKGROUND                                  | 11 |  |  |  |

|   | 2.1                 | Abstraction Levels                        | 11 |  |  |  |

|   | 2.2                 | Abstraction Levels for Software           | 11 |  |  |  |

|   |                     | 2.2.1 MACHINE LEVEL                       | 11 |  |  |  |

|   |                     | 2.2.2 Assembly Level                      | 13 |  |  |  |

|   |                     | 2.2.3 C LEVEL                             | 14 |  |  |  |

|   | 2.3                 | Abstraction Levels for Hardware           | 15 |  |  |  |

|   |                     | 2.3.1 GATE LEVEL                          | 15 |  |  |  |

|   |                     | 2.3.2 Register Transfer Level             | 16 |  |  |  |

|   |                     | 2.3.3 ISA Level                           | 17 |  |  |  |

|   | 2.4                 | Verification of Hardware & Software       | 18 |  |  |  |

|   |                     | 2.4.1 Simulation and Emulation            | 19 |  |  |  |

|   |                     | 2.4.2 Symbolic Techniques                 | 20 |  |  |  |

|   |                     | 2.4.3 Formal Verification                 | 20 |  |  |  |

|   | 2.5                 | Verification of Hardware/Software Systems | 23 |  |  |  |

|   | 2.6                 | Faults                                    | 23 |  |  |  |

|   |                     | 2.6.1 Terminology                         | 23 |  |  |  |

|   |                     | 2.6.2 FAULT MODELS                        | 26 |  |  |  |

|   |                     | 2.6.3 FAULT INJECTION                     | 28 |  |  |  |

|   |                     | 2.6.4 SAFETY STANDARDS                    | 29 |  |  |  |

|   | 2.7                 | Control Flow Graph                        | 31 |  |  |  |

|   |                     | 2.7.1 CFG GENERATION                      | 32 |  |  |  |

|   | 2.8                 | Automated Test Pattern Generation         | 33 |  |  |  |

|   |                     | 2.8.1 ATPG-based Testing in Practice      | 35 |  |  |  |

| 3 | Rei                 | LATED WORK                                | 37 |  |  |  |

| 4 | Pro                 | OGRAM NETLIST                             | 39 |  |  |  |

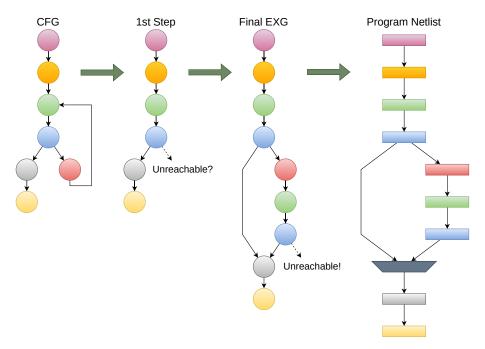

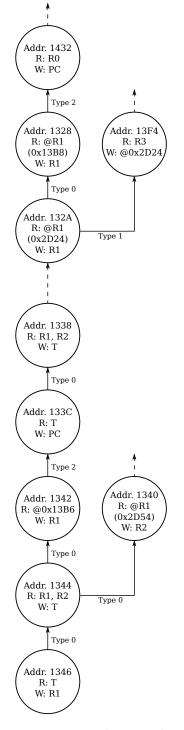

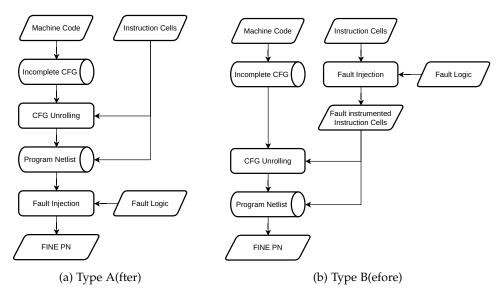

|   | 4.1                 | Program Netlist Generation                | 41 |  |  |  |

|   |                     |                                           |    |  |  |  |

\_\_\_\_\_

|   | •   | Instruction Cells                                   | 42   |

|---|-----|-----------------------------------------------------|------|

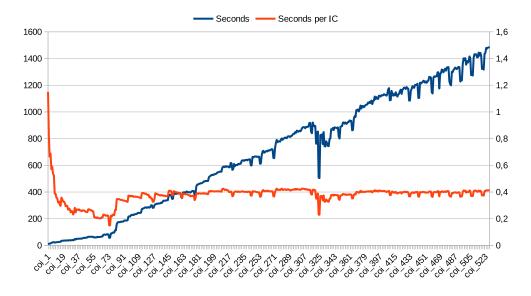

|   | 4.3 | Scalable PN Generation                              | 43   |

|   |     | 4.3.1 Compositional PN Generation                   | 43   |

|   |     | 4.3.2 Instruction Abstraction                       | 45   |

|   |     | 4.3.3 Program Path Priorities                       | 45   |

|   |     | 4.3.4 Address Caching                               | 46   |

|   |     | 4.3.5 Experiments                                   | 46   |

|   | 4.4 | Cone of Influence Computation                       | 49   |

| 5 | Fau | ult Injection in Program Netlists                   | 53   |

|   | 5.1 | Stuck-At Faults                                     | 54   |

|   |     | 5.1.1 Insertion of Fault Injection Logic            | 56   |

|   | 5.2 | SEU FAULTS                                          | 57   |

| 6 | ISA | A-LEVEL FAULT EFFECT ANALYSIS                       | 61   |

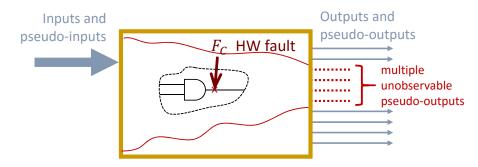

|   | 6.1 | Uncontrollability & Unobservability in PNs          | 63   |

|   | 6.2 | Experiments                                         | 63   |

|   |     | 6.2.1 FAULT EFFECT ANALYSIS - RISC-V RESULTS        | 66   |

|   |     | 6.2.2 Dependency Analysis                           | 67   |

| 7 | ISA | A/GATE CROSS-LEVEL FAULT ANALYSIS                   | 69   |

|   | 7.1 | Experiments                                         | 76   |

|   |     | 7.1.1 FAULT TESTABILITY ANALYSIS - RISC-V RESULTS . | 77   |

| 8 | ISA | A/C CROSS-LEVEL FAULT ANALYSIS                      | 79   |

|   | 8.1 | Software Decomposition                              | 80   |

|   | 8.2 | FAULT EFFECT ANALYSIS FOR SOFTWARE COMPONENTS       | 82   |

|   |     | 8.2.1 FAULT INJECTION                               | 82   |

|   |     | 8.2.2 Modelling Severe Control Flow Errors          | 84   |

|   |     | 8.2.3 Composing the Fault Dictionary                | 85   |

|   | 8.3 | FAULT PROPAGATION ANALYSIS                          | 86   |

|   |     | 8.3.1 Astrée                                        | 86   |

|   |     | 8.3.2 TAINT ANALYSIS                                | 87   |

|   |     | 8.3.3 TAINT-BASED FAULT PROPAGATION ANALYSIS        | 88   |

|   | 8.4 | Experimental results                                | 89   |

|   |     | 8.4.1 FAULT EFFECT ANALYSIS (FEA)                   | 90   |

|   |     | 8.4.2 FAULT PROPAGATION ANALYSIS (FPA)              | 93   |

| 9 | Co  | NCLUSION & OUTLOOK                                  | 97   |

|   | 9.1 | Outlook                                             | 99   |

|   |     | 9.1.1 Bespoke Processor Design                      | 99   |

|   |     | 9.1.2 Online Error Detection                        | 99   |

|   |     | 9.1.3 Abstract Interpretation for Program Netlist   | 5100 |

|   |     |                                                     |      |

| 10 Kurzfassung                               | 101 |

|----------------------------------------------|-----|

| 10.1 Programmnetzlisten                      | 102 |

| 10.1.1 Skalierbarkeit von Programmnetzlisten | 102 |

| 10.2 Fehlerinjektion                         | 104 |

| 10.3 Fehlereffektanalyse                     | 104 |

| 10.4 Fehlertestbarkeitsanalyse               | 105 |

| 10.5 Fehlerpropagationsanalyse               | 105 |

| 10.6 Fazit                                   | 106 |

| Bibliography                                 | 107 |

| ACRONYMS                                     | 117 |

| List of Figures                              | 119 |

| List of Tables                               | 121 |

## INTRODUCTION

Over the past decades information technology has advanced at a breathtaking pace. It has experienced significant improvements in every aspect, be it performance, size or power consumption. Digital systems that, just a few decades ago, used to be as large as a side table are nowadays as small as a credit card. Size has always been a limiting factor for the design of commercial products. However, the small size of modern digital systems allows them to be integrated almost everywhere. This enables new and diverse applications for digital systems and has sparked a gradual process where they perform more and more tasks in commercial products.

The task of most digital systems is to provide certain features for the product in which they are integrated in. For some features digital systems replace larger analog systems, like drive-by-wire in cars or fly-by-wire in avionics. For the majority of applications, digital systems are used to add new functionality to a product, for which smartwatches and smart home products are examples. This development has already changed the consumer market as is publicly observable. However, also industry is influenced by this transformation in many ways, affecting product design, manufacturing and the workplace.

This successive digitalisation has a large impact on our daily life and on how our society works. It creates an abundance of opportunities like featurerich products and new types of jobs. However, it also brings challenges like new malicious attacks, cyber-crime and misbehaving products. These threats need to be addressed not just by society but also by engineers who design current and future generations of digital systems and products.

For example, a malfunctioning or failing digital system controlling the movements of a machinery or vehicle could harm persons close by. Imagine a metal press that does not recognise a hand or limb between ram and bolster or an aeroplane which incorrectly 'thinks' that it is flying too high.

Frequently, digital systems, like anti-lock braking system (ABS) and electronic stability program (ESP) in cars, are successfully used to increase the safety of products for humans. Yet, a failing safety function can make a product less safe than a product lacking such a safety function. This situation can occur when, for example, a failing safety function takes control of the product or when humans have forgotten how to operate the particular product without the failing safety function. Unfortunately, the miniaturisation successes in information technology make digital circuits more susceptible to faults, increasing their likelihood of failure. These safety-critical aspects of digital systems are the focus of this thesis.

#### 2 INTRODUCTION

Besides safety, another important aspect of digital systems is their security, in particular, their resistance against malicious attacks. Since the publication of attacks like Meltdown [70] and Spectre [63] the, once sidelined, security aspect as a potential cause for malfunctioning digital systems received a lot of attention in recent years. Such attacks can also threaten the product's safety. However, issues related to security are not in the scope of this thesis because their nature is typically quite different to those related to safety and, therefore, require a different set of methods and analyses than those presented in this thesis.

#### 1.1 Embedded System

The *processor* is a commonly known example of a digital system. The task of a processor is to execute a software program and to provide interfaces for the software through which it can communicate with components located outside of the processor. The software execution is performed by *cores*, of which a processor can have one or more.

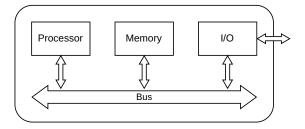

Processors are integrated in *computing platforms*. Figure 1.1 depicts a typical composition of a computing platform on an abstract level. The processor executes the software program that is located in the memory and uses an input/output-interface (I/O) to interact with the environment. The components of a computing platform are typically connected to a shared communication network, for example a bus, through which they communicate with each other. The combination of a hardware, like a computing platform, and a software program is denoted as *hardware/software system* (HW/SW system).

Figure 1.1: Computing Platform

The software that is executed on the computing platform stores intermediate values either in specific memory areas like *stack* or *heap* or in a component called *register file* that is located inside a processor core and has a very limited storage capacity. In contrast to other registers in the processor core, the registers in the register file are accessible by the software program for which they are denoted as *program-visible registers*.

A computing platform, together with connected peripheral devices like sensors or data storages, forms a computer system. Number and types of the peripheral devices depend on the use case of the particular system. The software that is executed by the processor, i.e., the *central processing unit* (CPU), instruments the system's hardware to provide the desired functionalities. The part of a software program that directly interacts with the system's other components is denoted as *low-level software, hardware-dependent software* or *firmware*.

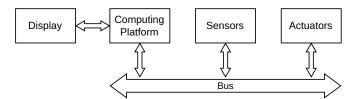

Figure 1.2: Embedded System

A computer system that provides a dedicated functionality to a larger system or product in which it is integrated is denoted as *embedded system*. The computing platform of the exemplary embedded system in Figure 1.2 uses a direct connection to communicate with a display and communicates with sensors and actuators via a bus. Today, with several billion units sold each year the vast majority of processors are used in embedded systems [104].

Some processors are designed for specific tasks. For example, the instruction types and internal structure of *digital signal processors* (DSPs) make them particularly performant in audio or image processing. Processors that do not have a specialised design are denoted as *general-purpose processors*.

The combination of a general-purpose processor with other digital components provides a large degree of flexibility w.r.t. the implementation of functionalities. This design freedom is a major advantage of embedded systems.

#### 1.2 SAFETY IN EMBEDDED SYSTEMS

New manufacturing technologies for digital circuits are constantly being developed to satisfy an ever increasing demand for improvements in performance, area and power consumption. A result of this research effort are ever more complex transistor structures and manufacturing processes. Modern integrated transistors, for example, now have a complex three-dimensional structure that cannot be simplified to the planar model that was used some decades ago. Some steps in the evolution of field effect transistors (FET), a widely used transistor for digital circuits, are depicted in Figure 1.3, with increasing complexity from left to right.

Figure 1.3: Transistor Designs [30]

The larger complexity and smaller distance between their structural elements have made transistors and their interconnections more susceptible to faults and lead to an increased probability of errors, malfunctions and failures.

The consequences of a malfunctioning embedded system depend mostly on its application. For example, a malfunctioning embedded system which provides infotainment in a car may be annoying but it would not directly affect the safety of the passengers. However, embedded systems are frequently employed in safety-critical tasks. For example, in application domains like avionics or autonomous driving they control the speed and direction of travel and identify obstacles to prevent collisions. In other application domains like production automation they verify that nothing, especially no body part, is close or between a moving mechanical system.

For such safety-critical tasks the requirement of *functional safety* has become a key concern in industry and, not rarely, defines the "economic operating point" of new products. This stimulated the development of several international standards like IEC 61508 to define strict measures and requirements for every phase of the development cycle to ensure functional safety in products.

Examples of industry specific safety standards are:

- ISO 26262 for automotive

- IEC 61511 for industrial processes

- IEC 61513 for nuclear power plants

- IEC 62061 & ISO 13849 for machinery

- EN 5012x for railways

- DO-178 & DO-254 for aviation

- IEC 62304 for medical devices

Yet, it is often not clear how the objectives formulated in these standards can actually be achieved in practice by the chosen architectures and design methods, and how this can be documented. For instance, to increase the safety of an embedded system, a large spectrum of design measures with varying costs is available both at the hardware and at the software level.

#### 1.3 MOTIVATION

Size and complexity of modern digital systems allow faults to manifest themselves in numerous ways at various locations. Implementing protection against all possible types of faults is costly and sometimes infeasible. We need to focus on those faults which can actually violate the functional safety of the system.

Safety standards demand the provision of guarantees that faults that are ignored can never compromise the functional safety of a system. In order to provide such guarantees the complete behaviour of the fault affected digital system has to be considered. The most prominent approaches for such safety analyses are exhaustive simulation and formal verification. Of those, the former tends to require an infeasible amount of time to analyse the effects for every possible input sequence, while for the latter the computational complexity of the analysis quickly becomes impractical.

The need for a formal method that can provide the aforementioned guarantees and that is still scalable motivates this thesis. We achieve this goal by exploiting the following characteristics of embedded systems.

Embedded systems typically provide clearly defined, limited tasks which implies that, for the most part, the software does not undergo major changes during a system's lifetime. This is true especially for low-level software that constitutes an important component of a chip's general infrastructure, for example, by controlling the communication between application software and hardware, by implementing important functions for chip management and, more and more often, by replacing traditionally hardware-implemented control functions of the system. Such software components are usually part of the system's firmware. They are tightly coupled with the hardware and, in many cases, play a particularly important role for the overall system safety. This application-specific nature of embedded systems, typically, leads to software which utilizes only a fraction of the processors capabilities.

The small changes to embedded systems software allows the implementation of cost-efficient safety measures tailored to a concrete software program. The limitation to a particular system software restricts the hardware utilization and, as shown in our experiments, limits the number of locations from where errors can propagate through the system to make it malfunction.

In this thesis we focus on faults that manifest themselves in processor cores and do not explicitly consider faults originating from other components of the embedded system. The main objective of this thesis is to show how formal methods can be used to identify all faults that can never affect the safety of a HW/SW system of realistic size. This thesis contributes a method to generate a computational model on which the effects, and the absence of any effect, of hardware faults on the software behaviour can be formally proven. Further, it shows how fault effects can be analysed across multiple abstraction layers in a formally sound way. Note that by showing that only certain faults can have a specific effect, e.g., affecting a safety function, formal methods also prove that every other fault can never cause the considered effect and can, therefore, be ignored in the corresponding safety evaluation.

#### 1.4 Overview and Scientific Contributions

As motivated in the previous section, the main objective of this thesis is the development of methods to formally analyse the effects of hardware faults on the behaviour of a HW/SW system. In order to obtain realistic results, we employed fault models that are commonly used in the field of testing and analysed the fault effects on industry-oriented software programs. This research effort yields a toolbox of methods to formally analyse the propagation of fault effects across multiple abstraction levels, namely the gate level, the instruction

#### 6 INTRODUCTION

set architecture (ISA) level and the higher software level (C level). We achieved a degree of automation where almost all steps of the methods presented in this thesis are fully automated. We point out the few steps where manual effort is required in the corresponding sections.

As the main scientific result of this thesis we present a cross-layer technique providing formal guarantees on fault effects propagating from the gate level to the C level. We demonstrate the new approach for systems of realistic size that were so far deemed intractable for any formal analysis of this kind. The main elements of this contribution are the following:

- 1. We develop a set of methods which allow us to improve the scalability of generating our basic computational model, called *program netlist* (*PN*). This contribution makes it possible to use PNs in our fault effect analyses even for large firmware and driver systems. We discuss these methods in Section 4.3.

- 2. In order to increase the scalability of the fault analysis methods, we develop the dependency analysis presented in Section 4.4. This method allows a cone-of-influence reduction on a PN and decreases the complexity of any PN-based formal analysis.

- 3. The ISA-level fault models used in this thesis are designed in such a way that they have a sound representation on the gate level. We achieve this by formulating stuck-at and single-event upset (SEU) fault models for program-visible registers. We provide a detailed discussion on this, together with several fault description styles, in Section 5.

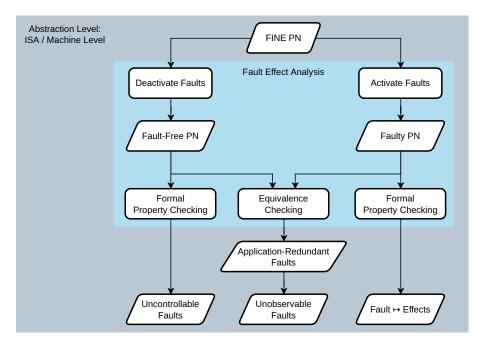

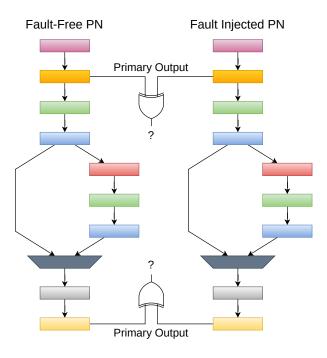

- 4. The formal method presented in Chapter 6 (*FEA*), can analyse the effects of hardware faults on the program behaviour at the ISA level by injecting faults in program netlists. The result of FEA are two sets of faults. In the first set are faults which, for certain input sequences, have an effect on the considered program behaviour. The faults in the second set never have an effect on the considered program behaviour.

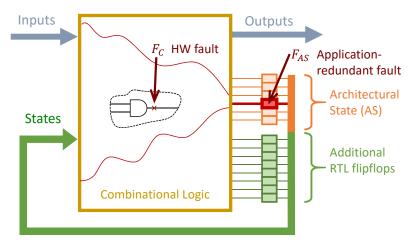

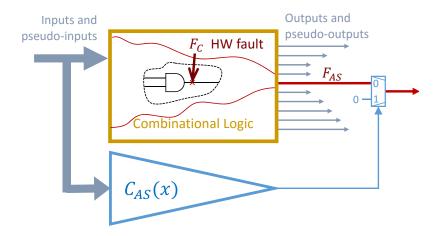

- 5. In Chapter 7 we show how the knowledge about the absence of fault effects obtained from FEA can be used to deductively identify faults on the gate level which, due to the constraints applied by the executed software program, also never have any effect on the behaviour of the HW/SW system. We denote these faults as *application redundant faults*. This method (*FTEA*) employs automated test pattern generation for this purpose and identifies gate-level faults that can never have an effect on the considered program behaviour.

- 6. In order to analyse fault effects also on higher software abstraction levels, we developed the formal method *FPA*. FPA takes the ISA-level fault effects found by FEA, inductively transfers them to faults at the higher software level (C level) and applies Abstract Interpretation to identify all other software objects, like safety critical functions, that can be affected

by a particular fault. The result of FPA is a 1-to-n relation between hardware faults on the ISA level and their effects on the C level. We present this method in Chapter 8.

## PUBLICATIONS

We already published several aspects of this thesis as shown by the following bibliography. Key elements of this thesis are presented in [14, 17, 18].

- [12] C. Bartsch, N. Rödel, et al. "A HW-dependent Software Model for Cross-Layer Fault Analysis in Embedded Systems". In: International Workshop on Resiliency in Embedded Electronic Systems. 2015.

- [13] C. Bartsch, N. Rödel, et al. "A HW-dependent Software Model for Cross-Layer Fault Analysis in Embedded Systems". In: 19th GI/ITG/GMM Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, MBMV 2016, Freiburg im Breisgau, Germany, March 1-2, 2016. Ed. by R. Wimmer. Albert-Ludwigs-Universität Freiburg, 2016, pp. 10–21. DOI: 10.6094/UNIFR/10634.

- [14] C. Bartsch, N. Rödel, et al. "A HW-dependent Software Model for Cross-Layer Fault Analysis in Embedded Systems". In: 2016 17th Latin-American Test Symposium (LATS). 2016, pp. 153–158. DOI: 10.1109/LATW. 2016.7483356.

- [15] C. Bartsch, C. Villarraga, et al. "Efficient SAT/Simulation-based model generation for low-level embedded software". In: 17th GI/ITG/GMM Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, MBMV 2014, Böblingen, Germany. Ed. by J. Ruf, D. Allmendinger, et al. Cuvillier, 2014, pp. 147–157.

- [16] C. Bartsch, C. Villarraga, et al. "Safety across the HW/SW interface -Can formal methods meet the challenge?" In: *International Symposium on Integrated Circuits, ISIC 2016, Singapore, December 12-14, 2016.* IEEE, 2016, pp. 1–3. DOI: 10.1109/ISICIR.2016.7829707.

- [17] C. Bartsch, C. Villarraga, et al. "A HW/SW Cross-Layer Approach for Determining Application-Redundant Hardware Faults in Embedded Systems". In: *Journal of Electronic Testing* 33.1 (2017), pp. 77–92. DOI: 10.1007/s10836-017-5643-3.

- [18] C. Bartsch, S. Wilhelm, et al. "Compositional Fault Propagation Analysis in Embedded Systems using Abstract Interpretation". In: 2021 IEEE International Test Conference (ITC). 2021.

- [19] C. Bartsch, S. Wilhelm, et al. "Combining Fault Effect Analysis and Fault Propagation Analysis to Determine Source Code Level Effects of Hardware Faults". In: *Embedded World*. WEKA FACHMEDIEN GmbH, 2022.

- [95] S. G. Sørensen, C. Bartsch, et al. "Generation of Formal CPU Profiles for Embedded Systems". In: 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration (VLSI-SoC). IEEE, Oct. 2022.

- [107] C. Villarraga, B. Schmidt, et al. "An Equivalence Checker for Hardware-Dependent Software". In: 11. ACM-IEEE International Conference on Formal Methods and Models for Codesign (MEMOCODE). 2013, pp. 119–128.

- [108] C. Villarraga, B. Schmidt, et al. "Software in a Hardware View: New Models for HW-dependent Software in SoC Verification and Test (Invited Paper)". In: *Proc. International Test Conference (ITC'14)*. 2014.

## BACKGROUND

In this chapter we review the various state-of-the-art concepts and methods from different fields which are used in this thesis and which are relevant for a deeper understanding of our contributions.

#### 2.1 Abstraction Levels

Abstraction is a method where specific information details are intentionally left out of consideration. The application of abstraction creates a more general concept, i.e., an abstract model of a concrete object. For example, the abstract term *transistor* is used when the information about the transistor type, e.g., bipolar or field effect transistor, is irrelevant for a particular discussion.

The goal of abstraction is to remove complexity by considering only those aspects which are relevant for a specific purpose. For example, when only the result value of an addition needs to be analysed time or individual steps the processor needs to perform the computation are irrelevant and, therefore, can be ignored.

When an abstract concept is further abstracted every abstraction step creates a new, higher, *abstraction level*. In the following sections we provide a survey on those abstraction levels for hardware and software that are used in this thesis.

#### 2.2 Abstraction Levels for Software

There exist several abstraction levels at which the behaviour of software programs can be described. In this thesis, only the lowest three of the software abstraction levels are of relevance, the *machine level* 2.2.1, the *assembly level* 2.2.2 and the *C level* 2.2.3.

#### 2.2.1 MACHINE LEVEL

Machine language is the actual language read in and executed by the processor. Its alphabet consists of only two letters, the values of a binary digit (*bit*) zero and one. A software program written at machine level, i.e., in machine language, is called *machine code* or *machine program*. The machine level is, therefore, the lowest abstraction level for a software program.

In general, machine code is a sequence of bit values situated in the memory of a computing platform (cf. Figure 1.1). For some processor architectures the machine code is stored together with the data in the same memory while for others the machine code is stored separate from the software-accessible data. In such architectures, the memory with the machine code, typically, cannot be written by the software and is, therefore, denoted as *read-only memory* (ROM). Memory whose contents can be read and modified by a software program in any order is denoted as *random access memory* (RAM). In most systems writing and overwriting machine code is strictly forbidden during runtime, because it is extremely error-prone. The smallest addressable unit of a memory is typically a *byte* which is a group of 8 adjacent bits. The locations of individual bytes are identified by their respective memory addresses.

When a processor executes a software program it reads an instruction, i.e., a group of consecutive bytes denoted as *instruction word*, from memory, decodes it and executes the instruction as specified by the architecture the processor implements. This specification is part of the instruction set architecture discussed in Section 2.3.3.

A segment of the instruction word, denoted as *opcode*, specifies the operation the processor is to perform. Other bits define the operands to be used by the operation. Possible operand types of an instruction are numbers, memory addresses or registers in the register file. Opcode and operands are written in binary format and may even be distributed over the instruction word. For example the bits for operand "imm" in Figure 2.1 are split into two blocks of adjacent bits located at two different positions in the instruction word.

| 31        |       |       |       |          | 0       |

|-----------|-------|-------|-------|----------|---------|

| imm[11:5] | rs2   | rs1   | func3 | imm[4:0] | opcode  |

| 00000000  | 01110 | 00010 | 010   | 01000    | 0100011 |

Figure 2.1: Example machine code instruction

Consider the example instruction for a RISC-V processor in Figure 2.1. The numbers at the top of the table are indices for the left-most and the right-most bit, providing the necessary information how the bits of the instruction word have to be interpreted. The highest index is used for the *most significant bit* (MSB) and the lowest index for the *least significant bit* (LSB). The first row shows the fields of a RISC-V instruction format that is used to specify different variants of store instructions, according to the RISC-V instruction set manual [109]. The instruction consists of the following instruction fields:

- An opcode field to identify the instruction as store instruction.

- A func3 field telling the processor how many bytes have to be written to memory.

- The fields rs1 and rs2, of which each contains a number addressing a program-visible register used in the store operation.

- Two fields for the imm operand used to compute the memory location where the values have to be stored.

The last row of Figure 2.1 shows an example instruction word split into the corresponding instruction fields. This particular instruction performs a store

operation (opcode) and stores 4 bytes (func3) of register number 14 (rs2) to the memory starting with the address that is computed by adding a constant value (imm) to the value in register 2 (rs1).

#### 2.2.2 Assembly Level

The machine code is what is actually executed by the processor, but its bits and bytes are very difficult for humans to read and understand. Machine programs are, therefore, expressed in an abstract representation called *assembly language*. Programs in such a language can be translated to machine code using an *assembler*. In assembly language, instructions are represented by a textual description that hides the details of bit values for the individual fields in the instruction word.

Typically, an instruction specified at assembly level starts with a *mnemonic* describing the operation to be performed followed by a comma-separated list of operands.

At assembly level, numbers are usually written in decimal or hexadecimal format, and rarely in binary format. Program-visible registers are addressable via aliases and not just by their number. In some processors the alias provides information about the register's intended usage, e.g., for RISC-V processors t0 refers to a register for temporary values and intermediate results.

| 1 target:  |                         |

|------------|-------------------------|

| 2 li t0, 0 |                         |

| 3          | 1 mv t0, t1             |

| 4 j target | 2 addi t0, t1, 0        |

| (a) Symbol | (b) Pseudo-Instructions |

| Figure 2.2: | Example | features | of the | assemb | oly i | level |

|-------------|---------|----------|--------|--------|-------|-------|

|             |         |          |        |        |       |       |

Memory addresses can also be written in hexadecimal format, however, such explicit use of memory addresses is rare. Instead, a descriptive symbol denoted as *label* is used that implicitly points to a specific memory address. The RISC-V assembly code in Figure 2.2a shows in line 4 a jump instruction with the label "target" as operand. This label is defined in line 1 and will be translated to the memory address of the load immediate instruction in line 2 during the translation from assembly code to machine code.

Another assembly-level feature that is not supported at the machine level are pseudo-instructions. Their purpose is to improve development and readability of assembly code by providing a simplified version of (a set of) semantically equivalent assembly instructions. For example, both RISC-V assembly instructions in Figure 2.2b copy the contents of register t1 to register t0 and both are translated to the same machine instruction. However, the first instruction, move, requires less assembly level operands and is more expressive.

Except for some special cases, an assembly instruction can be directly translated to a machine instruction. A translation in the other direction, i.e., from machine instruction to assembly instruction, is also possible. In theory, this task can be difficult to accomplish as shown by [20]. In practice, however, and in particular for the software considered in this thesis, disassembly is usually possible using standard techniques and tools.

For low-level programs used in embedded systems the translation from assembly level to machine level is straightforward, so that analysis results obtained at assembly level can be mapped to the machine level in a sound way.

1 is\_even\_number: xori a0, a0, -1 2 lui t0, 1 3 and a0, a0, t0 4 ret

Figure 2.3: Example assembly code

The RISC-V assembly code function in Figure 2.3 checks whether the provided value in register a0 is an even or odd number and returns the answer to the calling function by writing the corresponding binary value of *true* or *false* to register a0. For the computation the number's bit values are inverted by using the xor-operation in line 1 and, then, all bits, except the LSB, are set to zero in line 2. The value of the LSB in a0 tells whether the given number was even or not.

Even without an explicit comparison it should be clear that the assembly code in Figure 2.3 is easier to understand than its equivalent machine code. However, as we will point out in the following section, the next higher abstraction level allows to write the same function in a much conciser way.

#### 2.2.3 C LEVEL

As program complexity increased, the need for higher abstraction levels grew, resulting in the development of new programming languages. Nowadays, there exist many programming languages which support various styles of programming allowing to freely choose the degree of abstraction. Characteristic for these programming languages is their use of abstracter concepts. For example, they utilize statements and variables instead of instructions and memory locations, respectively. The two major advantages are the use of statements and variables being more intuitive for humans and the size of programs written at higher abstraction levels being an order of magnitude smaller because a single statement can represent multiple machine instructions.

A popular example is the C programming language, which is still frequently used for programming embedded systems, especially for device drivers. These low-level programs provide an abstract interface to peripheral devices for application software written on a higher abstraction level. In the rest of this thesis we will use the term *C level* to refer to software abstraction levels above assembly.

The translation process from C level to assembly level is denoted as *compilation* and is performed by a software program called *compiler*. A major disadvantage of this abstraction level is that knowledge obtained from C level cannot be transferred to lower abstraction levels in a sound way. The reason for this is the large degree of freedom in the ways C statements can be translated to assembly instructions. The assembly code produced by one compiler can be completely different to the assembly code of another compiler although they have translated the same C-code. This aspect becomes worse in the presence of optimisations, as they are regularly performed by compilers. For example, the value of a variable can be placed in memory, in the register file or can be optimised away.

```

1 bool is_even_number(int number)

2 {

3 return (number % 2) == 0;

4 }

```

Figure 2.4: Example C code

The code in Figure 2.4 is functionally equivalent to the assembly code in Figure 2.3. It is shorter and uses the modulo operation which may involve the more complex integer division in the compiled program, whereas the optimised assembly code employs simple logic operations.

#### 2.3 Abstraction Levels for Hardware

Similar to the software domain, the behaviour of hardware can be described at several abstraction levels, of which the *gate level* 2.3.1, the *register transfer level* 2.3.2 and the *instruction set architecture level* 2.3.3 are of relevance in this thesis. In this context, we focus on hardware located inside a processor, particularly the processor core. Digital circuits can be classified as combinational or sequential. A digital circuit that only uses its current input values to compute output values is called *combinational circuit*, while a circuit that uses previously computed values, alone or in combination with the current input values, to compute output values is called *sequential circuit*. The previously computed values constitute the *state* of a sequential circuit. A sequential circuit implements a *transition function* that defines how the next values, i.e., the next state, is computed depending on the previous state and the current input. The state of a sequential circuit is usually stored in memory elements like flipflops and registers. A combinational circuit does not have such storage elements.

#### 2.3.1 GATE LEVEL

The gate level is the first abstraction level above the transistor level. At the gate level transistors and electrical information such as voltage, resistance and capacitance, of a digital circuit are hidden. Only the logic functions implemented by the transistor circuitry are represented. Every gate models a Boolean function abstracting the corresponding transistor circuit. Instead of two discrete

voltage levels used at the transistor level, the inputs and outputs of gates use Boolean values which can also be interpreted as bit values.

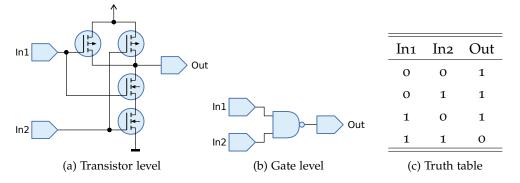

Figure 2.5: Gate level abstraction for NAND

Figure 2.5 illustrates the abstraction from transistor level (Figure 2.5a) to gate level (Figure 2.5b) at the example of the negated AND-operation. Both circuits implement the same logic function, i.e., for all input scenarios they produce the same output behaviour, as depicted in Table 2.5c.

The transistor circuit in Figure 2.5a uses the complementary metal-oxidesemiconductor (CMOS) technology commonly used to manufacture digital circuits by using two types of metal-oxide-semiconductor field-effect transistors (MOSFET). One MOSFET type the PMOS transistor, sets the output voltage to *high*, i.e., a logical one, and the other transistor type, the NMOS transistor, sets it to *low*, i.e., a logical zero.

When compared with the abstraction level of assembly from the software domain, the gate level provides similar advantages and disadvantages. It reduces the overall complexity of a digital circuit and is easier to understand for humans while allowing the knowledge transfer of analyses to and from the transistor level in a sound way. However, performing a comprehensive analysis for circuits of realistic size on gate level can be too complex to pursue. This is particularly true when the full behaviour, i.e., the complete semantics, of the circuit has to be considered, as is required for fault effect analyses.

#### 2.3.2 Register Transfer Level

The next higher abstraction level is the *register transfer level* (RT level or RTL). Abstraction from gate level to RTL is achieved by hiding the computation of individual Boolean values of the gate level behind modules and statements.

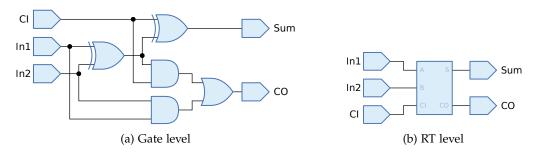

This abstraction is illustrated in Figure 2.6, where the gate-level full adder in Figure 2.6a and its RT level representation in Figure 2.6b are functionally equivalent. Both circuits take three Boolean values, In1, In2 and carry-in (CI), as inputs and compute sum and carry-out (CO).

An advantage of the RT level is that it supports the aggregation of multiple Boolean/bit values into bitvectors. Figure 2.7 shows a textual description of a similar circuit by using the hardware description language (HDL) Verilog. It defines an addition module that takes two 32bit signals interprets them as signed numbers and assigns the results of the addition to the output signal.

Figure 2.6: RT level abstraction of addition

Popular HDLs for the design of digital circuits at RT level are Verilog and VHDL<sup>1</sup>.

```

1

module signed_addition(

2

input logic [31:0] in1,

3

input logic [31:0] in2,

4

output logic [31:0] sum);

5

6

always_comb

7

begin

8

sum = signed(in1) + signed(in2);

9

end

10 endmodule

```

Figure 2.7: 32-bit signed addition at RT level

As can be seen in Figure 2.7, the concepts used for designing hardware at RT level are similar to those used for writing software at C level. Likewise, a disadvantage of this abstraction level is that most knowledge obtained from analyses at RT level cannot be soundly mapped to lower abstraction levels, because statements at RT level can be implemented in many ways at the gate level.

#### 2.3.3 ISA LEVEL

The *instruction set architecture* (ISA) specifies the behaviour of a processor during software execution and defines what machine code a processor supports including the instruction types and their formats. The ISA provides, therefore, the interface between hardware and software. By using the analogy from Section 2.2.1: the machine language provides the letters and the ISA defines words and grammar of the machine language that a processor understands.

ISA specifications are abstract and do not contain implementation details like exact instruction timing in processor clock cycles. They ensure that software written for a specific ISA can be executed on every processor that implements this ISA.

<sup>1</sup> Very High-Speed Integrated Circuit Hardware Description Language

A processor description on ISA level contains mainly a component to decode instructions, a file of program-visible registers and an implementationindependent description of the processor's behaviour for each instruction. The state of a processor core at the ISA level is denoted as *architectural state* (AS) and includes the state of the program-visible registers, the program counter and any program-visible status information.

The advantage of the ISA level is its high degree of hardware abstraction while retaining the ability to be combined with software on machine level. *Instruction set simulators* use this to provide high-performance execution of software programs compiled for an ISA that may be different from the ISA of the processor on which the simulator runs.

Since the ISA level is implementation-independent, knowledge obtained from analyses at ISA level cannot be translated to the gate level in a sound way in most cases. An exception is knowledge regarding program-visible registers as they have a representation on the gate level.

The relevant ISAs for this thesis are SuperH2 [86], originally developed by Hitachi, and RISC-V [109] developed by University of California, Berkeley.

In this thesis we exploit that the ISA level provides a direct connection to gate level via the register file and an interface to the machine level.

#### 2.4 Verification of Hardware & Software

An important part during the design process of hardware and software is to ensure that the design meets its specification, e.g., it is free of bugs and resilient against faults. The basic idea is to formalise the design specification by deriving mathematical models, denoted as *properties* or *assertions*. A design, then, complies with its specification only if every property holds for all possible values at the *primary inputs*. When the property set is complete, i.e., it covers every aspect of the specification, then compliance with the specification is also a necessary condition for the properties to hold.

Primary inputs of a design or a design component are those inputs which are not controlled by the design or component itself but by the environment, i.e., by connected external systems or devices which provide values to these inputs. Examples of primary inputs in software are the register *ao* in Figure 2.3 and the variable *number* in Figure 2.4. Examples of primary inputs in hardware are *In1* and *In2* in Figure 2.5 and *CI*, *In1* and *In2* in Figure 2.6. Analogous to primary inputs are the *primary outputs* of a design which are used by the design to send values to its environment.

Verification is a complex and time-intensive task where its procedural details, like the selection of analysis methods and the number and order of the analysis steps, depend entirely on the individual design and its application case. That is why there exists a wide range of methods and tools, developed for different system types and different aspects of hardware and software that have to be verified. These methods employ one or a combination of the following concepts.

#### 2.4.1 Simulation and Emulation

Simulating a hardware or software design means that its behaviour, which it would have in the real world, is imitated by a simulation tool that executes a computational model of the design. The simulation tool executes the computational model, e.g., RT code of hardware or assembly code of software, by interpreting its statements. The basic idea of the interpretation process is to simulate the behaviour of a single statement and then determine the successor statement whose behaviour will be simulated next.

Simulation has the advantages that it is very fast and that it scales linearly with the number of statements, allowing fast simulation runs of large hardware and software designs. A simulation run can start from reset or a user defined start statement in the design and either ends when no successor statement can be found or when a user defined end statement was simulated.

The disadvantage of simulation is that every simulation run requires a concrete value for every primary input of the design. For sequential designs a concrete value must be provided for every primary input and every time point, e.g., a value per clock cycle for hardware or a value per function call for software. This dependency on concrete values causes the simulation runtime to scale exponentially with the number of primary inputs when a simulation run for every combination of input values has to be performed. Such an *exhaustive simulation* is, therefore, rarely feasible for designs of medium and larger size.

Emulation is based on the same principle as simulation. Its major difference is that the imitation process is executed on a separate piece of hardware for which the design and the emulation environment is highly optimised. The runtime per statement during emulation is lower than during simulation providing a significant speed advantage for a complete emulation run over an equivalent simulation run. Nonetheless, emulation shares the problem of exponential scaling w.r.t. the number of primary inputs with simulation. This issue drastically overcompensates the linear speed advantage of emulation such that *exhaustive emulation* does not provide a feasible alternative to an infeasible exhaustive simulation.

Simulation- and emulation-based verification methods check the assertions during each simulation run and notify the verification engineer when an assertion fails. However, analyses based on non-exhaustive simulation can never cover the complete design behaviour and can, therefore, never guarantee the absence of behaviour violating any specification or safety goal. In order to attenuate this disadvantage modern verification methods perform a number of simulation runs until the probability of specification violations is determined to be sufficiently low. For safety-critical applications, like avionics or nuclear power plants, this presents a serious drawback, because the computation of this probability depends on, possibly flawed, assumptions on the real-world. Examples of such assumptions are values deemed to be impossible or less likely for certain primary inputs, or that the rate at which faults appear is below a certain limit.

#### 2.4.2 Symbolic Techniques

Hardware circuits or software programs can also be verified by using symbolic techniques. In the hardware domain the general term for such techniques is *symbolic simulation*, while *symbolic execution* is used in the software domain [27, 28].

Symbolic simulation-based methods and symbolic execution-based methods share a common methodology from which they inherit its advantages and disadvantages. In the following, we discuss these similarities.

Symbolic techniques use symbolic values which mathematically represent *sets* of data values in the design's state variables and at its primary inputs [53, 91]. This solves the limitation of classic simulation and emulation where only single, individual concrete values can be considered in each simulation/execution run. By using symbolic values, at least in principle, the complete design behaviour for all input values can be considered in a single symbolic simulation/execution/execution/execution run. A holding assertion, therefore, is valid for the complete design behaviour.

A disadvantage is that the complexity of the mathematical models increases with every interpreted statement. For data processing designs, which typically have a large portion of non-branching statements, the complexity growth with each statement may be manageable even for designs of medium size.

However, the complexity can increase significantly with each control statement [25] like branches at assembly level or if-statements at C level. The reason is that control statements can have more than one successor which increases the number of execution paths. In the worst case, the number of execution paths grows exponentially with the number of control decisions. This is known as the *path explosion* problem [98]. Applying symbolic simulation or symbolic execution to larger control-centric designs, e.g., designs with a hardware- or software-implemented finite state machine, is, therefore, rarely feasible.

Symbolic techniques employ several optimisation strategies to keep the computational model compact [6, 81]. By example of symbolic execution, one optimisation strategy is to include only reachable program paths in the model. Such paths are identified in an analysis applied on an intermediate mathematical model of the program. Another optimisation strategy is to merge identical program paths [6]. In order to facilitate the execution of both optimisations, symbolic techniques use *control flow graphs* which model the control behaviour of a hardware or software design. We discuss control flow graphs in detail in Section 2.7.

#### 2.4.3 FORMAL VERIFICATION

Formal verification methods translate the full design into a mathematical model and combine this with the mathematical model of a property. By applying mathematical and logical proofs formal methods try to prove the correctness of the combined model. If this succeeds, it formally shows that the design complies with the considered property for its complete behaviour. If this fails, a counterexample can be generated showing a behaviour where the considered property fails, i.e., where the design violates the considered aspect of its specification. The advantage of formal verification is that it considers all possible values at the primary inputs and can analyse data- and control-centric designs. A disadvantage is that it can suffer from an exponential complexity in terms of runtime or memory usage of the formal proof engines, making the analyses of medium to large designs infeasible. In practice, timeouts and limited computing resources cause formal verification methods to eventually terminate inconclusively. A well-known example for the complexity problem is the formal verification of hardware-implemented multiplication by using SAT solvers [111]. A SAT solver is a computer program solving the Boolean satisfiability problem which belongs to the class of NP-hard<sup>2</sup> problems.

The methods presented in this thesis employ only formal techniques and formal verification tools guaranteeing that the complete behaviour of an analysed hardware/software system is considered.

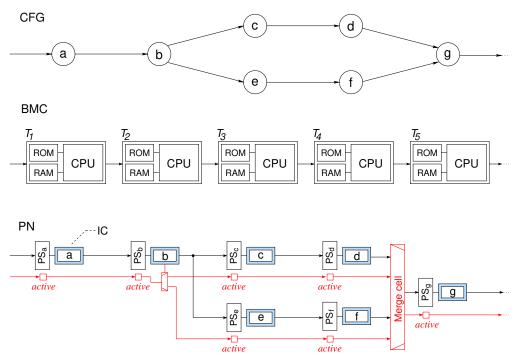

#### Bounded Model Checking

The formal verification of a sequential hardware design requires to analyse the design's behaviour over several time points, i.e., clock cycles, starting from system reset. In *bounded model checking* (BMC) [24] this is done by unrolling the hardware, e.g., duplicating the hardware, and connecting one hardware instance with another in such a way that every instance models the hardware behaviour for a specific clock cycle. The number of hardware instances grows linear with the number of clock cycles to be analysed. Unfortunately, the analysis complexity grows exponentially with the number of hardware instances. In practice this is observed by a sharp increase in the computational resource consumption. This limits the application of BMC in particular and formal verification in general to verification runs that cover only a small number of clock cycles after reset. For example, only a dozen clock cycles of unrolling is feasible for a processor of medium size, like in-order RISC-V processors with 5 pipeline stages.

#### INTERVAL PROPERTY CHECKING

A solution to analyse the hardware behaviour further away from reset than just a few clock cycles is *interval property checking* (IPC) [78]. The fundamental model of IPC, a finite unrolling of the circuit, is the same as in BMC, however IPC does not need to start from reset. In general, IPC starts from *any-state* where registers are not constrained and are allowed to have an arbitrary value. However, starting from any-state can lead to large over-approximations where the analysis includes behaviour that is unreachable in practice. This can easily lead to the situation that an unreachable state causes a property to fail, denoted as *false negative* or *false counterexample*. In practice, false counterexamples are reduced and excluded by adding *invariants* to the properties. Invariants are formulated as logic constraints that are universally valid for the design under

<sup>2</sup> non-deterministic polynomial time hardness

#### 22 BACKGROUND

verification and that restrict the set of starting states by excluding unreachable behaviour.

An application case for IPC is to decompose the specification of a sequential circuit into properties of manageable time length, each representing a specific behaviour. We re-use the basic idea of this concept in Section 8.1 where we analyse the behaviour of a large software system.

#### STATIC SOFTWARE ANALYSIS

In the domain of software verification static and dynamic software analyses are widely used techniques. Static software analysis-based approaches consider the behaviour of single statements or complete software programs without executing them [88]. In contrast, dynamic software analysis-based approaches require the software program under consideration to be executed, e.g., via simulation or emulation, making this approach non-formal. Static software analysis is employed in a variety of verification tasks that includes but is not limited to the following:

- A simple expression checking algorithm verifying that software code complies with a specific set of design rules [10].

- A sophisticated formal analysis that mathematically proves the functional correctness or behavioural properties of a software program [34, 106].

The formal methods in the software domain presented in this thesis belong to the category of static software analysis.

#### Abstract Interpretation

The semantics of a programming language is a formal description of the behaviour of programs. The most precise semantics is the so-called concrete semantics, describing closely the actual execution of the program on all possible inputs. Yet in general, the concrete semantics is not computable. Even under the assumption that the program terminates (cf. halting problem [105]), it is too detailed to allow for efficient computations. A solution is to introduce a formal abstract semantics that approximates the concrete semantics of the program in a well-defined way and still is efficiently computable. This abstract semantics can be chosen as the basis for a static software analysis. Compared to an analysis of the concrete semantics, the analysis result may be less precise but the computation may be significantly faster.

Abstract Interpretation is a formal method for sound semantics-based static software analysis [32]. It supports formal correctness proofs: it can be proved that an analysis will terminate and that it is sound in the sense that it computes an over-approximation of the concrete program semantics. Abstract Interpretation always provides full data and control coverage.

As of today, Abstract Interpretation-based static analysers have evolved to become standard methods for determining non-functional software quality properties [54, 56]. On the one hand, this includes source code properties, such as compliance with coding guidelines, compliance with software architectural requirements, as well as absence of runtime errors and data races [58]. On the other hand, also low-level code properties are covered such as absence of stack overflows and violation of timing constraints [57, 59].

#### 2.5 Verification of Hardware/Software Systems

A HW/SW system is a digital system where one part of the system is implemented in hardware while the other part is implemented in software. Only the combination of both parts can provide the required functionalities. Embedded systems, as defined in Section 1.1, are widely deployed types of HW/SW systems.

The challenge to fully analyse and verify such systems is considerable due to the large complexity emerging from a combination of hardware and software. The traditional approach to analyse such systems is to separate the hardware part from the software part and to analyse each part separately. The advantage of this approach is that the complexity of each analysis is significantly smaller than the analysis of the complete HW/SW system. However, this comes at the cost that the interaction between hardware and software is not considered. This may allow for certain development faults and error propagation paths to remain hidden, endangering the correct operation of the HW/SW system.

The methods proposed in this thesis show how the effects of hardware faults on the behaviour of embedded systems can be formally analysed across HW/SW boundaries.

#### 2.6 FAULTS

In every stage of the design and manufacturing process as well as during its operational lifetime, a fault can lead to an error in a HW/SW system and cause it to malfunction. Be it a flawed specification, bugs introduced in the design phase, manufacturing variations or physical wear-out, faults can originate from several source types and manifest themselves in many ways.

In this section we provide an overview on terminology, categories and standardisation measures to increase the fault resilience of HW/SW systems.

#### 2.6.1 TERMINOLOGY

Table 2.1 presents definitions of terms [8] used in this thesis some of which may be used interchangeably in daily life due to their ambiguous meaning.

Only an *active* fault produces an error. A fault that is present but does not produce an error is *dormant* [8], for example, a fault that sets a value that is already zero to zero. In order to activate a fault an input sequence denoted as *activation pattern* or *activation condition* is required. Some activation conditions are trivial, because they are always fulfilled, while others require very complex combinations of internal state and input sequences.

| Failure     | A failure is a deviation of the output behaviour from the in-<br>tended behaviour of a component or system.                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| Error       | An error is the incorrect output value of a failing component<br>or system, i.e., an incorrect state or an incorrect signal value. |

| Fault       | A fault is the "adjudged or hypothesized cause of an error".                                                                       |

| Fault Model | A fault model describes the effects of a fault on a component<br>or system at a certain abstraction level.                         |

#### Table 2.1: Terminology

Faults can be categorised into several fault classes, each representing a specific aspect of a fault. In Table 2.2 we review the fault classes that are relevant for this thesis. In general, any combination of fault classes in Table 2.2 are possible. In this thesis we focus on random faults that appear during the operational lifetime of a system, i.e., faults that are both operational and natural w.r.t. the fault classes. The examples provided in Table 2.2 reflect this focus. Development faults like bugs are, in general, out of scope but when they degrade the safety this degradation can be, for some cases, highlighted by our methods. In Sections 5.1 and 5.2 we present fault models for internal permanent and external transient faults, respectively.

Traditional analysis methods have a strong focus on *single faults*, i.e., they assume that during a considered time interval during system operation only a single fault occurs. However, due to shrinking transistor sizes and complexer transistors, the probability of faults has increased significantly, raising the need to consider *multiple faults*. We address this development by explaining how we inject multiple faults in our computational model and providing experimental data of fault analyses for multiple faults.

When the effects of a hardware fault manifest themselves as errors, in the digital domain they appear at first at the lowest digital abstraction level, i.e., the gate level. Like correct values, erroneous values are passed on to every successor in the fanout of the affected component allowing them to affect several other values. This is how errors can propagate through a digital circuit. During propagation, errors may become visible at higher abstraction levels and they may appear in the software after "crossing" the HW/SW boundary. Error propagation continues until all erroneous values are corrected or until they cannot propagate further, i.e., cannot affect more components.

Like faults, also errors can be categorised as shown in Table 2.3. In this thesis we consider both soft and hard errors. Some faults may not affect the behaviour of a component or system because the propagation of its errors to any primary output depends on a complex combination of internal state and input values. While in theory such complex combinations might be possible, in practice the application, e.g., the software running on a processor, could prevent the propagation of these errors to any primary output. In situations where a local analysis cannot provide formal guarantees that an error cannot have more effects on the system than found in the local analysis we also denote such errors as *latent errors*.

| Phase of occurrence | ce                                                                                                                                                                                                                                                |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Development fault   | Faults introduced into the system during development processes, for example by design engineer mistakes, bugs in tools or material impurities during production.                                                                                  |  |  |

| Operational fault   | Faults that occur after shipment when the system is in use.                                                                                                                                                                                       |  |  |

| Phenomenological    | cause                                                                                                                                                                                                                                             |  |  |

| Human-made fault    | Faults that result from human actions, like design mis-<br>takes or due to a wrongly operated system.                                                                                                                                             |  |  |

| Natural fault       | Faults that are "caused by natural phenomena without human participation" [8].                                                                                                                                                                    |  |  |

| System boundaries   | s                                                                                                                                                                                                                                                 |  |  |

| Internal fault      | Faults originating from mechanisms inside the system,<br>like electromigration, ageing or thermal processes due<br>to operational activity.                                                                                                       |  |  |

| External fault      | Faults originating from outside the system, like radia-<br>tion, unstable power supply or thermal processes due<br>to environmental temperature.                                                                                                  |  |  |

| Persistence         |                                                                                                                                                                                                                                                   |  |  |

| Permanent fault     | Faults that are always present, for example a short cir-<br>cuit of wire with the supply voltage.                                                                                                                                                 |  |  |

| Transient fault     | Faults that have only a temporary presence after which<br>the affected component returns to its fault-free opera-<br>tion. For example, value changes caused by a particle<br>strike.                                                             |  |  |

| Intermittent fault  | Transient faults and elusive permanent faults with an<br>unknown activation pattern are grouped together as in-<br>termittent faults. Typically, the presence of such faults<br>seems to be temporary, however, they reappear after<br>some time. |  |  |

|                     | Table 2.2: Fault Classes [8]                                                                                                                                                                                                                      |  |  |

In order to increase the fault resilience of embedded systems, i.e., to identify all faults that can cause the HW/SW system to fail, the fault effects on the system's behaviour have to be analysed such that appropriate measures can be taken. The state-of-the-art approach for such an analysis is to use fault models that describe fault behaviour as observed in the real-world, integrate them into a system model and analyse the behaviour of the fault injected system for single faults and multiple faults. Persistence of the causing fault

| Soft Error | Errors that are caused by intermittent or transient faults [8]. |

|------------|-----------------------------------------------------------------|

| Hard Error | Errors that are caused by permanent faults.                     |

| Protection      |                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| Detected Error  | An error is detected when a signal value, e.g., by a safety measure, indicates its presence [8].                             |

| Latent Error    | An error is latent when it is not (yet) detected [8].                                                                        |

| Corrected Error | An error is corrected when the error-free state is restored, e.g., due to logic masking or by an error-correcting algorithm. |

Table 2.3: Error Categories

#### 2.6.2 FAULT MODELS

Nowadays, a large number of fault models are in use [113]. In this section we focus on those models that are used by our methods during the experimental evaluation. We want to point out that an extension to support other fault models is straightforward and can be easily implemented.

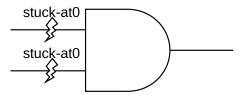

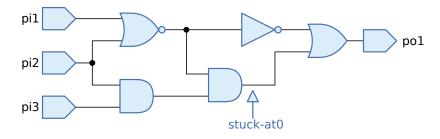

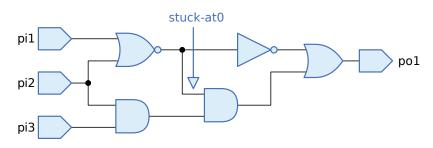

A permanent fault can occur when a physical connection between a component's output signal and the supply voltage or ground is created, e.g., by electromigration, causing the affected bit to be permanently set to the corresponding binary value. This fault behaviour is commonly modelled as a *stuck-at* fault which sets the value of a signal to either zero (stuck-at-o) or one (stuck-at-1).

As mentioned in Table 2.2, an example scenario for a transient fault is when an energetic particle strikes a transistor in such a way that it creates a temporary electrostatic charge that produces a current spike through the transistor. When such a particle strike changes the output value of a storage element like a register, it is called *single-event upset* (SEU). When a particle strike, instead, changes a value of the combinational part of a system, i.e., a signal value by affecting a transistor of a gate, it is called *single-event transient* (SET) [74] or *digital SET* (DSET) [39] when a demarcation between the digital and analog domain is desired. In this thesis we only consider digital signals and digital fault effects. The effect of an SEU or SET fault is modelled by using a *bitflip*, i.e., the corresponding binary value is changed to its opposite, and only the location of the bitflip determines the name of the event.